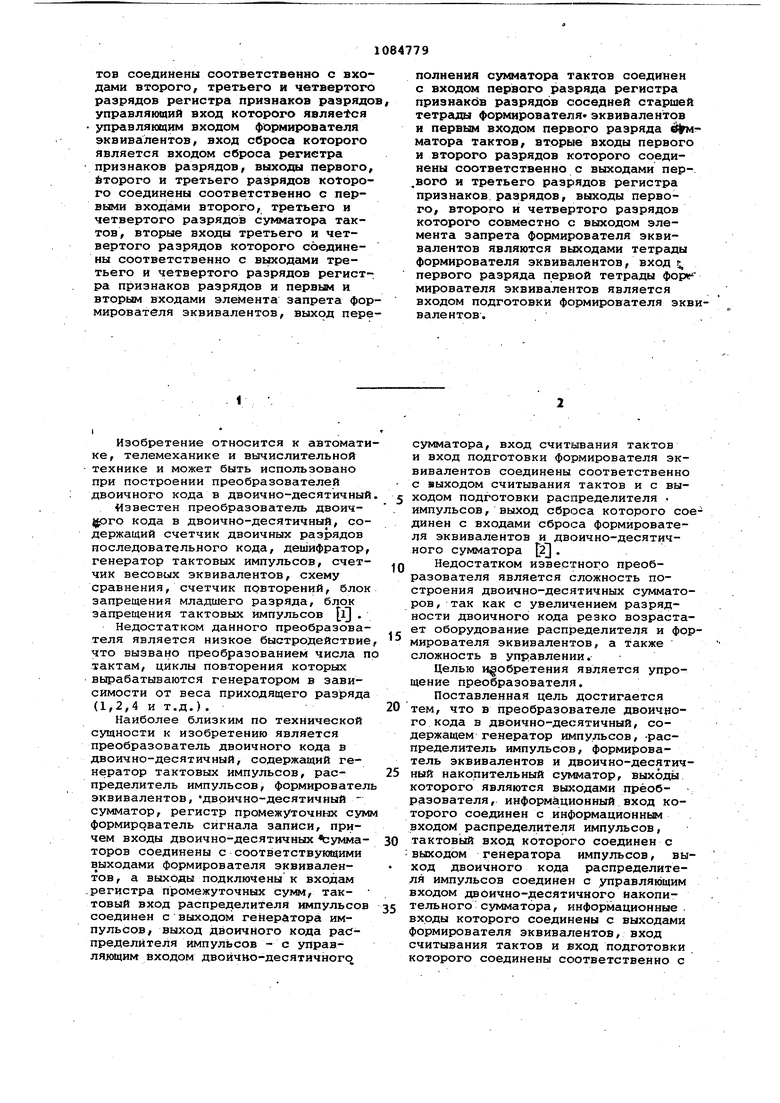

тон соединены соответственно с входами второго, третьего и четвертого разрядов регистра признаков разрядов управляющий вход которого являе ся управляющим входом формирователя эквивалентов, вход сброса которого является входом сброса регистра признаков разрядов, выходы первого, второго и третьего разрядов Kofopoго соединены соответственно с первыми входами второго, третьего и четвертого разрядов сумматора тактов, вторые входы третьего и четвертого разрядов которого соединены соответственно с выходгши третьего и четвертого разрядов регистра признаков разрядов и первым и вторым входами элемента запрета формирователя эквивалентов, выход переполнения сумматора тактов соединен с входом первого разряда регистра признакбв разрядов соседней старшей тетргщы формирователя эквивалентов и первым входом первого разряда Й матора тактов, вторые входы первого и второго разрядов которого соединены соответственно с выходами пер,вого и третьего разрядов регистра признаков, разрядов, выходы первого, второго и четвертого разрядов которого совместно с выходом элемента запрета формирователя эквивалентов являются выходами тетрады формирователя эквивалентов, вход ;, первого разряда первой тетрады мирователя эквивалентов является входом подготовки формирователя экввалентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1975 |

|

SU634267A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

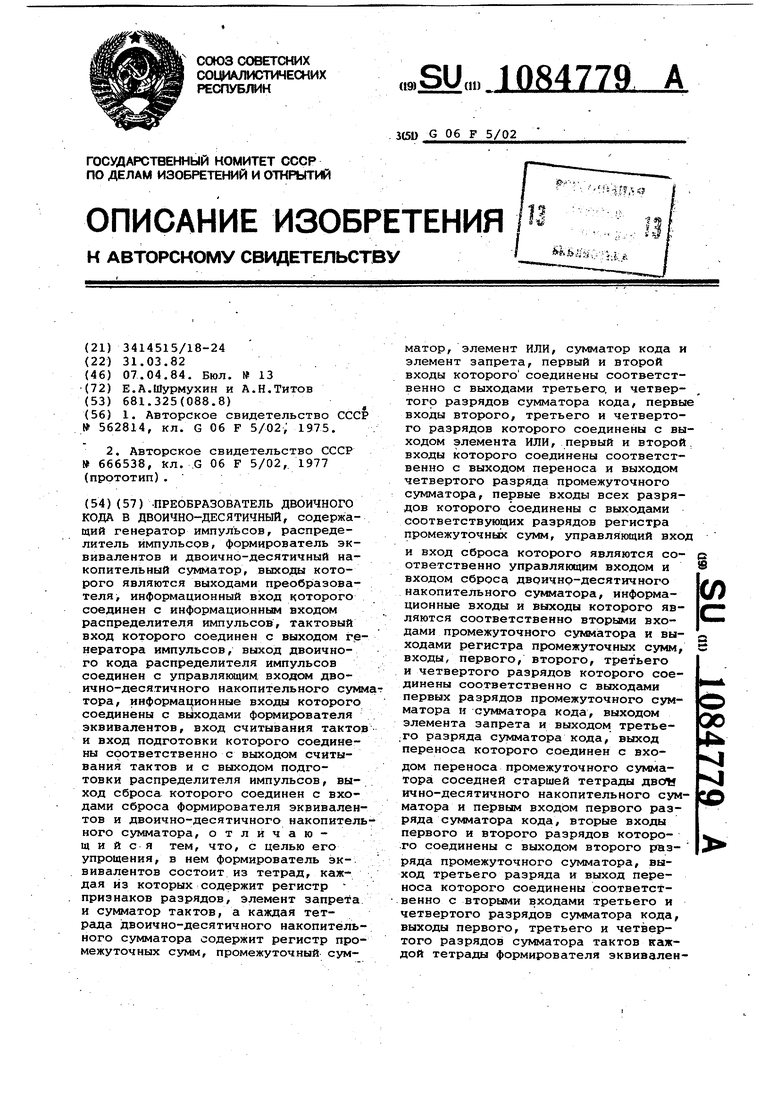

.ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий генератор импульсов, распределитель импульсов, формирователь эквивалентов и двоично-десятичный накопительный сумматор, выходы которого являются выходами преобразователя информационный вход которого соединен с информацио.нным входом распределителя импульсов, тактовый вход которого соединен с выходом г,енератора импульсов, выход двоичного кода распределителя импульсов соединен с управляющим входом двоично-десятичного накопительного суммаг тора, информационные входы которого соединены с выходами формирователя эквивалентов, вход считывания тактов и вход подготовки которого соединены соответственно с выходом считывания тактов и с выходом подготовки распределителя импульсов, выход сброса которого соединен с входами сброса формирователя эквивалентов и двоично-десятичного накопительного сумматора, отличающийся тем, что, с целью его упрощения, в нем формирователь эквивалентов состоит из тетрад, каждая из которых содержит регистр признаков разрядов, Элемент запрета и сумматор тактов, а каждая тетрада двоично-десятичного накопительного сумматора содержит регистр промежуточных сумм, промежуточный сумматор, элемент ИЛИ, сумматор кода и элемент запрета, первый и второй входы которого соединены соответственно с выходами третьего, и четвертого разрядов сумматора кода, первые входы второго, третьего и четвертого разрядов которого соединены с выходом элемента ИЛИ, первый и второй, входы которого соединены соответственно с выходом переноса и выходом четвертого разряда промежуточного сумматора, первые входы всех разрядов которого соединены с выходами соответствующих разрядов регистра промежуточный сумм, управляющий вход и вход сброса которого являются соответственно управляющим входом и входом сброса двоично-десятичного (Л накопительного сумматора, информационные входы и выходы которого являются соответственно вторыми входами промежуточного сумматора и выходами регистра промежуточных сумм, входы, первого, второго, третьего и четвертого разрядов которого соединены соответственно с выходами первых разрядов промежуточного сумматора и сумматора кода, выходом 00 элемента запрета и выходом третье4 .го разряда сумматора кода, выход переноса которого соединен с вхоЧ дом переноса промежуточного суммаVJ тора соседней старшей тетрады двои :о ично-десятичного накопительного сумматора и первым входом первого разряда сумматора кода, вторые входы первого и второго разрядов которого соединены с выходом второго р азряда промежуточного сумматора, выход третьего разряда и выход переноса которого соединены соответственно с вторыми входами третьего и четвертого разрядов сумматора кода, выходы первого, третьего и четвертого разрядов сумматора тактов каждой тетрады формирователя эквивален

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано при построении преобразователей двоичного кода в двоично-десятичный

известен преобразователь двоич| эго кода в двоично-десятичный, содержащий счетчик двоичных разрядов последовательного кода, дешифратор, генератор тактовых импульсов, счетчик весовых эквивалентов, схему сравнения, счетчик повторений, блок запрещения младшего разряда, блок запрещения тактовых импульсов lj .

Недостатком данного преобразователя является низкое быстродействие что вызвано преобразованием числа п .тактам, циклы повторения которых вырабатываются генератором в зависимости от веса приходящего разряда (1,2,4 и т.д.).

Наиболее близким по технической сущности к изобретению является преобразователь двоичного кода в двоично-десятичный, содержащий генератор тактовых импульсов, распределитель импульсов, формировател эквивалентов, двоично-десятичный сумматор, регистр промежуточных сум формирователь сигнала записи, причем входы двоично-десятичных Ьумматоров соединены с соответствукичими выходами формирователя эквивалентов, а выходы подключены к входам .регистра промежуточных сумм, тактовый вход распределителя импульсов соединен с выходом генератора импульсов, выход двоичного кода распределителя импульсов - с управляющим входом двoйчвo-дecятичнoгq

сумматора, вход считывания тактов и вход подготовки формирователя эквивалентов соединены соответственно с выходом считывания тактов и с вы5 ходом подготовки распределителя импульсов, выход сброса которого соединен с входами сброса формирователя эквивалентов и двоично-десятичного сумматора 2 . Q Недостатком известного преобразователя является сложность построения двоично-десятичных сумматоров , так как с увеличением разрядности двоичного кода резко возрастает оборудование распределителя и формирователя эквивалентов, а также сложность в управлении.

Целью изобретения является упрощение преобразователя.

Поставленная цель достигается

0 тем, что в преобразователе двоичного кода в двоично-десятичный, содержащем генератор импульсов, -распределитель импульсов, формирователь эквивалентов и двоично-десятич5 ный накопительный сумматор, выходы, которого являются вы :одами преобразователя, информационный вход которого соединен с информационным входом распределителя импульсов,

0 тактовый вход которого соединен с : выходом генератора импульсов, выход двоичного кода распределителя импульсов соединен с управляющим входом двоично-десятичного накопи5 тельного - сумматора, информационныевходы которого соединены с выходами формирователя эквивалентов, вход считывания тактов и вход подготовки которого соединены соответственно с

выходом считывания тактов и с выходом подготовки распределителя импульсов, выход сброса которого соединен с входами сброса формирователя эквивалентов.и двоично-десятичного накопительного сумматора, формирователь эквивалентов состоит из тетрад, каждая из которых содержит регистр признаков разрядов, элемент запрета и сумматор тактов, а каждая тетрада двоично-десятичного накопительного сумматора содержит регистр промежуточных сумм, промежуточный сумматор, элемент ИЛИ сумматор кода и элемент запрета, первый и второй входы которого соединены соответственно с выходами третьего и четвертого разрядов.сумматора кода, первые входы второго, третьего и четвертого разрядов которого соединены с выходом элемента ИЛИ, первый и вторбй входы которого соединены соответственной с выходом переноса и выходом четвертого разряда промежуточного сумматора, первые входы всех разрядов которого соединены с выходами соответствующих разрядов регистра промежуточных сумм, управлякадий вход и вход сброса которого являются соответственно управляющим входом сброса двоично-десятичного накопительного сумматора, информационные входы и выходы которого являются соответственно вторыми входами промежуточного сумматора и выходами регистра промежуточных сумм, входы первого, второго, третьего и четвертого разрядов которого соединены соответственно с выходами первых разрядов промежуточного сумматора, и сумматора кода, выходом элемента запрета и выходом третьего разряда сумматора кода, выход переноса которого соединен с входом переноса промежуточного сумматора соседней старшей тетрады двоично-десятичного накопительного сумматора и первым входом первого разряда сумматора кода, вторые входы первого и второго разрядов которого соединены с выходом второго разряда промежуточного сумматора, выход третьего разряда и выход переноса которого соединены соответственно с вторыми входами третьего и четвертого разрядов сумматора кода, выходы первого, третьего и четвертого разрядов сумматора тактов каждой тетрады формирователя эквивалентов соединены соответственно с входами второго, третьего и четвертого разрядов регистра признаков разрядов, управляющий вход которого является управляющим входом формирователя -эквивалентов, вход сброса которого является входом сброса регистра признаков разрядов,выходы первого,второго и третьего разрядов которого соединены соответственно с первыми входами второго,третьего и четвёртого разрядов сумматора тактов,вторые вхцы третьего и четвертого разрядов которого соединены соответственно с выходами третьего и четвертого разрядов регистра призна.ков разрядов и лервым и вторым входшми элемента запрета формирователя эквивалентов, выход переполнения сумматора тактов соединен с входом первого разряда регистра признаков соседней старшей тетрады формирователя эквивалентов и первым входом первого разряда сумматора тактов, вторые входы первого и второго разрядов которого соединены соответственно с выходами первого и третьего разрядо выходы первого, второго и четвертого разрядов которого совместно с выходом элемента запрета формирователя эквивалентов являются выходами тетрады формирователя эквивалентов, вход первого разряда первой тетрады формирователя эквивалентов является входом подготовки формирователя эквивалентов .

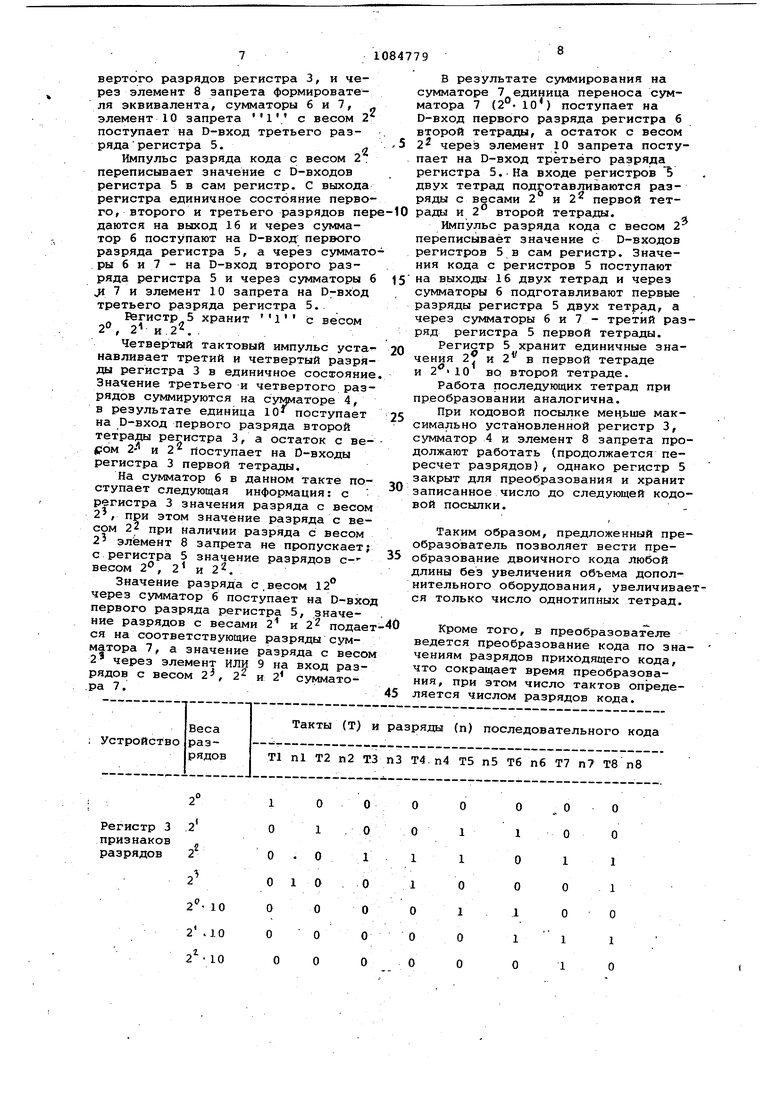

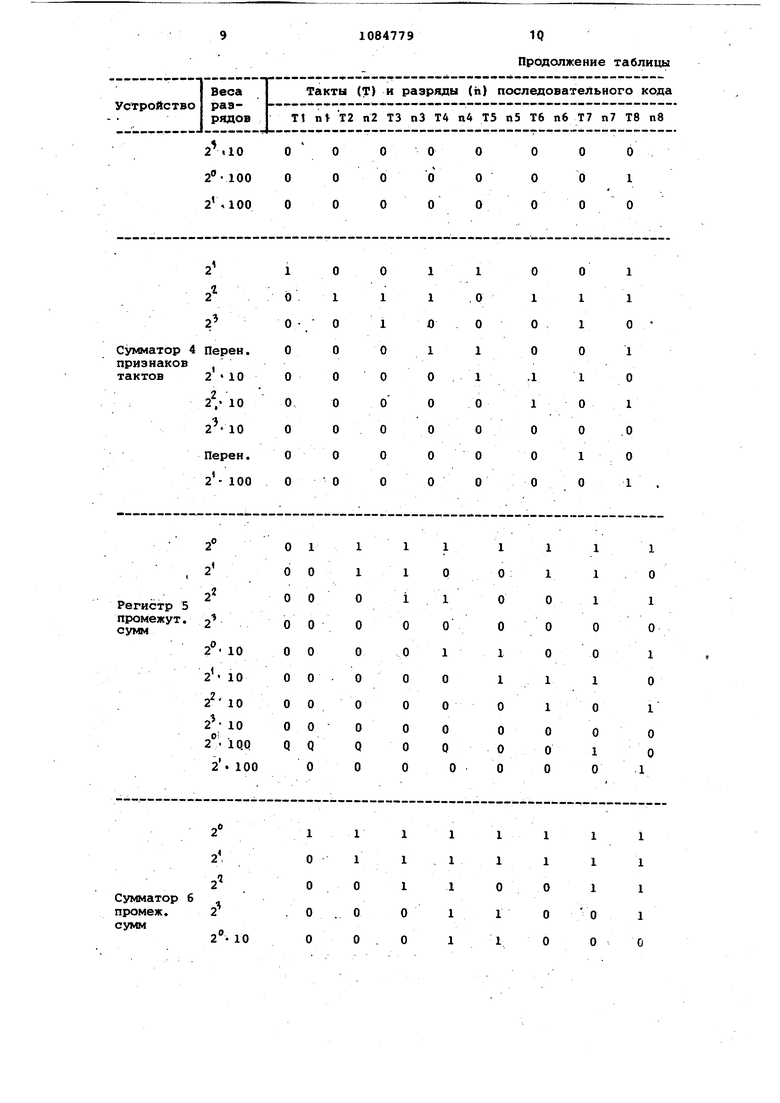

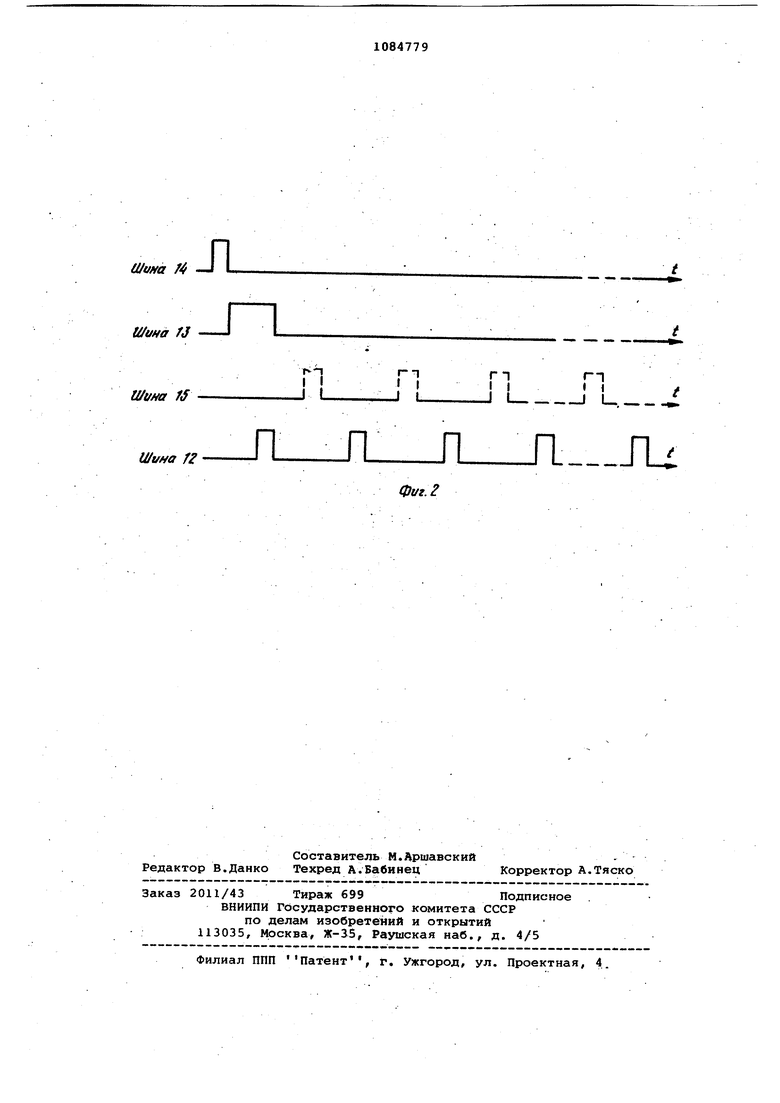

На фиг.1 приведена структурная схема предложенного преобразователя на фиг.2 - временные соотношения кодовой посылки и сигналов управления.

Преобразователь двоичного кода в двоично-десятичный содержит генератор 1 импульсов, распределитель 2 импульсов, регистр 3 признаков разрядов, сумматор 4 тактов, регистр 5 промежуточных сумм промежуточный сумматор б, сумматор 7 кода, элемент 8 запрета формирователя эквивалентов, предназначенный для запрещения разряда весом 2 при одновременном наличии на втором входе разряда 2, элемент ИЛИ 9, который предназначен для сбора разряда 2 и сигнала переполнения промежуточного сумматора б, и элемент 10 запрета.

Регистр 3 признаков разрядов преназначен для хранения текущего значения двоичного разряда в виде двоично-десятичного эквивалента.

Регистр 3, сумматор 4 и элемент 8 запрета служит для преобразования текущего значения двоичного разряда в двоично-десятичный эквивалент. .

гРЕгистр 5 промежуточных сумм предназначен для хранения суммы значений разрядов двоичного кода в йиде двоично-десятичных эквивалентов.

Промежуточный сумматор 6 представляет собой двоичный сумматор и предназначен для суммирования текущего двоично-десятичного значения разряда кода с суммарным значением ранее поступивших разрядов кода. Сумматор 7 представляет собой двоичный декадный сумматор и обеспечивает, совместно с промежуточнь регистром 5, промежуточным суммато ром б, элементами ИЛИ 9 и запрета формирование двоично-десятичного э вивалента двоичного кода. Входная информация в виде посылок последовательного кода подается на информационный вход 11 преоб разователя. Распределитель 2 импульсов выдает четыре сигнала, временные соо ношения которых представлены на фиг.2: по выходу 12 импульсы считы вания тактов (тактовые импульсы на время кодовой посылки), по выходу импульс подготовки D-входа первого разряда регистра 3 (импульс начала кодовой посылки) ; по выходу. 14 импульс установки в О регистров и 5; по выходу 15 импульсы двоично кода (кодовая посылка). I. Результат преобразования формируется на выходах 16. Регистр 3 признаков разрядов, сумматор 4 так тов и элемент 8 Запрета в соовокуп ности образуют тетраду формировате ля 17 эквивалентов. Регистр 5 Промежуточных сумм, промежуточный сумматор 6, сумматор кода, элементы ИЛИ 9 и запрета 10 в совокупности образуют тетраду дв 1 но-десятичног6 накопительного сум матора 18 i Преобразователь двоичного кода в двоично-десятичный работает следующим образом. На вход распределителя 2 импульсов поступают тактовые импульсы генератора 1 импульсов и кодовые по сылки на вход 11 (младшими разрядам вперед, причем одна посылка может содержать несколько кодов, подлежащих преобразованию). Сигнал установки в О регистров 3 и 5 подготавливает преоб разователь к приему информации. Иипульс тактовой частоты в момент наличия на информационном D-входе первого разряда регистра 3 импульса начала кодовой посылки записывает в регистр 3 единицу, что соответствует значению разряда с весом 2° . Следующим тактовым импульсом значение в регистре 3 удваивается. При значении в регистре чисел больше 8 сумматором 4 производится коррекция значений чисел а регистрах 3 и перенос числа 2. 10 тетраду п+1, где п - номер тетрады Значение текущего разряда в двоично-десятичном эквиваленте, формированное формирователем 17 эквивалента, суммируется сумматорами 6 с ранее прошедшими разрядами, храня(римися В регистрах 5. Суммарное значение с сумматоров б поступает через сумматор 7 кода на информационные входы регистра 5. Сумматор 7 преобразует числа от О до 18 в дярично-десятичный эквивалент. Сигнал переноса 2, Ю с сумматора 7 поступает на информационный вход 1-го разряда сумматора б тетрады п+1. ёапись информации в регистр 5 производится импульсом соответствующего разряда входного двоичного кода, при отсутствии во входном -коде разряда запись в регистр 5 не производится.; В таблице истинности указана j бота преобразователя в зависимости от приходящего такта (Т) (признака текущего разряда) и разряда кодовой посылки /п,/, где i - текущий номер разряда. Рассмотрим подробнее работу преобразователя для двоичного кода 11111 на примере Двух .тетрад - принцип преобразования распространяется на двоичный последовательный код любой длины, поступающий младшими разрядами вперед. Первым тактовым импульсом с выхода 12 первый разряд регистра 3 с весом 2 устана(вливается в единичное состояние Ч и поступает через сумматор 4.на D-вход второго разряда с весом 2 регистра 3 и через сумматор б на D-вход первого разряда с весом 2° регистре 5. Импульс разряда кода с весом 2 поступает по выходу 15 и переписывает значение с D-входа в регистр 5. С выхода регистра.единичное состояние первого разряда поступает на выход 16 и через сумматор б на D-вход первого разряда регистра 5. Шгистр 5 хранит с весом 2 По второму тактовому импульсу второй разряд регистра 3 с весом 2 устанавливается в Ч,состояние с выхода второго разряда подается через сумматор 4 на D-вход третьегб разряда регистра 3 и через сумматоры б и 7 на D-вход второго разряда регистра 5. Импульс разряда кода с весом 2 переписывает значение с D-входов регистра 5 в сам регистр. С выходарегистра 5 единичное состояние первого и второго разрядов подаетсяна выход 16 и через сумматор б на D-.вход первого разряда регистра 5, а через сумматоры б и 7 - на D-вход второго разряда регистра 5. Регистр 5 хранит i с весом 2 u2. По третьему тактовому импульсу „ третий разряд регистра 3 с весом 2 устанавливается в единичное состояние, и его значение через сумматор 4 поступает на D-вхбды третьего и четвертого разрядов регистра 3, и через элемент 8 запрета формирователя эквивалента, сумматоры 6 и 7, „ элемент 10 запрета с весом 2 поступает на D-вход третьего разрядарегистра 5.2 Импульс разряда кода с весом 2. переписывает значение с D-входов регистра 5 в сам регистр. С вьохода регистра единичное состояние первого, второго и третьего разрядов пер даются на выход 16 и через сумматор б поступают на D-вход первого разряда регистра 5, а через суммато ры 6 и 7 - на D-вход второго разряда регистра 5 и через сумматоры ji 7 и элемент 10 запрета на D-вхЬд третьего разряда регистра 5. 1 гистр 5 хранит с весом 2, 2 и 2 Четвертый тактовый импульс уста навливает третий и четвертый разря ды регистра 3 в единичное состояние Значение третьего И четвертого разрядов суммируются на сумматоре 4, в результате единица 10 поступает на D-вход первого разряда второй тетрады регистра 3, а остаток с ве(ром 2- и 2 поступает на D-входы регистра 3 первой тетрады. На сумматор 6 в данном такте поступает следующая информация: с регистра 3 значения разряда с весом 2, при этом значение разряда с весом 22 при наличии разряда с весом 2 элемент 8 запрета не пропускает; с регистра 5 значение разрядов свесом 2°, 2 и 2 2. Значение разряда с.весом 12° через сумматор б поступает на D-вхо первого разряда регистра 5, значение разрядов с весами 2 и 2 подае ся на соответствующие разряды сумматора 7, а значение разряда с весо 2 через элемент ИЛИ 9 на вход разрядов с весом 2, 2 и 2 сумматора 7.

Регистр 3 2 признаков разрядов 2

2°- 10

о 1 о о 1 1 о

о о 1 о о 1 1

о о 1

1 о 1 о В результате суммирования на сумматоре 7 единица переноса сумматора 7 (2°. 10) поступает на D-вход первого разряда регистра б второй тетрады, а остаток с весом 2 через элемент 10 запрета поступает на D-вход третьего разряда регистра 5. На входе регистрО1В 5 двух тетрад подготавливаются разряды с весами 2 и 2 первой тетрады и 2° второй тетрады. Импульс разряда кода с весом 2 переписывает значение с D-входов регистров 5 в сам регистр. Значения кода с регистров 5 поступают на выходы 16 двух тетрад и через сумматоры б подготавливают первые разряды регистра 5 двух тетрад, а через сумматоры 6 и 7 - третий разряд регистра 5 первой тетрады. Регистр 5 хранит единичные значения 2 и 2 в первой тетраде и 10 во второй тетраде. Работа последующих тетрад при преобразовании аналогична. При кодовой посылке меньше максимально установленной регистр 3, сумматор 4 и элемент 8 запрета продолжают работать (продолжается пересчет разрядов), однако регистр 5 закрыт для преобразования и хранит записанное число до следующей кодовой посылки. Таким образом, предложенный преобразователь позволяет вести преобразование двоичного кода любой длины без увеличения объема дополнительного оборудования, увеличивается только число однотипных тетрад. Кроме того, в преобразователе ведется преобразование кода по значениям разрядов приходящего кода, что сокращает время преобразования, при этом число тактов определяется числом разрядов кода.

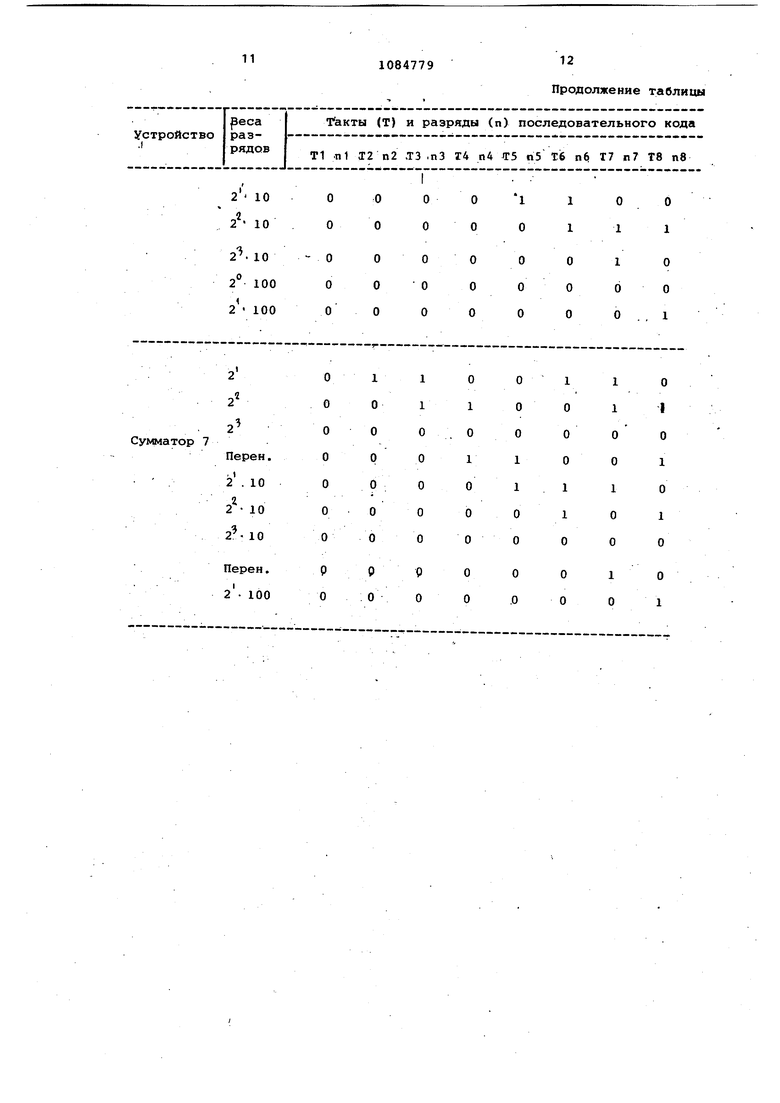

Продолжение таблицы

Продолжение таблицы

гг

м

/J

W

//О(f

j j

д

ф

N/./

FFJ

I U IJ у1 Г

:z

Jf

;

2

Ф

L

г,2,1г

Х. . л . 1; /4/M/4f

У У

г ф у | ф ф

а

.

Г

г/ I

.

Ч

77

п

,г 4 W у

J

/ч/ 1/П

23

гГфффф фффф ф ф -HJT IjLIjSL, ЩШ.

/

S/ .Л Шина /4 -I I

и/ина fJ

Шина // п п п Шина fZ Фиг.2 ,--i л п

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 562814, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU666538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-03-31—Подача