рой группы которого соединен с первым входом второй группы второго элемента И-ИЛИ узла запуска и с первыми входами первых групп элементов И-ИЛИ группы, вторые входы первых групп и первые входы вторых групп которых соединены с выходами разрядов регистра сдвига с первыми входами первых групп

вход второго элемента ИЛИ которого соединен с первым входом второй группы первого элемента И-ИЛИ узла запуска и с входом разрешения занесения данных устройства, выход окончания сдвигов которого соединен со вторым входом второй группы третьего элемента И-ИЛИ узла запуска и с выходом

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

Устройство содержит регистр исходных данных, два счетчика, группу мультиплексоров, элемент И - ИЛИ, дешифратор, регистр сдвига и узел запуска, содержащий четыре триггера, первый элемент НЕ, два элемента И - ИЛИ и три элемента И. Устройство дополнительно содержит коммутатор, элемент задержки, триггер, группу элементов И - ИЛИ, узел стробирующих сигналов и режимов, содержащий шесть элементов ИЛИ, три элемента И и два элемента задержки, узел анализа переполнения, содержащий две схемы сравнения, элемент И - ИЛИ, элемент И и триггер, узел компоновки сдвиговых регистров, содержащий группу элементов И, группу элементов И - ИЛИ, элемент НЕ, элемент НЕ, элемент И и источник логического нуля, а узел запуска дополнительно содержит третий элемент И - ИЛИ, второй и третий элементы НЕ.

элементов И-ИЛИ группы узла компонов- ю элемента И-ИЛИ, третий вход первой

ки сдвиговых регистров и с первыми входами элементов И группы узла компоновки сдвиговых регистров, с первыми входами первой и второй схем сравнения узла анализа переполнения, информационный вход устройства и вход разрешения занесения данных устройства соединены соответственно с информационным входом и входом разрешения приема триггера, выход которого со- единен с первым входом элемента И узла компоновки сдвиговых регистров и со вторыми входами первой и второй схем сравнения узла анализа переполнения, нулевой вход триггера которо- го ки,

полнения является выходом переполнения устройства, информационный выход

соединен с входом элемента задерж- 1, выход триггера узла анализа перекоторого соединен с выходами элемен- 30 первого и второго счетчиков, первый

тов И-ИЛИ группы, второй вход элемента И узла анализа переполнения соеди нен с вторым выходом дешифратора, третий и четвертый выходы которого соединены соответственно со вторым входом первого элемента ИЛИ и с первым входом второго элемента И1М узла стро- бируюш;их сигналов и режимов, третий вход первого элемента ИЛИ которого соединен с вторыми входами второй группы элементов И-ИЛИ группы, с управляющим входом коммутатора, с первым входом второй группы элемента И-ИЛИ, с первыми входами первой и

второй группы, третьего элемента И-ИЛИ, рым входом первой группы третьего

50

узла запуска и с пятым выходом дешифратора, шестой выход которого соединен с вторым входом элемента И узла компоновки сдвиговых регистров, выходы элемента И, элементов И-ИЛИ группы, элементов И группы и источника логического нуля которого соединены с информационным входом регистра сдвига, тактовый вход, первый и второй входы задания режима которого сг соединены соответственно с выходами третьего элемента ИЛИ, первого и второго элементов задержки узла стробирующих сигналов и режимов, второй

элемента И-ИЛИ, с вторым входом в рой группы второго элемента И-ИЛИ с первым входом второй группы перв го элемента И-ШШ, выход которого единен с входом разрешения приема вого триггера, выход которого соед нен с третьим входом первой группы

Первого элемента И-ИЛИ и с первым входом второго элемента И, выход к торого соединен с единичным входом второго триггера, вход разрешения приема которого соединен с вы ходом перврго элемента И и с входом трет ей группы второго элемента И-ИЛИ,

группы и второй вход второй группы которого объединены и подключены к выходу первого счетчика и к второму входу первой группы первого элемента И-ИЛИ узла запуска, выход первого триггера которого соединен с первым входом третьего элемента И узла стро- бирующих сигналов и режимов, с входом элемента НЕ узла компоновки сдвиговых регистров и с первым входом первой группы элемента И-ИЛИ узла анализа переполнения, первый вход второй группы которого соединен с выходом третьего триггера узла запуска и с вторым входом первого элемента И уз ла стробирующих сигналов и режимов, выходы четвертого элемента ИЛИ и первого элемента И которого соединены соответственно со счетными входами

5

0

и второй управляющие входы мультиплексоров группы соединены соответственно с выходами пятого и шестого элементов ИЛИ узла стробирующих сиг- налов и режимов, первые входы которых объединены и подключены к второму входу второй группы первого элемента И-ИЛИ узла запуска, причем в узле запуска выход первого элемента НЕ соединен с третьим входом второй группы третьего элемента И-ИЛИ, выход которого соединен с входом разрешения приема четвертого триггера, информационный вход которого соединен с вто0

г

элемента И-ИЛИ, с вторым входом второй группы второго элемента И-ИЛИ и с первым входом второй группы первого элемента И-ШШ, выход которого соединен с входом разрешения приема первого триггера, выход которого соединен с третьим входом первой группы

Первого элемента И-ИЛИ и с первым входом второго элемента И, выход которого соединен с единичным входом второго триггера, вход разрешения приема которого соединен с вы ходом перврго элемента И и с входом третьей группы второго элемента И-ИЛИ,

третий вход первой группы которого соединен с выходом третьего триггера, информационный вход которого через второй элемент НЕ соединен со вторым входом первой группы.второго элемента И-ИЛИ, третий вход второй группы которого .соединен со вторым входом второго элемента И, с вторым входом первой группы первого элемента И-ИЛИ, с информационным входом второго триггера и с входом третьего элемента НЕ, выход которого соединен с информационным входом первого триггера и с первым входом третьего эле- мента И, выход и второй вход которого соединены соответственно с вторым входом второй группы первого элемента И-ИЛИ и с первым входом второй группы второго элемента И-ИЛИ, вход первого элемента НЕ соединен со вторым входом первого элемента И, приче в узле стробирующих сигналов и режим

третий вход которого соединен с выходом первого элемента И, первый вход которого соединен с вторыми входами второго и третьего элементов И, выход второго элемента И соединен с первым входом четвертого элемента ИЛИ и с четвертым входом третьего элемен а ИЛИ, пятый вход которого соединен с вторым входом четвертого элемента ИЛИ и с выходом третьего элемента И, выходы первого и второго элементов ИЛИ соединены соответственно с входами первого и второго элементов эадержки, причем в узле анализа переполнения выходы первой и второй схем сравнения соединены соответственно с вторыми входами второй и первой групп элемента И-ИЛИ, выход которого соединен с 20 третьим входом элемента И, выход которого соединен с единичным входом триггера, причем в узле компоновки сдиго- вых регистров выход элемента КЕ соединен с вторыми входами первой группы

первый вход первого элемента ИЛИ соединен с третьим входом второго эле- 25элементов И-ИЛИ группы, с вторыми вхо- мента ИЛИ, с первым входом третьегодами элементов И группы, первый вход элемента ИЛИ и со вторым входом пято-элемента И соединен с первыми входа- го элемента ИЛИ, третий вход первогоми второй группы элементов И-ИЛИ элемента ИЛИ соединен с вторым входомгруппы,-вторые входы второй группы шестого элемента ИЛИ, второй вход вто-зокоторых соединены со входом элемен- рого элемента ИЛИ соединен с четвер-та НЕ, второй вход элемента И соеди- тым входом первого элемента ИЛИ и снен с третьими входами первой и вто- вторым входом третьего элемента ИЛИ,рой группы элементов И-ИЛИ группы.

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах электронных вычислительных машин средней производительности.

Цель изобретения - повьшение быстродействия .

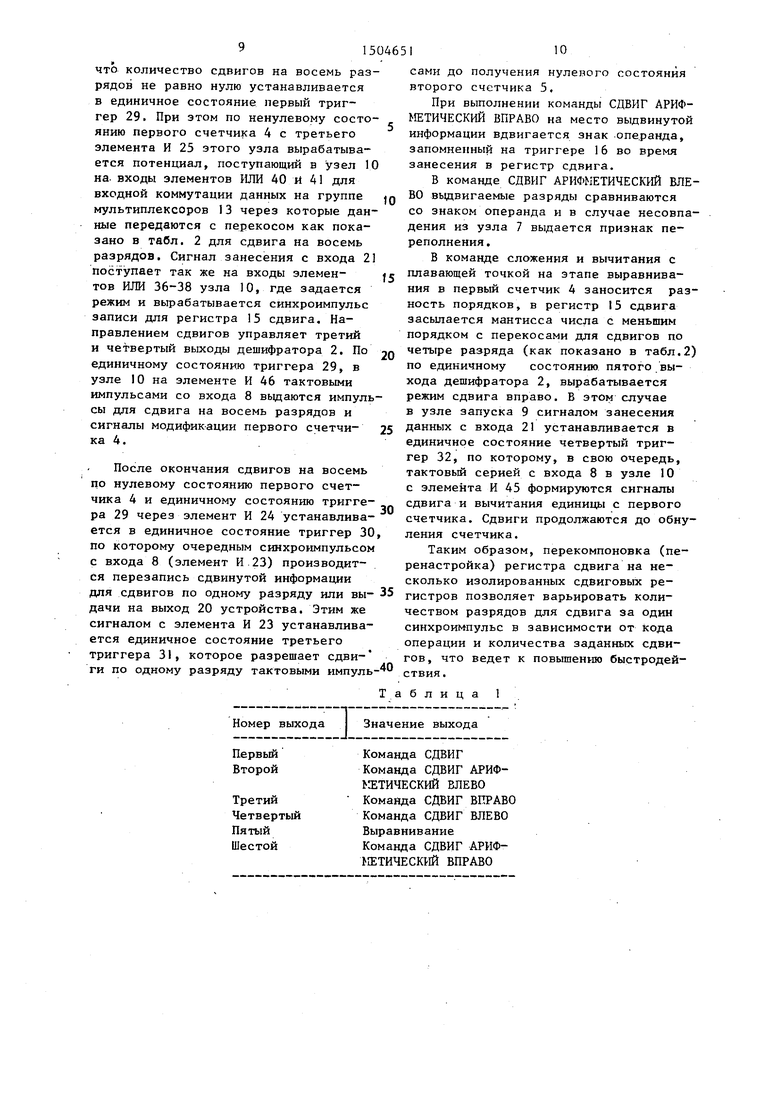

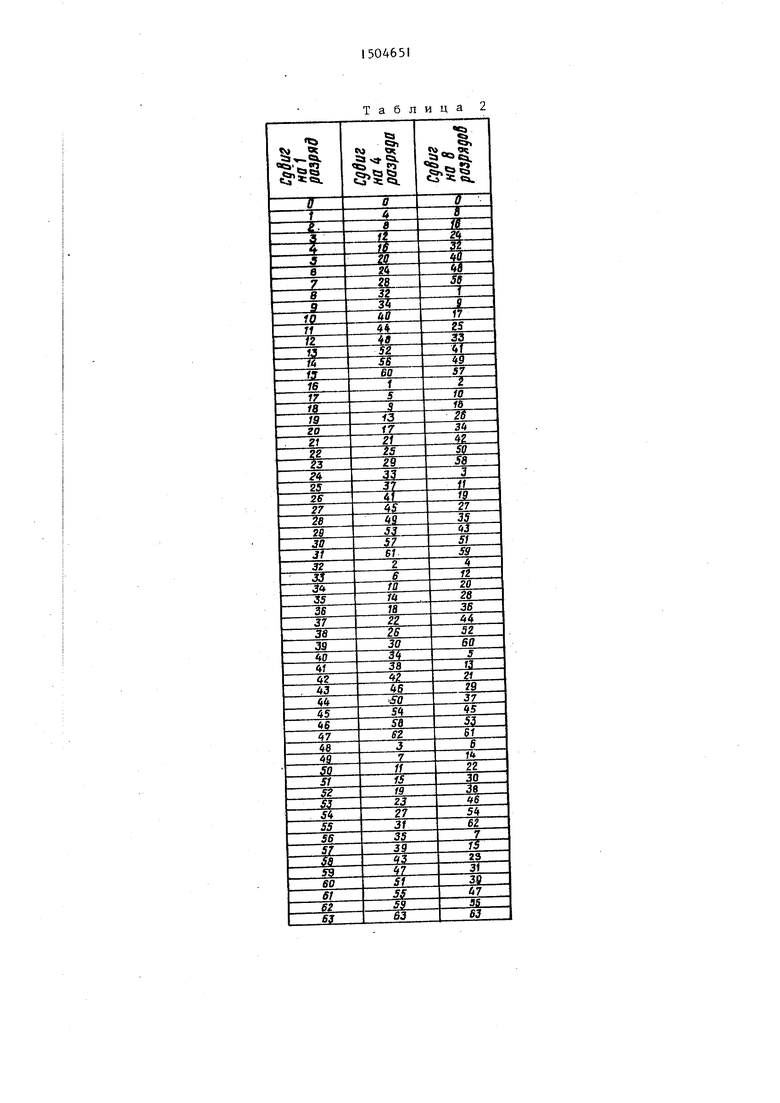

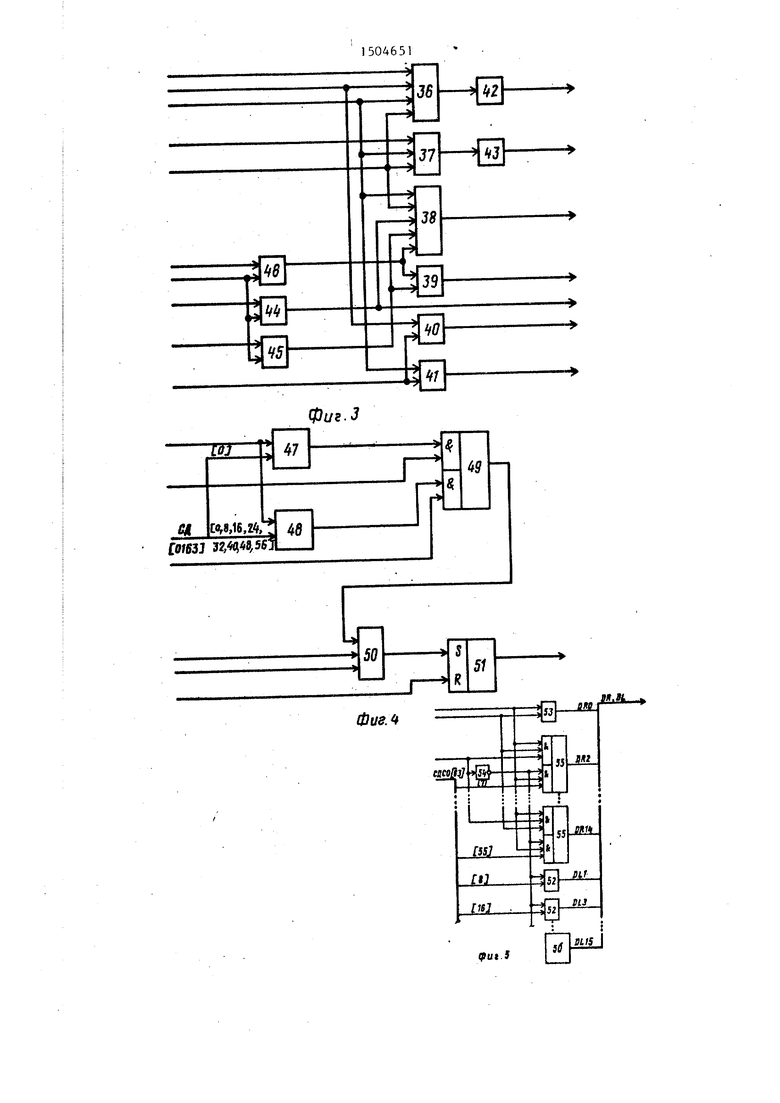

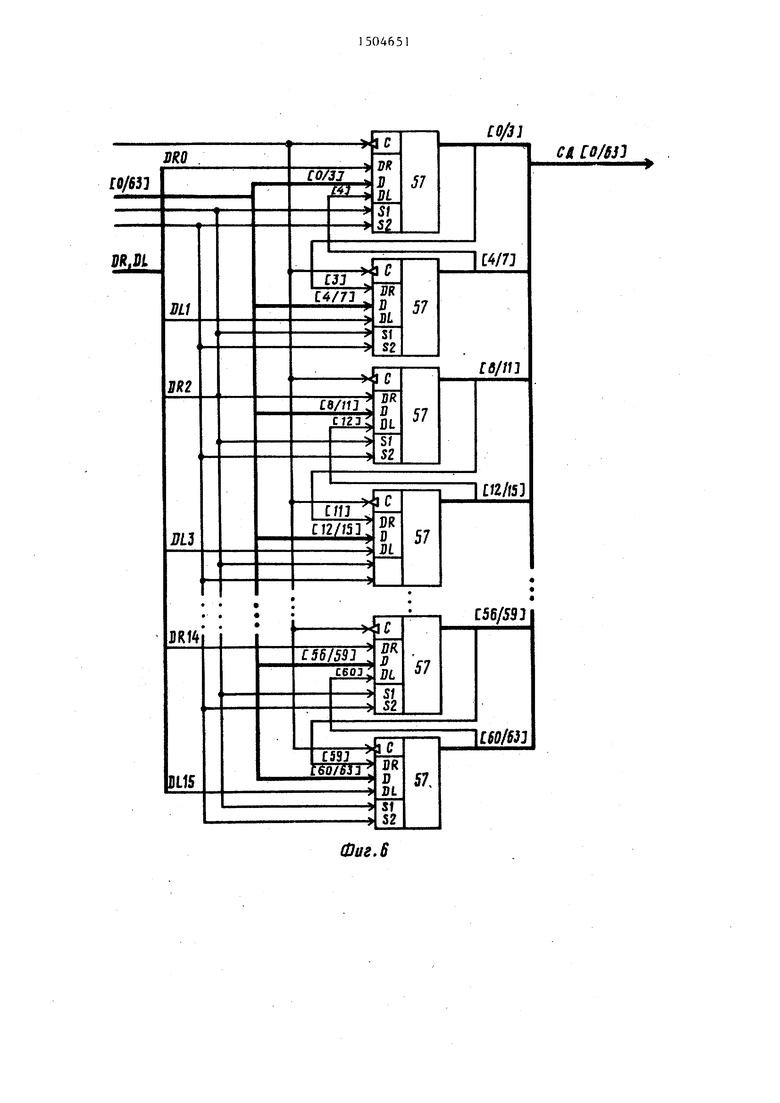

На фиг. 1 изображена схема устройства для сдвига; на фиг. 2 - схема узла запуска; на фиг. 3 - схема узла стробирующих сигналов и режимов; на фиг. 4 - схема узла анализа переполнения; на фиг. 5 - схема узла компоновки сдвиговых регистров; на фиг. 6- схема регистра сдвига; на фиг. 7 - временная диаграмма работы сдвигате- ля при выполнении команд сдвигов.

Сдвигатель (фиг. 1) содержит регистр 1 исходных данных, дешифратор 2, коммутатор 3, первый и второй счетчики 4 и 5, элемент 6 задержки, узел 7 анализа переполнения, тактовьй

третий вход которого соединен с выходом первого элемента И, первый вход которого соединен с вторыми входами второго и третьего элементов И, выход второго элемента И соединен с первым входом четвертого элемента ИЛИ и с четвертым входом третьего элемен а ИЛИ, пятый вход которого соединен с вторым входом четвертого элемента ИЛИ и с выходом третьего элемента И, выходы первого и второго элементов ИЛИ соединены соответственно с входами первого и второго элементов эадержки, причем в узле анализа переполнения выходы первой и второй схем сравнения соединены соответственно с вторыми входами второй и первой групп элемента И-ИЛИ, выход которого соединен с третьим входом элемента И, выход которого соединен с единичным входом триггера, причем в узле компоновки сдиго- вых регистров выход элемента КЕ соединен с вторыми входами первой группы

элементов И-ИЛИ группы, с вторыми вхо- дами элементов И группы, первый вход элемента И соединен с первыми входа- ми второй группы элементов И-ИЛИ группы,-вторые входы второй группы которых соединены со входом элемен- та НЕ, второй вход элемента И соеди- нен с третьими входами первой и вто- рой группы элементов И-ИЛИ группы.

вход 8 устройства, узел 9 запуска, узел 10 стробирующих сигналов и режимов, элемент И-ИЛИ 11, группу элементов И-ИЛИ 12, группу мультиплексоров 13, узел 14 компоновки сдвиговых регистров, регистр 15 сдвига, триггер 16, информационный вход 17 устройства, вход 18 разрешения занесения команды устройства, выход 19 переполнения устройства, информационный выход 20 устройства, вход 21 разрешения занесения данных устройства, выход 22

окончания сдвигов устройства.

Узел 9 запуска (фиг. 2) содержит элементы И 23, 24, 25 с первого по третий соответственно, элементы И- ИЛИ 26, 27, 28 с первого по третий соответственно, триггеры 29-32 с первого по четвертый соответственно, элементы НЕ 33-35 с первого по третий соответственно.

В узле 9 запуска триггеры 29-32 являются двухтактными.

Узел 10 .стробирующих сигналов и режимов (фиг. 3) содержит элементы ИЛИ 36-41 с первого по шестой соответственно, первый и второй элементы 42 и 43 задержки, элементы И 44- 46 с первого по третий соответственно

Узел 7 анализа переполнения (фиг.4 содержит первую и вторую схемы 47 и 48 сравнения, элементы И-ИЛИ 49, элемент И 50 и триггер 51. .

Узел 14 компоновки сдвиговых ре-- гистров (фиг. 5) содержат группу эле- ментов И 52, элемент И 53, элемент НЕ 54, группу элементов И-ИЛИ 55, источник 56 логического нуля.

Регистр 15 сдвига (фиг. 6) содержит группу элементов 57 сдвига.

Узел 9 запуска служит для выработки потенциалов разрядности сдвигов по запускающим воздействиям.

Узел 10 стробирующих сигналов и режимов служит для формирования сигна лов приема и сдвига информации в регистре сдвига, а также сигналов вычитания единицы из содержимого счетчиков для подсчета количества сдвигов..

Узел 7 анализа переполнения служит для установки признака переполнения.

Узел 14 компоновки сдвиговых регистров служит для выработки сигналов последовательного ввода информации в регистр сдвига DR при сдвигах вправо и DL при сдвигах влево.

Устройство для сдвига работает следующим образом.

Перед началом сдвигов со входа 17 устройства в регистр 1 исходных данных сигналом с входа 18 устройства засылается код команды и количество сдвигов. Последние через задержку на элементе 6 сигналом занесения пересылаются в счетчики 4 и 5 через коммутатор 3 в зависимости,от принятого кода команды (выравнивание или команда сдвигов). При этом содержимое командной части регистра 1 исходных лданных подается на дешифратор 2, где вырабатываются управляющие признаки, которые подготавливают сдвигатель для работы в определенном режиме.В табл. 1 приведены значения выходов дешифратора.

П 6 типу команды и величине сдвигов группа мультиплексоров 13 настраивается на прием информации в зависи

0

0

5 Q

5

5

0

мости от вида сдвига. Организуются сдвиги на восемь, один и четыре разряда. Причем сдвиги на четыре разряда используются отдельно, а сдвиги на восемь и один разряд могут использоваться совместно, т.е. информация на регистре 15 сдвига сначала сдвигается по восьми, а затем - по одному разряду, в зависимости от заданного количества сдвигов.

Чтобы организовать сдвиги более чем на один разряд за один синхроимпульс, регистр 15 сдвига, собранный на четырехразрядных элементах 57 сдвига, способных сдвигать за один импульс только на один разряд влево или вправо, условно разбивается на несколько сдвиговых регистров. Для организации сдвигов на четыре 64-разрядный регистр 15 сдвига разбивается на четыре регистра по шестнадцати разрядов каждый. Для организации сдвигав на восемь разрядов регистр 15 сдвига разбивается на восемь регистров по восемь разрядов каждый. В табл. 2 показано расположение принятой в регистр 15 сдвига информации и его разбиение на отдельные сдвиговые регистры в зависимости от разновидности сдвигов. Кежду условно разбитыми сдвиговыми регистрами информация не сдвигается. Разрыв сдвигов организован в узле 14 компоновки сдвиго- вьпс регистров путем формирования определенным образом сгиналов для инфор- мационных входов последовательного ввода информации.

-.V

При организации сдвигов на один разряд разбиений на отдельные регистры не производится и информация заносится в соответствующие разряды без перекосов.

При выполнении команд сдвигов временная диаграмма которых показана на фиг. 7, три старших разряда количества сдвигов заносится в первый счетчик 4, для подсчета сдвигов по восемь разрядов, три младших разряда - во второй счетчик для подсчета сдвигов по одному разряду. Подсчет производится вычитанием единицы по каждому импульсу сдвига до появления нулевого состояния соответствующего счетчика.

Сигналом занесения в регистр 15 сдйига, поступающим со входа 21 уст- ройс тва и далее на вход элемента И-ИЛИ 26 узла 9 запуска, и условию.

что количество сдвигов на восемь разрядов не равно нулю устанавливается в единичное состояние первый триггер 29. При этом по ненулевому состоянию первого счетчика 4 с третьего элемента И 25 этого узла вырабатывается потенциал, поступающий в узел 10 на. входы элементов ИЛИ 40 М 41 для входной коммутации данных на группе мультиплексоров 13 через которые данные передаются с перекосом как показано в табл. 2 для сдвига на восемь разрядов. Сигнал занесения с входа 21 поступает так же на входы элементов ИЛИ 36-38 узла 10, где задается режим и вырабатывается синхроимпульс записи для регистра 15 сдвига. Направлением сдвигов управляет третий и четвертый выходы дешифратора 2. По единичному состояния триггера 29, в узле 10 на элементе И 46 тактовыми импульсами со входа 8 вьщаются импульсы для сдвига на восемь разрядов и сигналы модифик-ации первого счетчи- ка 4.

После окончания сдвигов на восемь по нулевому состоянию первого счетчика 4 и единичному состоянию триггера 29 через элемент И 24 устанавливается в единичное состояние триггер 30 по которому очередным синхроимпульсом с входа 8 (элемент И.23) производится перезапись сдвинутой информации для сдвигов по одному разряду или вы- дачи на выход 20 устройства. Этим же сигналом с элемента И 23 устанавливается единичное состояние третьего триггера 31, которое разрешает сдви

ги по одному разряду тактовыми импуль

Номер выхода

Первый Второй

Третий Четвертый Пятый Шестой

f5

0

jg 5

35

0

40

сами до получения нулевого состояния второго счетчика 5,

При выполнении команды СДВИГ АРИФМЕТИЧЕСКИЙ ВПРАВО на место выдвинутой информации вдвигается знак операнда, запомненный на триггере 16 во время занесения в регистр сдвига.

В команде СДВИГ АРИФМЕТИЧЕСКИЙ ВЛЕВО выдвигаемые разряды сравниваются со знаком операнда и в случае несовпадения из узла 7 выдается признак переполнения.

В команде сложения и вычитания с плавающей точкой на зтапе выравнивания в первый счетчик 4 заносится разность порядков, в регистр 15 сдвига засылается мантисса числа с меньшим порядком с перекосами для сдвигов по четыре разряда (как показано в табл.2) по единичному состоянию пятого выхода дешифратора 2, вырабатывается режим сдвига вправо. В этом случае в узле запуска 9 сигналом занесения данных с входа 21 устанавливается в единичное состояние четвертый триггер 32, по которому, в свою очередь, тактовый серией с входа 8 в узле 10 с элемента И 45 формируются сигналы сдвига и вычитания единицы с первого счетчика. Сдвиги продолжаются до обнуления счетчика.

Таким образом, перекомпоновка (перенастройка) регистра сдвига на несколько изолированных сдвиговых регистров позволяет варьировать количеством разрядов для сдвига за один синхроимпульс в зависимости от кода операции и количества заданных сдвигов , что ведет к повышению быстродействия.

Таблица 1

Значение выхода

Команда СДВИГ Команда СДВИГ АРИФ- ЬЗ;ТИЧЕСКИЙ ВЛЕВО Команда СДВИГ ВПРАВО Команда СДВИГ ВЛЕВО Выравнивание Команда СДВИГ АРИФМЕТИЧЕСКИЙ ВПРАВО

Таблица 2

tt

Фие.1

Фиг.З

ISL

47

Фигл

- OJlJlJTJlJlJTJ tJlJl-r

Фиг. 7

| Устройство для сдвига | 1975 |

|

SU723570A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сдвигающее устройство | 1981 |

|

SU949719A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-30—Публикация

1985-11-18—Подача