1

(21)4258178/2А-24

(22)08.06.87

(46) 07.09.89. Бкхл. № 33

(71)Куйбьшевский политехнический институт им. В.В. Куйбышева

(72)Ф.М. Медников, А.В. Малинин, И.Д. Лапидус и М.Л. Нечаевский (53) 681.327.66(088.8)

(56) Авторское свидетельство СССР № 469141, кл. G 11 С 17/00, 1974.

Шигин А.Г., Дерюгин А.А. Цифровые вычислительные машины.- М.: Энергия, 1976, с. 280, рис. 10-13.

(54) БЛОК ПАМЯТИ ДЛЯ ТРАНСФОРМАТОРНОГО ПЗУ

(57) Изобретение относится к вычислительной технике и автоматике и предназначено для использования в устройствах и системах, где требуется постоянное запоминающее устройство. Цель изобретения - расширение функциональных возможностей устройства за счет осуществления считьюания в параллельном и последовательном кодах. Поставленная цель достигается за счет введения схем 5 сравнения, источника 6 опорного напряжения, дифференцирующих цепочек 7, элемента ИЛИ 8. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок памяти для полупостоянного запоминающего устройства | 1987 |

|

SU1499404A1 |

| Магнитное запоминающее устройство | 1976 |

|

SU619964A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU1048517A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Устройство для сопряжения | 1983 |

|

SU1176337A1 |

| Оперативное запоминающее устройство типа 2/5д/2 | 1978 |

|

SU746722A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

Изобретение относится к вычислительной технике и автоматике и предназначено для использования в устройствах и системах, где требуется постоянное запоминающее устройство. Цель изобретения - расширение функциональных возможностей устройства за счет осуществления считывания в параллельном и последовательном кодах. Поставленная цель достигается за счет введения схем 5 сравнения, источника 6 опорного напряжения, дифференцирующих цепочек 7, элемента ИЛИ 8. 3 ил.

3-

ел

3J

СП

о а

4

сх 4;

itj

К|У - магнитное сопротивление;

g - проводимость рассеяния между сердечниками линии.

Для согласования магнитной линии (нагруженной на волновое сопротивление

мет вид:

Соотношение (1) приФ (X) д, е

Г

(2)

31506484

Изобретение относится к вычислительной техн1же и автоматике и предназначено для использования в устройствах и системах, где требуется по- стоянное запоминающее устройство.

Цель изобретения - расширение функциональных возможностей за счет осуществления считывания тч параллельном и Последовательном кодах. 10

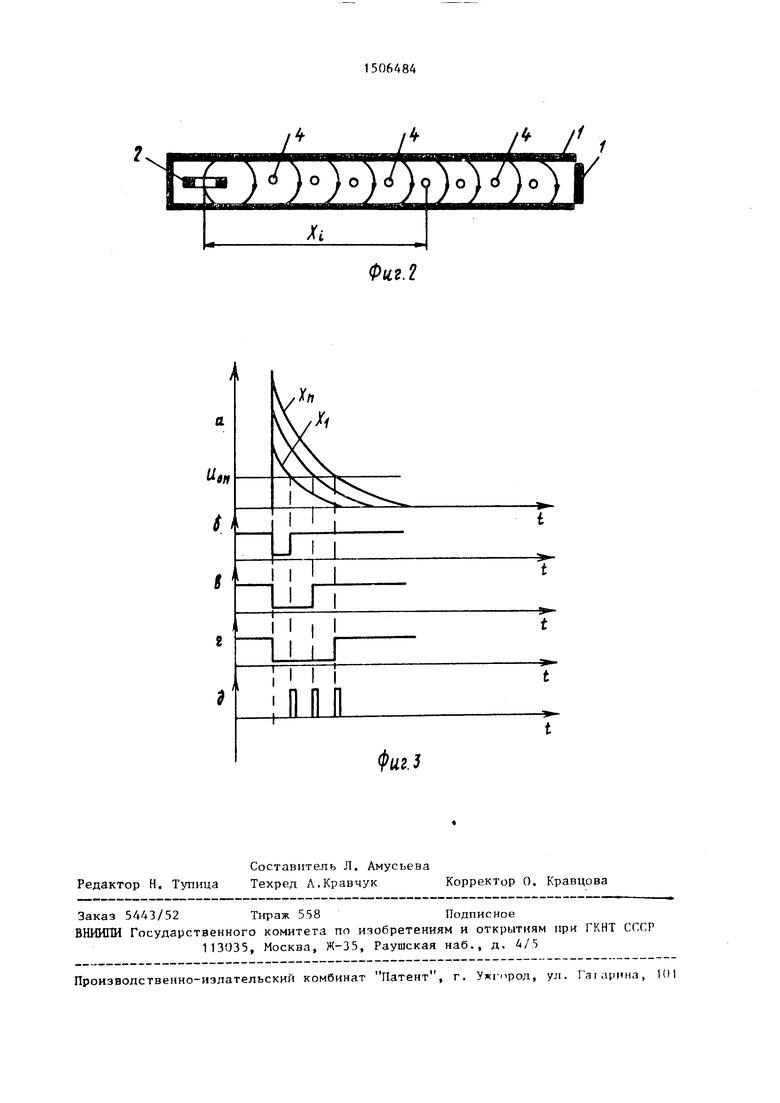

На фиг. 1 представлена схема предлагаемого блока памяти; на фиг. 2 - распределение магнитного потока в магнитной линии; на фиг.З - временные диаграммы работы блока. 15

БЛОК памяти содержит П-образные согласованные магнитные линии 1 с обмотками 2 возбуждения, подключенными к адресным шинам 3, тины 4 счи- тьшания, схемы 5 сравнения, источник 20 6 опорного напряжения, дифференцирующий блок 7, выполненный на дифференцирующих цепочках, элемент ИЛИ 8, выходные разрядные шины 9.

П-образная магнитная линия выполняется из электротехнической стали 3350, при реализации блока исполь- зутатся интегральные компараторы 521 САЗ, на которых выполняются сравнивающие устрсп тства, схема ИЛИ - микросхема .ерии К500ЛМ109. Обмотки возбуждения вьтолняются в виде плоских контуров, оптимальное число кото- P(X,t) Р рых должно составлять порядка 10. Разрядные ишны для параллельного счи- 35 Этот поток индуцирует в шинах 4 счигде 9 - значение потока при X 0.

При скачкообразном подключении обмотки 2 возбуждения к источнику питания поток в обмотке возбуткдения нарастает по закону

25

9 rt) (Р

Макс

(1 )

(3)

где с 30

L/R - постоянная времени обмотки возбуждения. Таким образом, изменение магнитного потока по д.пине линии и во времени описывается в силу (2) и (3) выражением

И

/WOKC

.e-(1).4)

тывания напряжения

и у1Ф( /

ЗЫ.; dt л а с 1

еУ,е(5)

вания.

тьгоания информации соединены непосредственно с выходами схем сравнения (интегральных KONmapaTopoB). а щина последовательна.го вывода информпции

подключена к выходу элемента ШШ. где X; - координата i-й итны считы- ны 4 считьтания при записи единицы прошивают магнитные линии 1, а при записи нуля их огибают.

Блок памяти работает следуюшлм образом.

При выборе одной из адресных шин 3 на обмотку 2 возбуждения соответствующей магнитной линии 1 подается импульс напряжения, в результате чего в ней возникает магнитный поток, определяемый из соотношения

45

50

Напряжения ,; с выходов шин 4 считывания подаются на инвертирующие входы схем 5 сравнения, на неинверти рующий вход которых подается постоя ное опорное напряжение .

При достижении равенства UgbiK , и (фиг. 3) на выходе схем 5 формируются импульсы напряжения (фиг.Зб в, г), длительность которых определя

ется из соотношения

ф(Х) +

Be

Я

(1)

где координата X отсчитывается от обмотки возбуждения (фиг. 2);

X -л вКцТ постоянная распространения магнитной линии;

К|У - магнитное сопротивление;

g - проводимость рассеяния между сердечниками линии.

Для согласования магнитной линии (нагруженной на волновое сопротивление

Соотношение (1) примет вид:

Ф (X) д, е

Г

(2)

где 9 - значение потока при X 0.

P(X,t) Р Этот поток индуцирует в шинах 4 счиПри скачкообразном подключении обмотки 2 возбуждения к источнику питания поток в обмотке возбуткдения нарастает по закону

9 rt) (Р

Макс

(1 )

(3)

P(X,t) Р Этот поток индуцирует в шинах 4 счигде с

L/R - постоянная времени обмотки возбуждения. Таким образом, изменение магнитного потока по д.пине линии и во времени описывается в силу (2) и (3) выражением

И

/WOKC

.e-(1).4)

тывания напряжения

и у1Ф( /

ЗЫ.; dt л а с 1

еУ, (5)

вания.

коорди

где X; - координата i-й итны считы-

Напряжения ,; с выходов шин 4 считывания подаются на инвертирующие входы схем 5 сравнения, на неинвертирующий вход которых подается постоянное опорное напряжение .

При достижении равенства UgbiK , и (фиг. 3) на выходе схем 5 формируются импульсы напряжения (фиг.Зб, в, г), длительность которых определяется из соотношения

.1п -5х:ь

on

(6)

Из (6) следует, что длительность импульсов, формируемых на выходе схем 5, линейно связана с коорлина- той X.

Отрицательный перепад напряжения с выходов схем 5 используется для считывания инсЬормации, записанной в блоке памяти, в параллельном коде через выходные разрядные шины 9.

Импульсы с выходов схем 5 дифференцируются с помощью дифференциру- юг;их цепочек блока 7, пр1гчен импульсы положительной полярности, возникающие за счет дифференцирования задних фронтов сигналов с выходов схем 5, воздействуют на входы элемента ИЛИ. На ее выходе при этом образуется

последовательность импульсов (фиг.3д),15 ПЗУ, содержащий накопитель на сердеч- причем наличие импульса в определенный момент времени (относительно отрицательного перепада напряжения с выходов сравнивающих схем 5) характеризует считьгоание единицы из соот- 20 ветствующегр разряда выбранного слова, а его отсутствие - считывание нуля.

Таким образом, предлагаемый блок памяти обладает более широкими функ- 25 циональными возможностями, так как обеспечивает возможность считывания информации как в параллельном, так и в последовательном коде.

Обмотки возбуждения и шины считы- 30 вания могут вьшолняться печатным мениках из магнитного материала с непрямоугольной петлей гистерезиса, адресные и разрядные шины, отличающийся тем, что, с целью расширения функциональных возможностей за счет осуществления считьтания в параллельном и последовательном кодах, он содержит схемы сравнения, источник опорного напряжения, дифференцирующие цепочки, элемент ИЛИ, выход которого является выходом последовательного вьшода информации блока памяти, входы элемента ИЛИ соединены с выходами дифференцирующего блока, входы которого подключены к выходам соответствующих схем сравнения, первые входы которых подключены к источнику опорного напряжения, а вторые входы схем сравнения подключены к шинам считьгоания накопителя, причем сердечники накопителя выполнены в виде П-образных согласованных магнитных линий, по торцам которых расположены обмотки возбуждения, подключенные к адресным шинам накопителя, выходы схем сравнения являются выходами параллельного вывода информации блока памяти.

тодом, а магнитные линии - методом напыления магнитных пленок на непроводящую основу. Это позволяет изготавливать блок памяти по интегральной технологии на одной подложке с электронными элементами, обеспечивающими функционирование ПЗУ (сравнива- 1ющие устройства, диффренцирующие цепочки, схема ИЛИ).

Согласование магнитной линии осуществляется с помощью ферромагнитного якоря, расположенного в торце магнит

ной линии. В этом случае, как следует из соотношения (6), обеспечивается линейная связь между длительностями формируемых временных интервалов и координатой шин считывания относительно обмотки возбуждения. Это существенно облегчает синхронизацию приема информации с ПЗУ в последовательном коде.

Формула изобретения Блок памяти для трансформаторного

ПЗУ, содержащий накопитель на сердеч-

никах из магнитного материала с непрямоугольной петлей гистерезиса, адресные и разрядные шины, отличающийся тем, что, с целью расширения функциональных возможностей за счет осуществления считьтания в параллельном и последовательном кодах, он содержит схемы сравнения, источник опорного напряжения, дифференцирующие цепочки, элемент ИЛИ, выход которого является выходом последовательного вьшода информации блока памяти, входы элемента ИЛИ соединены с выходами дифференцирующего блока, входы которого подключены к выходам соответствующих схем сравнения, первые входы которых подключены к источнику опорного напряжения, а вторые входы схем сравнения подключены к шинам считьгоания накопителя, причем сердечники накопителя выполнены в виде П-образных согласованных магнитных линий, по торцам которых расположены обмотки возбуждения, подключенные к адресным шинам накопителя, выходы схем сравнения являются выходами параллельного вывода информации блока памяти.

)°)))°)77Tr

XL

/

/ /

Фи2.2

Авторы

Даты

1989-09-07—Публикация

1987-06-08—Подача