g

(Л

Фие.1

31509

Цель изобретения - повышение быстродействия устройства при отладке программ. Устройство, имеющее вход 1 синхронизации, содержит генератор 2 импульсов, блоки 7, 21 и 22 индикации, счетчик 8 положения курсора, входной регистр 14, коммутаторы 11, 15 и 23, блок 18 сравнения, цифроаналоговый преобразо- ватель 19, делитель 9 частоты, счетчик 10, элементы И 5 и 12, элементы

ИЛИ 3, 4 и 24, элементы НЕ 6, 13 и 20, блок 16 эталонной памяти и формирователь 17. Изобретение обеспечивает возможность предварительного запоминания входного процесса, его статического анализа, сравнения с другим входным процессом, определения их различия, причем каждая параллельная комбинация входной информации представляется в блоке эталонной памя- ти бдним битом. 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство для отображения и редактирования информации на экране электронно-лучевой трубки | 1989 |

|

SU1695288A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве анализатора программ при разработке, наладке, контроле работоспособности и техническом обслуживании сложных программируемых цифровых устройств и систем. Цель изобретения - повышение быстродействия устройства при отладке программ. Устройство, имеющее вход 1 синхронизации, содержит генератор 2 импульсов, блоки 7, 21 и 22 индикации, счетчик 8 положения курсора, входной регистр 14, коммутаторы 11, 15 и 23, блок 18 сравнения, цифроаналоговый преобразователь 19, делитель 9 частоты, счетчик 10, элементы И 5 и 12, элементы ИЛИ 3, 4 и 24, элементы НЕ 6, 13 и 20, блок 16 эталонной памяти и формирователь 17. Изобретение обеспечивает возможность предварительного запоминания входного процесса, его статического анализа, сравнения с другим входным процессом, определения их различия, причем каждая параллельная комбинация входной информации представляется в блоке эталонной памяти одним битом. 6 ил.

25

Изобретение относится к вычислительной технике и.может быть использовано в качестве анализатора программ при разработке, наладке, контроле работоспособности и техническом обслу- живании сложных программируемых цифровых устройств и систем. ,

Целью изобретения.является повышение быстродействия при отладке .программ.

Перебор адресов чтения блоком эталонной памяти, по KOTopbiM отЪ утству- ет информация с большой скоростью, И адресов чтения, по которым информация присутствует с меньшей скоростью, при- водит к такому увеличению времени отображения входной информации.

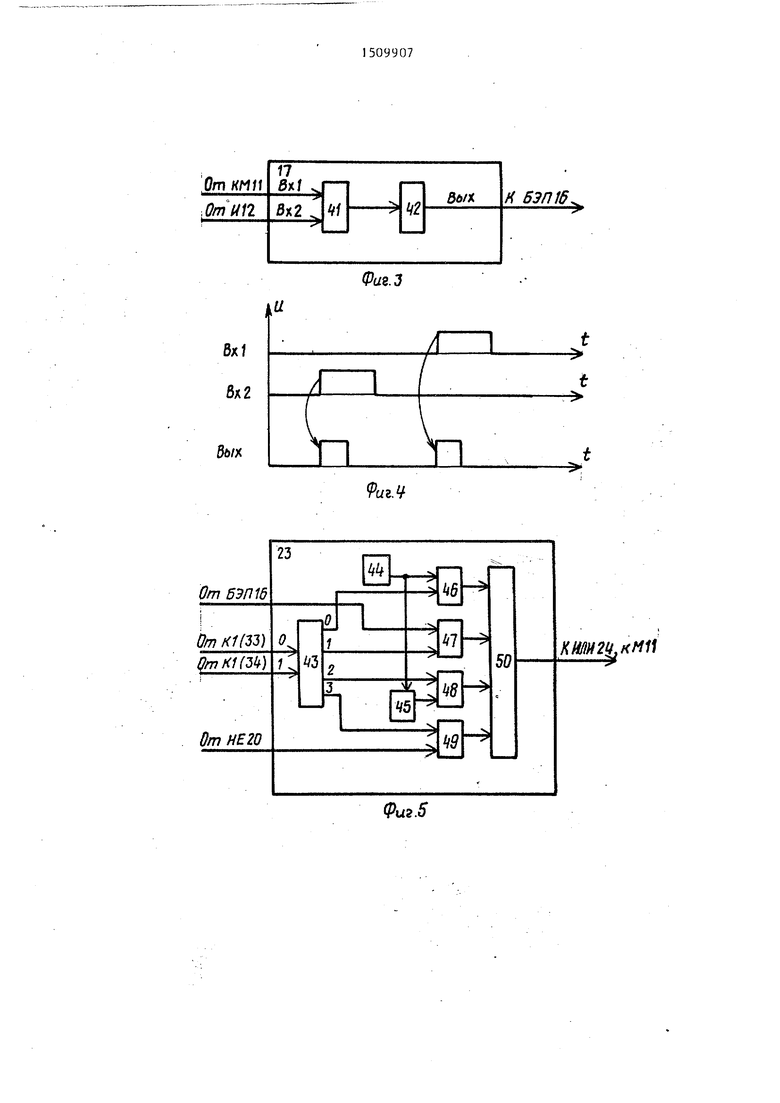

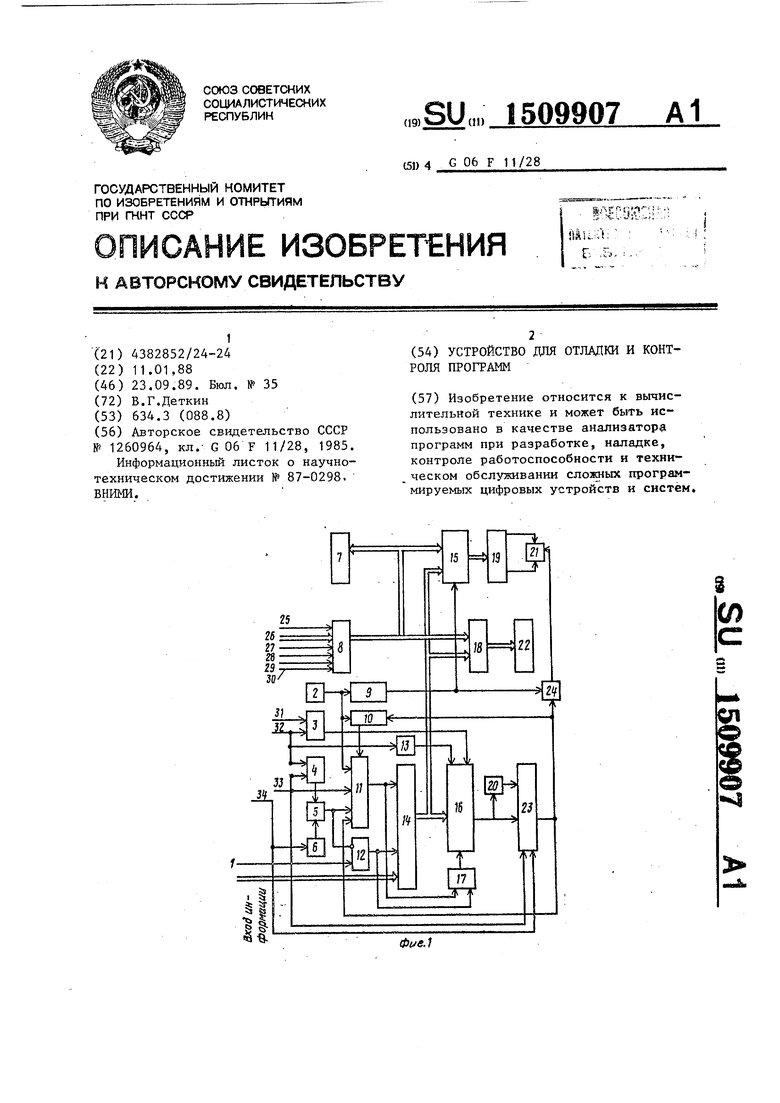

На фиг.1 представлена Структурная схема предлагаемого устройства; на фиг.2 - структурная схема возможного 35 .построения второго коммутатора; на фиг. 3 - структурная схема возможного построения формирователя; на фиг. 4 - диаграмма работы формирователя; на фиг. 5 - структурная схема возможного построения третьего коммутатора; на фиг. 6 - диаграмма работы устройства при отображении содержимого блока эталонной памяти, .

. . 5 Устройство (фиг. 1). содержит вход 1

синхронизации, генератор 2 им пульсов, . первый 3 и второй 4 элементы ИЛИ, первый элемент ИЗ, первый элемент НЕ 6, первый блок 7 индикации, счетчик 8 п положения курсора, делитель 9 частоты, счетчик 10, второй коммутатор 11, второй элемент И 12, второй элемент НЕ 13, входной регистр 14, первый-коммутатор 15, блок 16. эталонной памяти, гг формирователь. 17, блок 18 сравнения, .;. цифроаналоговый преобразователь (ЦАП) 19, третий, элемент НЕ 20, второй блок. 21 индикации, третий блок 22 индика5

5

5

ции, третий коммутатор 23, третий элемент ИЛИ 24, вход 25 записи курсора, вход 26 начальной установки курсора, вход 27 признака Вверх устройства, вход 28 признака Вниз устройства, вход 29 признака Вправо устройства, вход 30 признака Влево устройства, вход 31 записи эталона устройства, вход 32 сброса устройства, вход 33 признака отображения эталонной информации и вход 34 признака отображения входной информации.

Второй коммутатор 1.1 (.фиг. 2)содержит дешифратор 35, элементы И 37 - 39 и элемент ИЛИ 40,

Формирователь 17 (фиг.4) содержит элемент ИЛИ 41 и формирователь 42 одиночного импульса.

Третий коммутатор 23 (фиг,6) содержит дешифратор 43, генератор 44 логической 1, элемент НЕ 4;5, элементы И 46 - 49, элемент ИЛИ 50.

Вход 25 предназначен для формирования сигнала параллельной записи в счетчик 8 начального состояния курсора с входа 26. .

Вход 26 служит для набора начального положения адреса курсора с целью его последующей параллельной записи пользователем в счетчик 8. .

Вход 27 предназначен для формирования сигнала, передвигающего курсор вверх по оси X на блок 21. При калодом поступлении данного сигнала на первый вход счетчика 8 код младщей части

счетчика 8 (координата X курсора)

увеличивается на единицу.

«

Вход 28 предназначен для формирования сигнала, передвигающего курсор ВНИЗ; по оси X на блоке 21. Сигнал с входа 28 поступает на вычитающий вход счетчика 8 и уменьшает содержимое младшей части счетчика 8 на единицу.

Вход 29 служит для передвижения курсора по оси У вправо, при этом каждый сигнал на входе 29 увеличивает на единицу содержимое старшей части счетчика 8,

Вход 30 служит для передвижения курсора по оси У влево. Каждый сигнал на входе 29 регистра уменьшает на единицу содержимое старшей части счет.чика 8.

Вход 31 служит для формирования управляющего сигнала, во время действия которого происходит запись входной информации в блок 16.

Вход 32 Сброс служит для формирования управляющего сигнала, во время действия которого происходит стирание содержимого блока 16.

Вход 34 служит для формирования уп-20 ствия информации. Тот же сигнал через

равляющего сигнала, во время действия которого на блоке 21 отображается входная информация.

Дешифратор 35 в зависимости от кода, поступающего на его вход, формирует на одном из выходов сигнал, разрешающий работу соответствующего элемента И.

Элементы И 36-39 при наличии на их первом входе разрешающего потенциала с выхода дешифратора 35, а также разрешающего сигнала с выхода элемента И 5 пропускают на выход сигналы высокой либо низкой частоты.

Элемент ИЛИ 40 пропускает любой сигнал с выходов элементов И 36-39 на выход коммутатора 11.

Элемент ИЛИ 41 объединяет сигнал с выхода коммутатора 20 и с выхода элемента И 12 (Вх.1, Вх.2, фиг.5).

Формирователь 42 формирует на вход блока 16 сигнал, разрешающий обращение к блоку 16 в соответствии с диаграммой, приведенной на фиг.5 (сигнал Вых.).

Дешифратор 43 выполняет такую же функцию, как и дешифратор 35.

Генератор 43 формирует на выходе постоянный сигнал, соответствующий уровню логической 1.

Элементы И 46-49 в коммутаторе 23 выполняют те же функции, что и элементы И 36-39 в коммутаторе 11.

Элемент ИЛИ 50 в коммутаторе 23 выполняет ту же функцию, что и элемент ИЛИ 41 в коммутаторе 11.

Рассмотрим работу устройства для отладки и контроля программ в следующих пяти режимах: очистка эталонной

1509907

памяти (режим I); отображение входной информации (режим И); запись в эталонную память(режим 111 );отображение содержимого эталонной памяти (режим IV); сравнение входной информации с содержимым эталонной памяти (режим V).

Режим I предназначен для очис тки эталонной памяти устройства с целью

подготовки ее для последующей записи. Для установки данного режима пользователю необходимо на вход 32 подать . сигнал, при этом сигнал с входа 32 поступает через элемент ИЛИ 3 на вход

записи блока 16, устанавливая режим записи.

Тот же сигнал через элемент НЕ 13 поступает на информационный вход блока 16, устанавливая потенциал отсут5

0

5

0

5

0

5

элемент ИЛИ 4 и элемент И 5 поступает на управляющий вход коммутатора 11, что приводит к пропусканию через него импульсов высокой частоты с выхода генератора 2 на счетный вход входного регистра 14. Сигнал с выхода элемента И 5 с помощью элемента И 12 блокирует прохождение импульсов синхронизации на вход параллельной записи входного регистра 14, в результате он работает в ускоренном счетном режиме, формируя на выходе последовательно все комбинации (число комбинаций равно 2, где К - разрядность входного регистра 14, равная числу возможных адресов блока 16). Комбинации с выхода входного регис- ра 14 поступают на адресные входы блока 16, выбирая последовательно все его ячейки для записи,

Счетные импульсы с выхода коммутатора 11 одновременно поступают на формирователь 17 (lUlll 41) и с выхода формирователя 42 сформированные импульсы (фиг.З и 4) поступают в блок 16, производя запись нуля (признак отсутствия информации). Импульсы записи поступают синхронно с изменением адреса записи. Когда на входном регистре 14 будет сформировано число адресов-, равное 2 весь массив блока 16 окажется очищенным и готовым к занесению новой информации.

Режим II предназначен для отображения в реальном масштабе времени входной информации блоком 21. Для установки данного режима пользователь на вход 34 должен подать сигнал. Этот сигнал поступает на вход элемента НЕ 6 и управляющий вход коммутатора 23.

В результате через элемент И 48 на выходе коммутатора 23 устанавливается постоянный сигнал, разрешающий через элемент ИЛИ .24 отображение ин- формации на блоке 21, Сигнал с выхода элемента НЕ 6 с помощью элемента И 5 поступает на управляющий вход коммутатора 11, запрещая прохождение через него счетных импульсов, и на элемент И 12, разрешая прохождение через него импульсов синхронизации с входа синхронизации устройства на вход параллельной записи входного регистра 14. На информационные входы входного регистра 2 поступает информация с входа устройства.

Таким образом, входной регистр 14, сохраняя входную информацию, выполняет роль буферного регистра, Информа- ция с выхода входного регистра 14 через коммутатор 15 преобразуется с помощью ЦАП 19 в два напряжения, определяющие координаты X и У данной комбинации на блоке 21. В результате каж дои параллельной комбинации на входе устройства соответствует одна точка на блоке 21. Совокупность всех входных комбинаций отображается на блоке

21 В виде совокупности точек, относи- 30 формирования адреса чтения и на вход

тельное расположение которых однозначно определяет входную информационную последовательность. Таким образом, визуально наблюдая в режиме II входную информацию в реальном масштабе времени, пользователь может ее ана лнзировать с целью обнаружения ошибок сбоев, фиксации области устойчивости работы и т.д.

Режим I предназначен для занесения эталонной информации в блок 16. Предполагается, что перед этим блок 16 был очищен в режиме I.

Режим Г( устанавливается путем подачи сигнала на вход 31. Эталонная информация поступает, на вход информации устройства и сопровождается импульсами синхронизации с входа синхронизации устройства. Сигнал с входа 31 через элемент ИЛИ 3 поступает на управляющий вход блока 16, устанавливая режим записи. На информационном входе блока 16с выхода элемента НЕ 13 постоянно присутствует потенциал единицы (признак наличия информации). Потенциалом с выхода элемента И 5 коммутатор 11 закрыт, а прохождение синхроимпульсов через элемент И 12 разрешено.

Под синхросигналы входная информация записывается во входной регистр 14 и с его выхода поступает на адресные входы блока 16. Синхросигналы поступают также на вход формирователя 17, осуществляющего запись в блок 16. В результате каждая эталонная комбина- ция, поступающая на вход устройства, представлена в блоке 16 одним битом, адрес которого равен ,значению данной кдмбинации.

Режим IV предназначен для отображения на блоке 21 содержимого блока 16. Режим 1V устанавливается путем подачи сигнала на вход 33, при этом сигнал с входа 33 через элементы ИЛИ 4 и И 5 разрешает работу коммутатору 11 и запрещает прохождение синхроимпульсов через элемент И 12. Этот же сигнал, поступая на коммутатор 23 (дешифратор 43), разрешает прохождение информации с выхода блока 16 на выход коммутатора 23 (через элемент И 47). С выхода ИЛИ 3 на управляющий вход .блока 16 поступает нулевой потенциал, определяющий режим чтения. Импульсы с выхода коммутатора 11 поступают на счетньй вход входного регистра 14 для

5

0

е

5

0

формирователя 17. Входной регистр 14, работая в счетном режиме, формирует 2 адресов чтения. При чтении блока 16 может возникнуть две ситуации: по данному адресу присутствует информация (считанный бит равен единице) и информация отсутствует (считанный бит равен нулю). С целью улучшения качества отображения алгоритм работы устройства для первой и второй ситуации различен.

В случае отсутствия информации с выхода блока 16 потенциал нуля с. выхода коммутатора 23 поступает на элемент ИЛИ 24, блокируя отображение содержимого входного регистра 14 на блок. 21 и на вход коммутатора 11, открывая элемент И 38, через который с генератора 2 на выход коммутатора 11 переходит высокая частота, и, следовательно, входной регистр 14 быстрее формирует адреса чтения. I

Сигнал нуля с выхода коммутатора 23 поступает на второй вход счетчика 10, удерживая его в сброшенном состоянии и запрещая счет. В случае наличия информации в блоке 16 с выхода коммутатора 23 поступает потенциал единицы, разрешая отображение содержимого входного регистра 14 на блок

915

21 (через элемент ИЛИ 24) и счет в счетчике 10, а также прохождение с выхода счетчика 10 через коммутатор 11 низкой частоты (через И 39). В ре- зультате длительность отображения информации на блоке 21 увеличивается а, следовательно, улучшается качество ег отображения.

Режим V предназначен для отобра- жения на блоке 21 отличной от содержимого блока 16 части входной информации. Данный режим целесообразно использовать при анализе нестабильных во времени процессов, например, при диагностике сбоев ЭВМ. Режим V устанавливается путем подачи сигнала на входы 33 и 34. В этом случае коммутатор 11 заблокирован, а синхроимпульсы проходят через элемент И 12 на выход параллельной записи входного регистра 14, фиксируя в нем входную информацию. Одновременно сигналы с входов 33 и 34 поступают на коммутатор 23 (дешифратор 43), пропуская инверсную информацию с блока 16 (с выхода НЕ 20) через элемент И 49 на вход коммутатора 23. При этом на блоке 21 разрешается отображение содержимого входного регистра 14 в случае отсутствия единицы по данному адресу в блоке 16, т.е. в случае отсутствия данной комбинации в эталонной памяти.

При отсутствии сигналов на- входах 33 и 34 на выход коммутатора 23 про- ходит сигнал с генератора 44, т.е. потенциал нуля, чем блокируется отображение на блоке 21 любой информации, кроме курсора.

Курсор отображается на блоке 21 в любых режимах, при этом по сигналу с выхода делителя 9 на вход коммутатора 15 переключаются сигналы с выхода счетчика 8.

Управляя положением курсора с помощью входов 25 - 30 можно совместить курсор с интересующей пользователя точкой на экране блока 21. Момент совпадения точно фиксируется в блоке 18 сравнения и отображается на блоке 22, при этом значение информации совпадает с кодом курсора, отображаемом на блоке 7.

Формула изобретения

Устройство для отладки и контроля программ, содержащее генератор импуль7

10

сов, первый, второй и третий блоки индикации, счетчик положения курсора, входной регистр, первый коммутатор, блок сравнения и Ц1{фроаналоговый преобразователь, причем входы записи курсора, начальной установки курсора, признаки сдвига Вверх, признаки сдвига Вниз, признаки сдвига Вправо, признаки сдвига Влево устройства соединены соответственного с входом записи, с информационным входом, с

5

0

5

30

5

0

5

O.

5

первым входом сложения, с первьм входом вычитания, с вторым входом сложения , с вторым входом вычитания счетчика положения курсора, информационные выходы которого соединены с входами первого блока индикации и первыми информационными входами первого коммутатора и блока сравнения, выход равенства которого соединен с входом второго блока индикации, информационные входы устройства соединены с информационными входами входного регистра, выходы которого соединены с вторыми информационными входами блока сравнения и первого коммутатора, выходы которого соединены с входами цифроана- логового преобразователя, первый и: второй выходы которого соединены с

о

входами сигналов развертки по координатам соответственно X и У, третьего блока индикации, отличаю- щ е-е с я тем, что, с целью повышения быстродействия при отладке программ, в устройство введены делитель частоты, счетчик-, первый и второй элементы И, первый и третий элементы ИЛИ, первый, второй и третий элементы НЕ, второй и третий кo мyтaтopы, блок эталонной памяти, формирователь одиночного импульса, причем вход записи блока памяти устройства соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом обнуления блока эталонной памяти, вход сброса устройства соединен с вторым входом первого элемента ИЛИ, с первым информационным входом второго коммутатора, i с первым входом второго элемента ИЛИ, выход которого соединен с первым вхо- дом первого элемента И, вход признака отображения эталонной информации устройства соединен с вторым входом второго элемента ИЛИ, с первым информа- ционньм входом третьего коммутатора, вторым информационным входом второго коммутатора, выход которого соединен с вторым информационным входом третьего коммутатора, с первым входом третьего элемента ИЛИ и с входом запрет счетчика, вход признака отображения входной информации устройства соединен с вторым информационным входом третьего коммутатора и через первый элемент НЕ с вторым входом первого элемента И, выход которого соединен с инверсным входом второго элемента. И и первым тактовым входом второг коммутатора, вход сброса устройства через второй элемент НЕ соединен.с информационным входом блока эталонной памяти, выход которого соединен с первым управляющим, входом третьего коммутатора и через третий элемент НЕ - с вторым управляющим входом третьего коммута.тора, выход генератора импульсов соединен со счетным входом счетчика, с вторым тактовым входом второго коммутатора и через делитель частоты с управляющим входом первого

коммутатора и с вторым входом третьего элемента ИЛИ, выход которого соединен с входом разрешения индикации третьего блока индикации, вход синхронизации устройства соединен с прямым входом второго элемента И, выход которого соединен с входом записи входного регистра и первым входом

формирователя одиночного импульса, вход синхронизации устройства соединен с прямым входом второго элемента И, выход переполнения счетчика соединен с управляющим входом третьего

коммутатора, выход которого соединен со счетным входом входного регистра и вторым входом формирователя одиночного сигнала, выход которого соединен с входом записи блока эталонной памяти, адресные входы которого подключены соответственно к выходам входног о регистра.

фие.г

Bxf

5x2

A I

Sft/x

Фаг.З

A I

Фыг.5

| Устройство для визуального контроля исполнения программ | 1984 |

|

SU1260964A1 |

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| ВНИМИ. | |||

Авторы

Даты

1989-09-23—Публикация

1988-01-11—Подача