гз

60

со

формируемой функции. Устройство содержит блок 1 памяти микрокоманд, группу 2.1-2.П блоков памяти, блок 3 памяти кодов настройки, коммутатор А, цифро-аналоговый преобразователь 5, триггер 6 запуска, блок 7 синхронизации, счетчик 8 периодов, коммутатор 9 адреса, мультиплексор 10 условий, регистры 11, 12 адреса,- счетчик 13 адреса, буферный регистр

14, регистр 15 настройкр, выходной регистр 16, элемент И 17, одновибра- тор 18, входы 19 кода функции, 20 количества периодов, 21 пуска, 22 логических условий устройства, выход 23 устройства. Поставленная цель достигается введением нсвых элементо и связей, обеспечиваняцих изменение формируемой функции под действием внешних логических условий. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

1

Изобретение относится к вычислиельной технике- и может быть использовано для формирования периодичесих сигналов, имеющих сложную структуру.

Целью изобретения является расширение области применения за счет динамического изменения формируемой функции в соответствии с внешними логическими условиями.

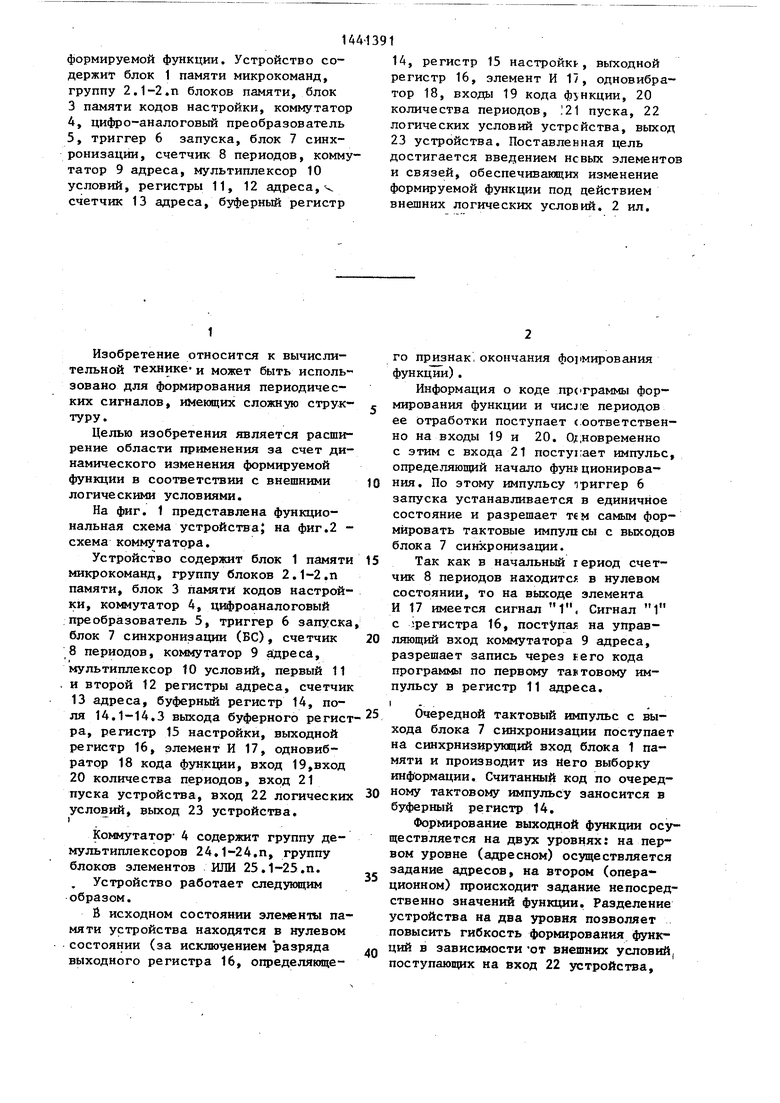

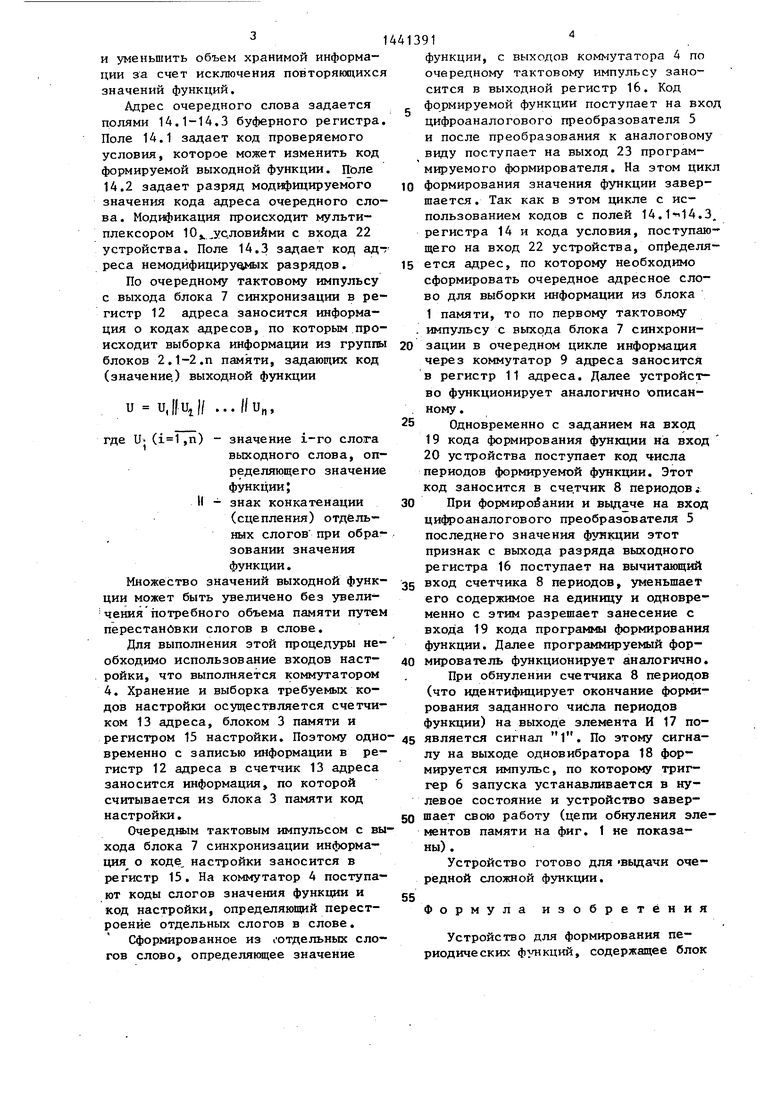

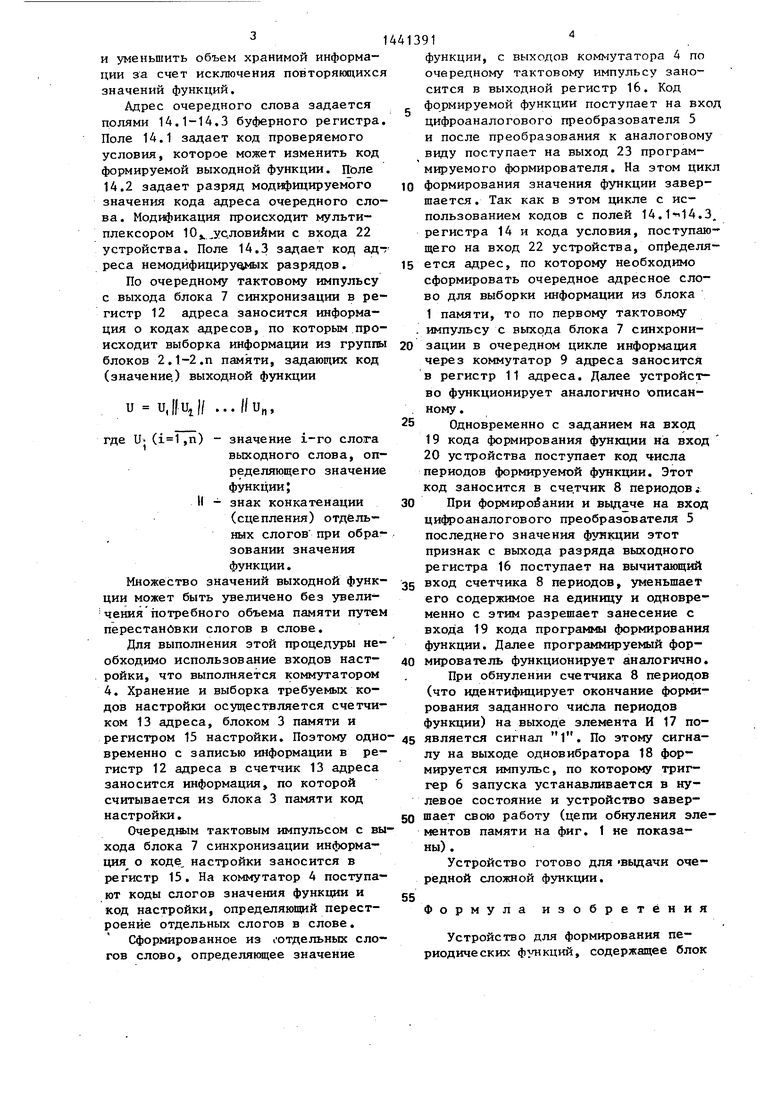

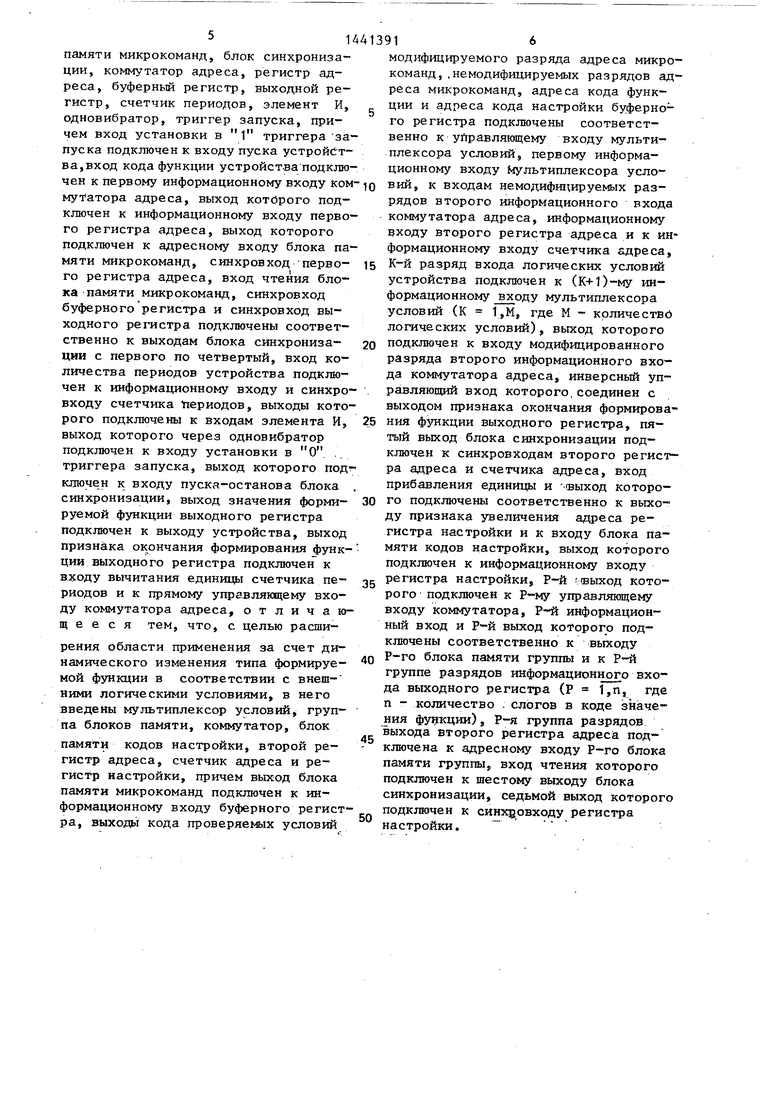

На фиг. 1 представлена функциональная схема устройстваJ на фиг,2 - схема коммутатора.

Устройство содержит блок 1 памяти микрокоманд, группу блоков 2.1-2.П памяти, блок 3 памяти кодов настройки, коммутатор 4, цифроаналоговый преобразователь 5, триггер 6 запуска, блок 7 синхронизации (БС), счетчик 8 периодов, коммутатор 9 айреса, мультиплексор 10 условий, первый 11 и второй 12 регистры адреса, счетчик 13 адреса, буферный регистр 14, поля 14.1-14.3 выхода буферного регистра, регистр 15 настройки, выходной регистр 16, элемент И 17, одновиб- ратор 18 кода функции, вход 19,вход 20 количества периодов, вход 21 пуска устройства, вход 22 логических

условий, выход 23 устройства.

I

Коммутатор- 4 содержит группу де- мультиплексоров 24,1-24.п, группу блоков элементов ИЛИ 25,1-25.п.

Устройство работает следующим образом.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением разряда выходного регистра 16, определяюще0

5

0

5

0

5

0

го признак,окончания фо1 мирования функции).

Информация о коде программы формирования функции и периодов ее отработки поступает е.оответствен- но на входы 19 и 20. Of.HOBpeMeHHo с этим с входа 21 постукает импульс, определяющий начало фунг ционирова- ния. По этому импульсу триггер 6 запуска устанавливается в единичное состояние и разрешает т€М самым формировать тактовые импул сы с выходов блока 7 синхронизаи;ии.

Так как в начальный гериод счетчик 8 периодов находите}- в нулевом состоянии, то на выходе элемента И 17 имеется сигнал 1, Сигнал 1 с «.регистра 16, поступая на управляющий вход коммутатора 9 адреса, разрешает запись через tero кода программы по первому тактовому импульсу в регистр 11 адреса,

I - ..

Очередной тактовый импульс с выхода блока 7 синхронизации поступает на синхрнизирующий вход блока 1 памяти и производит из йего выборку информации. Считанный код по очередному тактовому импульсу заносится в буферный регистр 14,

Формирование выходной функции осуществляется на двух уровнях; на первом уровне (адресном) осуществляется задание адресов, на втором (операционном) происходит задание непосредственно значений функции. Разделение устройства на два уровня позволяет повысить гибкость формирования функций в зависимости -от внешних условий, поступающих на вход 22 устройства.

и уменьшить объем хранимой информации за счет исключения повторяющихся значений функций.

Адрес очередного слова задается полями 14.1-14.3 буферного регистра. Поле 14.1 задает код проверяемого условия, которое может изменить код формируемой выходной функции. Поле 14.2 задает разряд модифицируемого значения кода адреса очередного слова . Модификация происходит мультиплексором 10 ,ус,ловийми с входа 22 устройства. Поле 14.3 задает код ад-т реса немодифицируо№1х разрядов.

По очередному тактовому импульсу с выхода блока 7 синхронизации в регистр 12 адреса заносится информация о кодах адресов, по которым происходит выборка информации из группы блоков 2.1-2.п памяти, задающих код (значение.) выходной функции

и ujfuj/ ... /1и„,

где Uj (,п)

II значение 1-го слога выходного слова, определяющего значение функции;

знак конкатенации (сцепления) отдельных слогов при образовании значения функции.

Множество значений выходной функции может быть увеличено без увели- чения потребного объема памяти путем перестанйвки слогов в слове.

Для выполнения этой процедуры необходимо использование входов настройки, что выполняется коммутатором 4. Хранение и выборка требуемых кодов настройки осуществляется счетчиком 13 адреса, блоком 3 памяти и

50

регистром 15 настройки. Поэтому одно- 45 является сигнал 1. По этому сигналу на выходе одновибратора 18 формируется импульс, по которому триггер 6 запуска устанавливается в нулевое состояние и устройство завершает свою работу (цепи обнуления элементов памяти на фиг. 1 не показаны) .

Устройство готово для вьщачи очередной сложной функции.

Формула изобретения

Устройство для формирования периодических функций, содержащее блок

временно с записью информации в регистр 12 адреса в счетчик 13 адреса заносится информация, по которой считывается из блока 3 памяти код настройки,

Очеред1ым тактовым импульсом с выхода блока 7 синхронизации информация о коде настройки заносится в регистр 15. На коммутатор 4 поступают коды слогов значения функции и код настройки, определяющий перестроение отдельных слогов в слове.

Сформированное из 1 отдельных слогов слово, определякщее значение

55

функции, с выходов коммутатора 4 по очередному тактовому импульсу заносится в выходной регистр 16. Код формируемой функции поступает на вход цифроаналоговогЬ преобразователя 5 и после преобразования к аналоговому виду поступает на выход 23 программируемого формирователя. На этом цикл

0 формирования значения функции завершается. Так как в этом цикле с использованием кодов с полей 14.1 п14.3. регистра 14 и кода условия, поступающего на вход 22 устройства, оп1)еделя5 ется адрес, по которому необходимо сформировать очередное адресное слово для выборки информации из блока 1 памяти, то по первому тактовому . импульсу с выхода блока 7 синхрони0 зации в очередном цикле информация через коммутатор 9 адреса заносится в регистр 11 адреса. Далее устройство функционирует аналогично описанному.

5 Одновременно с заданием на вход

19кода формирования функции на вход

20устройства поступает код числа периодов формируемой функции. Этот код заносится в сче.тчик 8 периодов .0 При фогмиройании и выдаче на вход ци ч оаналогового преобразователя 5 последнего значения функции этот признак с выхода разряда выходного регистра 16 поступает на вычитающий

5 вход счетчика 8 периодов, уменьщает его содержимое на единицу и одновременно с этим разрешает занесение с входа 19 кода программы формирования функции. Далее программируемый фор0 мирователь функционирует аналогично. При обнулении счетчика 8 периодов (что идентифицирует окончание формирования заданного числа периодов функции) на выходе элемента И 17 по50

45

55

памяти микрокоманд, блок синхронизации, коммутатор адреса, регистр адреса, буферный регистр, выходной регистр, счетчик периодов, элемент И, одновибратор, триггер запуска, причем вход установки в 1 триггера запуска подключен к входу пуска устройства,вход кода функции устройства подключен к первому информационному входу ком мутатора адреса, выход KOTdporo подключен к информационному входу первого регистра адреса, выход которого подключен к адресному входу блока памяти микрокоманд, синхровход перво- го регистра адреса, вход чтения блока памяти микрокоманд, синхровход буферного регистра и синхровход выходного регистра подключены соответственно к выходам блока синхрониза- ции с первого по четвертый, вход количества периодов устройства подключен к информационному входу и синхро входу счетчика периодов, выходы которого подключены к входам элемента И, выход которого через одновибратор подключен к входу установки в О. .. триггера запуска, выход которого под ключей к входу пуска-останова блока синхронизации, выход значения форми- руемой функции выходного регистра подключен к выходу устройства, выход признака окончания формирования функции выходного регистра подключен к входу вычитания единицы счетчика пе- риодов и к прямому управляющему входу коммутатора адреса, отличающееся тем, что, с целью расширения области применения за счет динамического изменения типа формируе- мой функции в соответствии с внеш- ними логическими условиями, в него введены мультиплексор условий, группа блоков памяти, коммутатор, блок

„

памяти кодов настройки, второй регистр адреса, счетчик адреса и регистр настройки, причем выход блока памяти микрокоманд подключен к информационному входу буферного регист

ра, выходы кода проверяемых условий

0 5 0 5

5

0

модифицируемого разряда адреса микрокоманд, .немодифицируемых разрядов адреса микрокоманд, адреса кода функции и адреса кода настройки буферного регистра подключены соответственно к управляющему входу мультиплексора условий, первому информационному входу { мультиплексора условий, к входам немодифицируемых разрядов второго информационного входа коммутатора адреса, информационному входу второго регистра адреса и к информационному входу счетчика адреса, К-й разряд входа логических условий устройства подключен к (К+1)-му информационному Jзxoдy мультиплексора условий (К 1,М, где М - количестве логических условий), выход которого подключен к входу модифицированного разряда второго информационного входа коммутатора адреса, инверсный управляющий вход которого,соединен с выходом признака окончания формирования функции выходного регистра, пятый выход блока синхронизации подключен к синхровходам второго регистра адреса и счетчика адреса, вход прибавления единицы и (выход которого подключены соответственно к выходу признака увеличения адреса регистра настройки и к входу блока памяти кодов настройки, выход которого подключен к информационному входу регистра настройки, Р-й выход которого подключен к Р-му управляющему входу коммутатора, Р-й информационный вход и Р-й выход которого подключены соответственно к выходу Р-го блока памяти группы и к Р-й группе разрядов информационного входа выходного регистра (Р 1,п, где п - количество . слогов в коде значе- Jiия функции), Р-я группа разрядов выхода второго регистра адреса подключена к адресному входу Р-го блока памяти группы, вход чтения которого подключен к шестому выходу блока синхронизации, седьмой выход которого подключен к синхвовходу регистра настройки. - ..

Л V

Ti

2V./

ТЕ

2S

Ф(е,2

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программируемый формирователь периодической функции | 1985 |

|

SU1275772A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-10—Подача