31513522

Изобретение относится к вычисли- тельной технике и может быть исполь- зовано при проектировании запоминаю- щих устройств на базе перестраивае- мых регистров сдвига.

Целью изобретения является расши- рение области применения ячейки памя- ти за счет возможности сохранения в

ней информации при ее выключении. 10

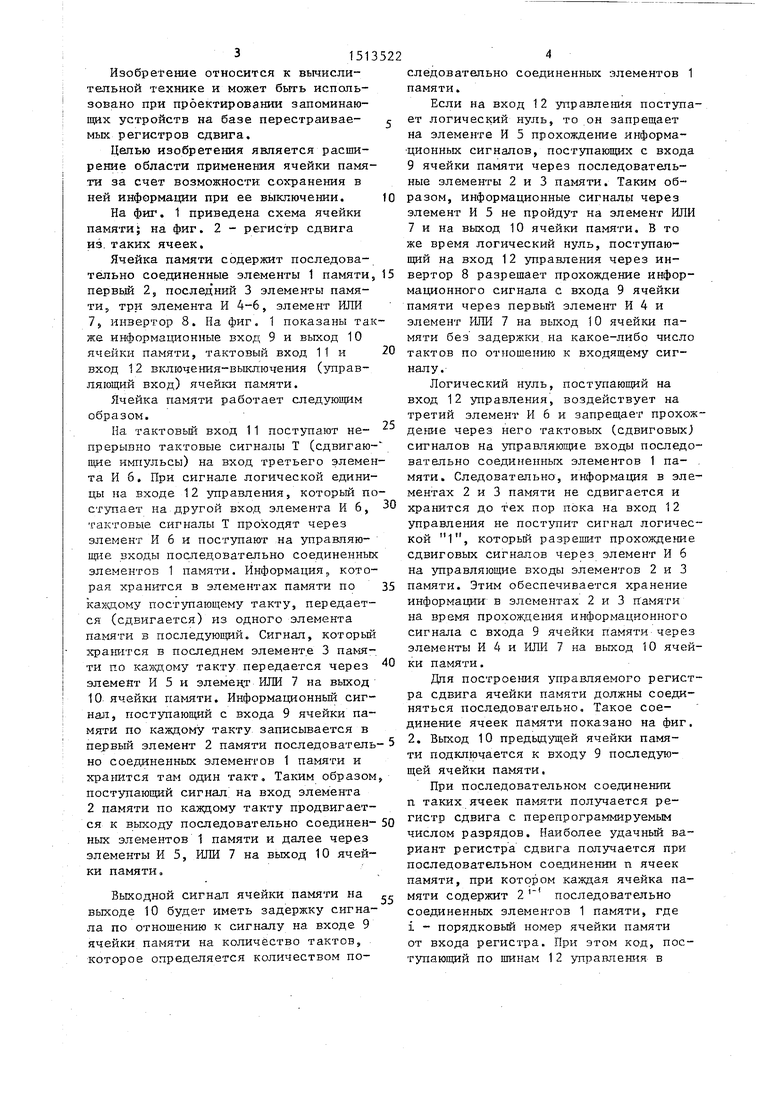

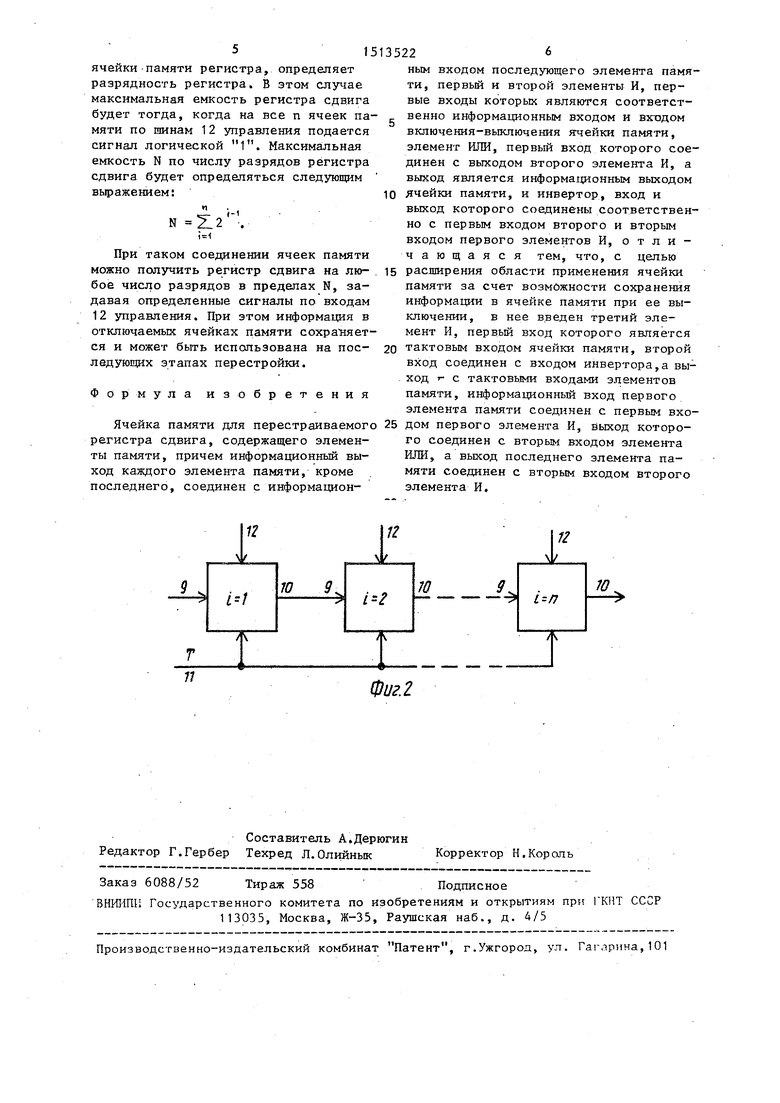

На фиг. 1 приведена схема ячейки памяти; на фиг. 2 - регистр сдвига из. таких ячеек.

Ячейка памяти содержит последовательно соединенные элементы 1 памяти, 15 первьй 2, послед ний 3 элементы памяти, три элемента И 4-6, элемент ИЛИ 7, инвертор 8. На фиг, 1 показаны также информационные вход 9 и выход 10 ячейки памяти, тактовый вход 11 и 20 вход 12 включения-выключения (управляющий вход) ячейки памяти.

Ячейка памяти работает следующим образом.

На тактовый вход 11 поступают не- прерывно тактовые сигналы Т (сдвигаю- шив импульсы) на вход третьего элемента И б . При сигнале логической единицы на входе 12 управления, который поступает на другой вход элемента И 6, 30 тактовые сигналы Т проходят через элемент И 6 и поступают на управляющие входы последовательно соединенных элементоБ 1 памяти. Информация, которая хранится в элементах памяти по 35 каждому поступающему такту, передается (сдвигается) из одного элемента памяти в последующий. Сигнал, который храьштся в последнем элементе 3 памя40

ти по каждому такту передается через

элемент И 5 и элемент ИЛИ 7 на выход 10 ячейки памяти. Информационньш сигнал, поступаюЕЩЙ с входа 9 ячейки памяти по каждому такту записывается в первый элемент 2 памяти последователь но соединенных элементов 1 памяти и хранится там один такт. Таким образом поступающий сигнал на вход элемента 2 памяти по каждому такту продвигается к выходу последовательно соединен- ных элементов 1 памяти и далее через элементы И 5, ИЛИ 7 на выход 10 ячейки памяти.

Выходной сигнал ячейки памяти на выходе 10 будет иметь задержку сигнала по отношению к сигналу на входе 9 ячейки памяти на количество тактов, которое определяется количеством по

0

5 0

05

0

5 0

г

следовательно соединенных элементов 1 памяти.

Если на вход 12 управления поступает логический нуль, то он запрещает на элементе И 5 прохождение информа- ционных сигналов, поступающих с входа 9 ячейки памяти через последовательные элементы 2 и 3 памяти. Таким образом, информационные сигналы через элемент И 5 не пройдут на элемент ИЛИ 7 и на выход 10 ячейки памяти. В то же время логический нуль, поступающий на вход 12 управления через инвертор 8 разрешает прохождение информационного сигнала с входа 9 ячейки памяти через первьй элемент И 4 и элемент ИЖ 7 на выход 10 ячейки памяти без задержки.на какое-либо число тактов по отношению к входящему сигналу.

Логический нуль, поступающий на вход 12 управления, воздействует на третий элемент И 6 и запрещает прохож- через него тактовых (сдвиговых) сигналов на управляющие входы последовательно соединенных элементов 1 па- . мяти. Следовательно, информация в элементах 2 и 3 памяти не сдвигается и хранится до тех пор пока на вход 12 управления не поступит сигнал логической 1, который разрешит прохождение сдвиговых сигналов через элемент И 6 на управляющие входы элементов 2 и 3 памяти. Этим обеспечивается хранение информации в элементах 2 и 3 памяти на время прохож,це1ия информационного сигнала с входа 9 ячейки памяти через элементы И 4 и ИЛИ 7 на выход 10 ячейки памяти.

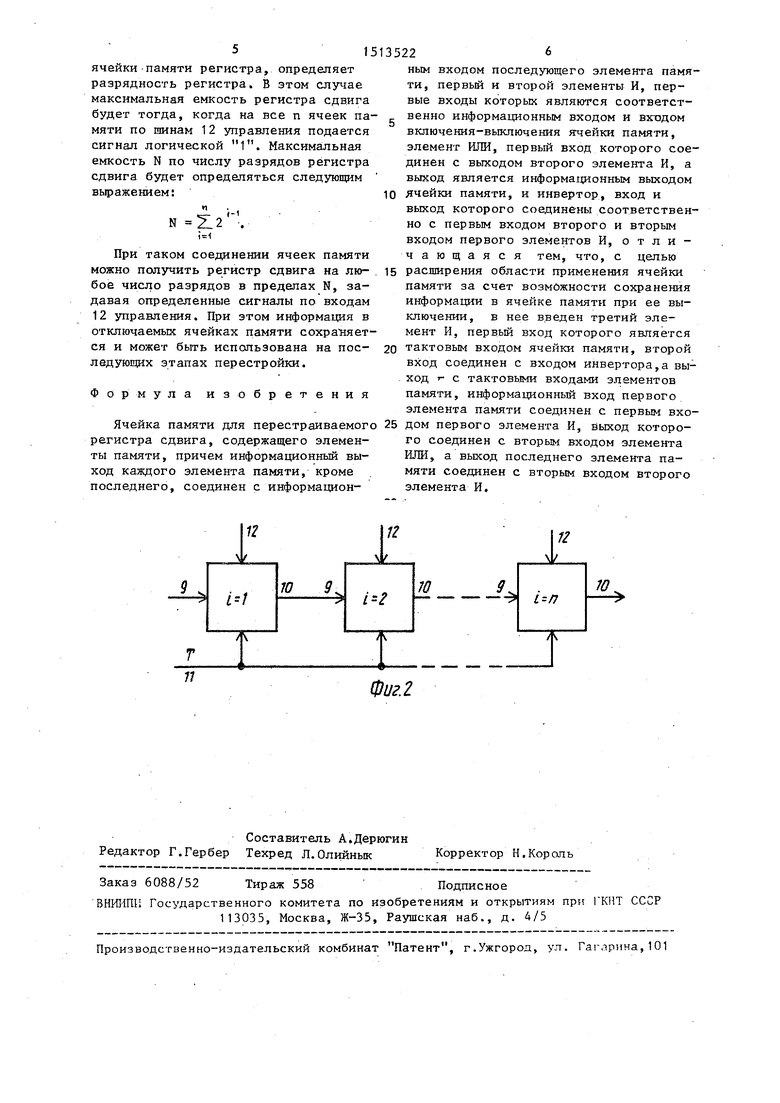

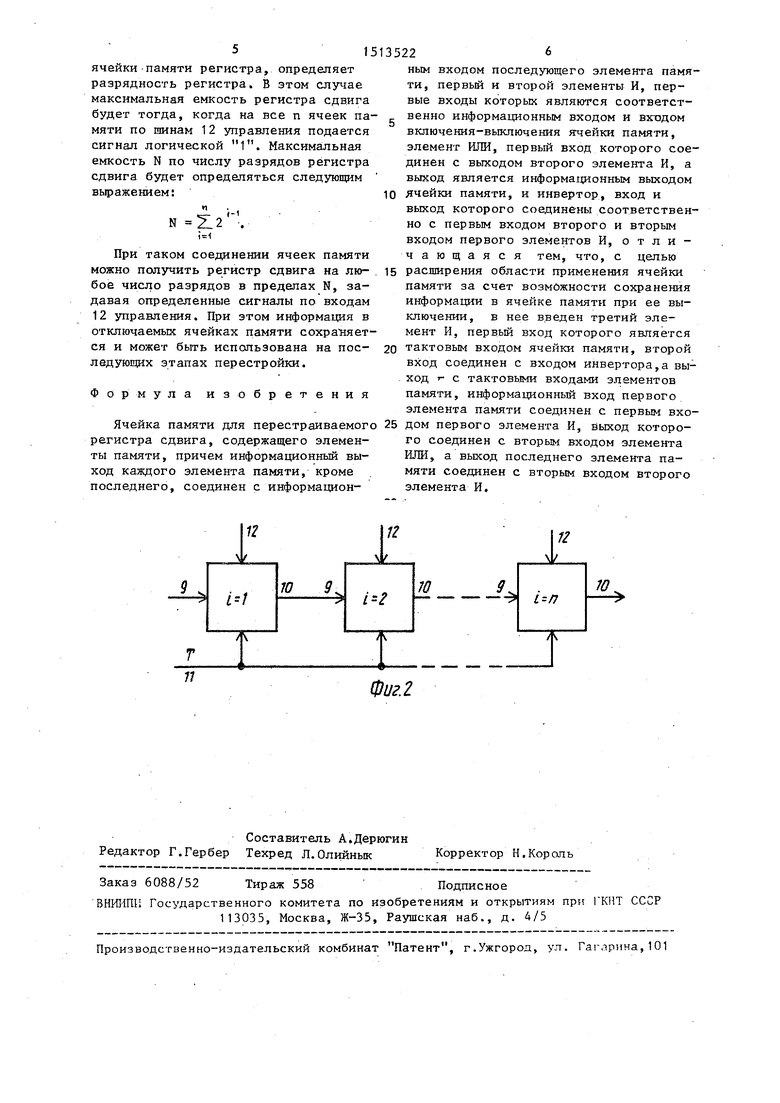

Для построения управляемого регистра сдвига ячейки памяти должны соединяться последовательно. Такое соединение ячеек памяти показано на фиг. 2. Выход 10 предьщущей ячейки памяти подключается к входу 9 последующей ячейки памяти.

При последовательном соединении п таких ячеек памяти получается регистр сдвига с перепрограммируемым числом разрядов. Наиболее удачный вариант регистра сдвига получается при последовательном соединении п ячеек памяти, при котором каждая ячейка памяти содержит 2 последовательно соединенных элементов 1 памяти, где i - порядковьвй номер ячейки памяти от входа регистра. При этом код, поступающий по шинам 12 упраачеш я в

ячейки-памяти регистра, определяет разрядность регистра. В этом случае максимальная емкость регистра сдвига будет тогда, когда на все п ячеек памяти по шинам 12 управления подается сигнал логической 1. Максимальная емкость N по числу разрядов регистра сдвига будет определяться следующим выражением:

in . N 2 .

i

При таком соединении ячеек памяти можно получить регистр сдвига на лю- бое число разрядов в пределах N, задавая определенные сигналы по входам 12 управления. При этом информация в отключаемых ячейках памяти сохраняется и может быть использована на последующих этапах перестройки.

Формула изобретения

ным входом последующего элемента памяти, первьй и второй элементы И, первые входы которых являются соответственно информационным входом и входом включения-выключения ячейки памяти, элемент ИЛИ, первый вход которого соединен с выходом второго элемента И, а выход является информа1:№1онным выходом

ячейки памяти, и инвертор, вход и

выход которого соединены соответственно с первым входом второго и вторым входом первого элементов И, отличающаяся тем, что, с целью

расширения области применения ячейки памяти за счет возможности сохранения информации в ячейке памяти при ее выключении, в нее введен третий элемент И, первьй вход которого является

тактовым входом ячейки памяти, второй вход соединен с входом инвертора,а выход т- с тактовыми входами элементов памяти, информационный вход первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1979 |

|

SU842966A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU769631A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для задержки сигналов | 1985 |

|

SU1345325A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Приемник М-ичных дискретных сигналов | 1987 |

|

SU1497746A1 |

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

Изобретение относится к области вычислительной техники и может быть использовано при проектировании запоминающих устройств на базе перестраиваемых регистров сдвига. Целью изобретения является расширение области применения ячейки памяти за счет возможности сохранения в ней информации при ее выключении. Для достижения цели в ячейку памяти введен третий элемент И 6, а первый 4 и второй 5 элементы И и элемент ИЛИ 7 соединены так, чтобы блокировать поступление информации на выход ячейки памяти при ее выключении. 2 ил.

элемента памяти соединен с первым вхоЯчейка памяти для перестраиваемого 25 дом первого элемента И, йькод которо- регистра сдвига, содержащего элемен- го соединен с вторым входом элемента ты памяти, причем информационный вы- ИЛИ, а выход последнего элемента па- ход каждого элемента памяти, кроме . мяти соединен с вторым входом второго последнего, соединен с информацион- элемента И,

77

W

Фиг.2

| РЕГИСТР СДВИГА | 1972 |

|

SU432602A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU842966A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-10-07—Публикация

1987-02-23—Подача