(54) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1988 |

|

SU1539842A1 |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

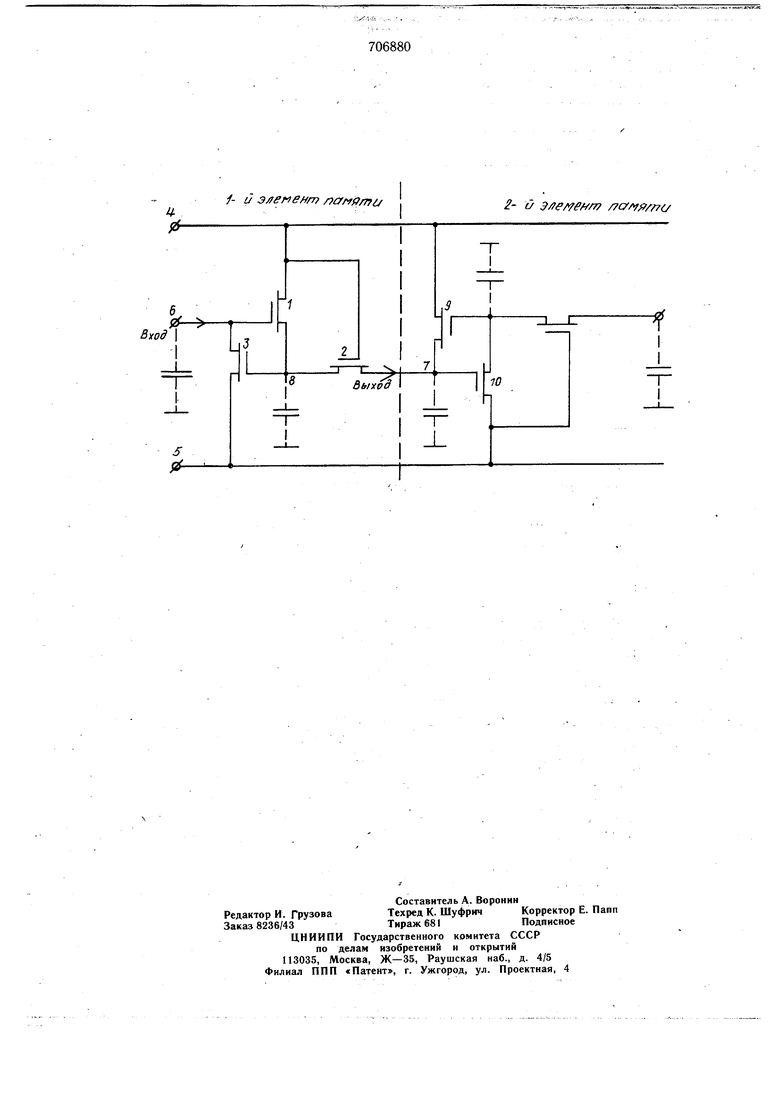

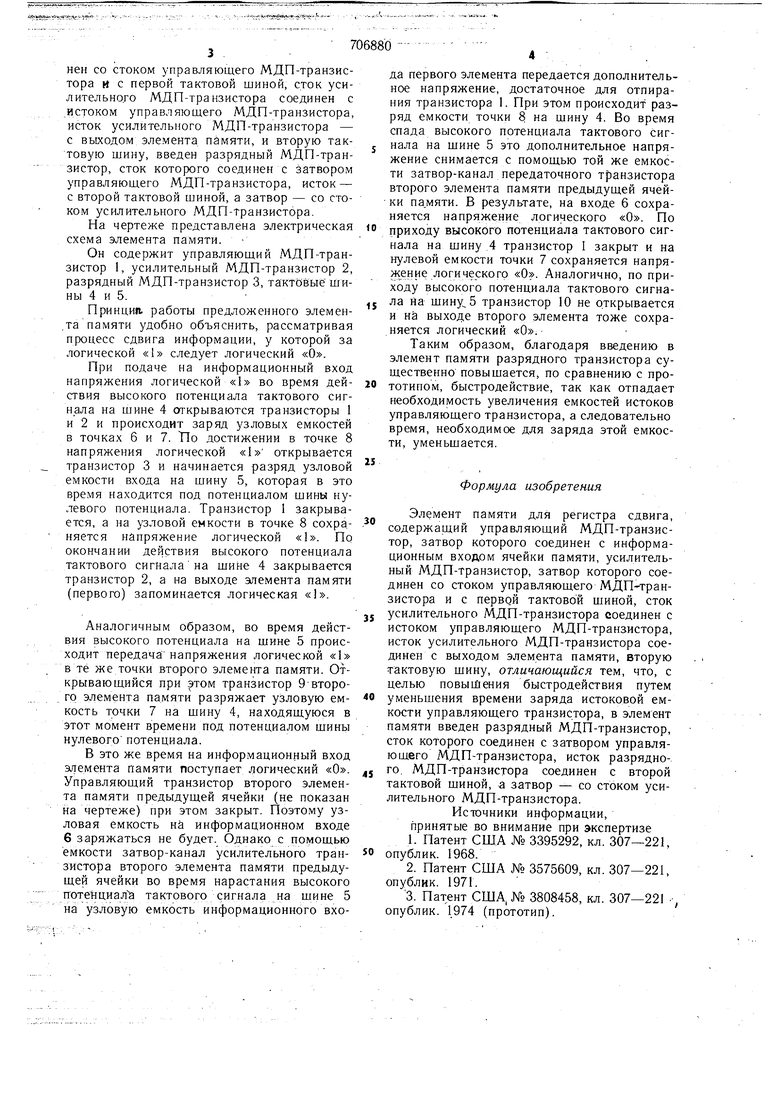

На чертеже представлена электрическая схема элемента памяти.

Он содержит управляющий МДП-транзистор 1, усилительный МДП-транзистор 2, разрядный МДП-транзистор 3, тактовые шины 4 и 5.

Принцил работы предложенного элемен.та памяти удобно объяснить, рассматривая процесс сдвига информации, у которой за логической «1 следует логический «О.

При подаче на информационный вход напряжения логической «1 во время действия высокого потенциала тактового сигнала на щине 4 открываются транзисторы 1 и 2 и происходит заряд узловых емкостей в точках 6 и 7. По достижении в точке 8 напряжения логической открывается транзистор 3 и начинается разряд узловой емкости входа на шину 5, которая в это время находится под потенциалом шины нулевого потенциала. Транзистор 1 закрывается, а на узловой емкости в точке 8 сохраняется напряжение логической «1. По окончании действия высокого потенциала тактового сигналана шине 4 закрывается транзистор 2, а на выходе элемента памяти (первого) запоминается логическая «1.

Аналогичным образом, во время действия высокого потенциала на шине 5 происходит передача напряжения логической «1 в те же точки второго элемента памяти. Открывающийся при этом транзистор 9-второго элемента памяти разряжает узловую емкость точки 7 на щину 4, находящуюся в этот момент времени под потенциалом шины нулевого потенциала.

В это же время на информационный вход элемента памяти поступает логический «О. Управляющий транзистор второго элемента памяти предыдущей ячейки (не показан на чертеже) при этом закрыт. Поэтому узловая емкость на информационном входе 6 заряжаться не будет. Однако с помощью емкости затвор-канал усилительного транзистора второго элемента памяти предыдущей ячейки во время нарастания высокого потенциала тактового сигнала на щине 5 на узловую емкость информационного входа первого элемента передается дополнительное напряжение, достаточное для отпирания транзистора 1. При этом происходит разряд емкости точки 8 на щину 4. Во время спада высокого потенциала тактового сигнала на щине 5 это дополнительное напряжение снимается с помощью той же емкости затвор-канал передаточного транзистора второго элемента памяти предыдущей ячейки па.мяти. В результате, на входе 6 сохраняется напряжение логического «О. По приходу высокого потенциала тактового сигнала на щину 4 транзистор 1 закрыт и на нулевой емкости точки 7 сохраняется напряжение логического «О. Аналогично, по приходу высокого потенциала тактового сигнала На транзистор 10 не открывается и на выходе второго элемента тоже сохраняется логический «О.

Таким образом, благодаря введению в элемент памяти разрядного транзистора существенно повышается, по сравнению с прототипом, быстродействие, так как отпадает необходимость увеличения емкостей истоков управляющего транзистора, а следовательно время, необходимое для заряда этой емкости, уменьшается.

Формула изобретения

Элемент памяти для регистра сдвига, содержащий управляющий МДП-транзистор, затвор которого соединен с информационным входом ячейки памяти, усилительный МДП-транзистор, затвор которого соединен со стоком управляющего МДП-транзистора и с первой тактовой шиной, сток усилительного МДП-транзистора соединен с истоком управляющего МДП-транзистора, исток усилительного МДП-транзистора соединен с выходом элемента памяти, вторую тактовую щину, отличающийся тем, что, с целью повышения быстродействия путем уменьщения времени заряда истоковой емкости управляющего транзистора, в элемент памяти введен разрядный МДП-транзистор, сток которого соединен с затвором управляющего МДП-транзистора, исток разрядного. МДП-транзистора соединен с второй тактовой щиной, а затвор - со стоком усилительного МДП-транзистора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-12-30—Публикация

1978-07-05—Подача