тч

ип

И1НIS 14 1314

П 1 Sn-i иЛ Вп В BO

315

Изобретение относится к вычислительной технике.

Целью изобретения является упрощение устройства.

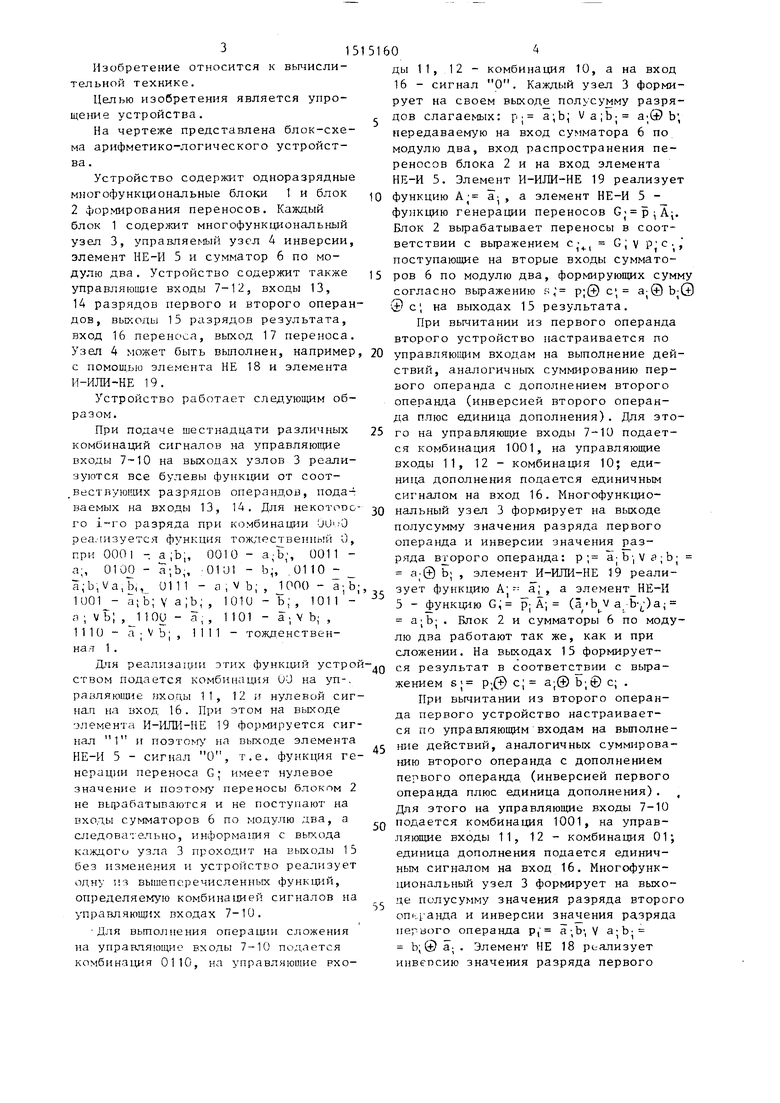

На чертеже представлена блок-схема арифметико-логического устройства .

Устройство содержит одноразрядные многофункциональные блоки 1 и блок 2 формирования переносов. Каждый блок 1 содержит многофункциональный узел 3, управляемый узел 4 инверсии, элемент НЕ-И 5 и сумматор 6 по модулю два. Устройство содержит также управляющие входы 7-12, входы 13, 14 разрядов первого и второго операндов, вьЕходы 15 рг13рядов результата, вход 16 переноса, выход 17 переноса. Узел 4 может быть выполнен, например с помощью злемепта НЕ 18 и элемента И-ИЛИ-НЕ 19.

Устройство работает следующим образом.

При подаче шестнадцати различных комбинаций сигналов на управляющие входы 7-10 на выходах узлов 3 реализуются все булевы функции от соот- веству101цих. разрядов операндов, подаваемых на входы 13, 14. Для некотооо- го i-ro разряда при комбинации UUi.-O реа. гизуется функция тождественный О, при 0001 -. а;Ь,, 0010 - а;Ь;, 0011 - а;, 0100 - К;Ь,, ;0101 - Ь;, , 01 10 - a;b,Va,b,, 0111 - а , V Ь; , 000 - i;b; 1001 - a;b; Y а;Ь;, 1010 - b;, 1011 - с ) ; vb; ,1 100 - а, , 1101 - а ; V Ь; , 1110- а ;Vb;, 1111 - тожд.енствен- нал 1 .

Для реализащги этих функций устройством подается комбинация 00 на уп-. рааляюип1е нходы 11, 12 и нулевой сиг- нап на вход 16. При этом на выходе элемента И-ИЛИ-ИЕ 19 формируется сигнал 1 и поэтом на выходе элемента НЕ-И 5 - сигнал О, т.е. функция генерации переноса G; имеет нулевое значение и поэтому переносы блоком 2 не вырабатываются и не поступают на входы сумматоров 6 по модулю два, а следова 1 ельно, информация с выхода каждого узла 3 проходит на выходы 15 без изменения и устройство реализует одну из вышеперечисленных функций, определяе1 ю комбинацией сигналов на управляющих входах 7-10.

Для выполнения операции сложения на yпpaвляюш le входы 7-10 подается комбинация 0110, на управляющие вхо

04

ды 11,12 - комбинация 10, а на вход 16 - сигнал О. Каждый узел 3 формирует на своем выходе полусумму разрядов слагаемых: р; а;Ь; Va;b; а;© Ь; передаваемую на вход сумматора 6 по модулю два, вход распространения переносов блока 2 и на вход элемента НЕ-И 5. Элемент И-ИЛИ-НЕ 19 реализует

функцию А а , а элемент НЕ-И 5 - функцию генерации переносов . Блок 2 вырабатывает переносы в соответствии с вьфажением , Gj v Р с., поступающее на вторые входы сумматоров 6 по модулю два, формирующих сумму согласно выражению ;; р;@ с; а;® @ с; на выходах 15 результата.

При вычитании из первого операнда второго устройство настраивается по управляющим входам на выполнение действий, аналогичных суммированию первого операнда с дополнением второго операнда (инверсией второго операнда плюс единица дополнения). Для этого на управляюш;ие входы 7-10 подается комбинация 1001, на управляющие входы 11, 12 - комбинация 10; единица дополнения подается единичным сигналом на вход 16. Многофункциональный узел 3 формирует на выходе полусумму значения разряда первого операнда и инверсии значения аз- ряда второго операнда: р ; a|b|Va;b; а.@ Ь; , элемент И-ИЛИ-НЕ 19 реализует функцию AJ- а;, а элемент НЕ-И 5 - функцию 0; р; А; ( а a;b; . Блок 2 и сумматоры 6 по модулю два работают так же, как и при сложении. На выходах 15 формируется результат в соответствии с выражением S j р;(Э с; а;® Ь;© с; .

При вычитании из второго операнда первого устройство настраивается по управляющим входам на выполнение действий, аналогичных суммированию второго операнда с дополнением первого операнда (инверсией первого операнда плюс единица дополнения). , Для этого на управляющие входы 7-10

подается комбинация 1001, на управляющие входы 11, 12 - комбинация 01; единица дополнения подается единичным сигналом на вход 16. Миогофунк- щюнальный узел 3 формирует на выходе полусумму значения разряда второго оп -л/анда и инверсии значения разряда первого операнда р, а;Ь , V а;Ь; Ь;@ а; . Элемент НЕ 18 реализует инвепсию значения разряда первого

слагаемого а;, а элемент И-ИЛИ-НЕ 19 - инверсию этой инверсии, в результате на выходе элемента И-ИЛИ-НЕ 19 реализуется функция А а;, а на выходе элемента НЕ-И 5 - функция (а; Ь; V а; Ь,) Ь;. . Блок 2 и сумматоры 6 по модулю два работают так же, как и при сложении. Нзг выходах 15 формируется результат в со- ответствии с выражением s; b @a .®C

Формула изобретения

Арифметико-логическое устройство, содержащее блок формирования переносов и одноразрядные многофункциональные блоки, каждый из которых содержи многофункциональный узел и сумматор по модулю два, выход которого соединен с выходом суммы данного одноразрядного многофункционального блока и является выходом результата соответствующего разряда устройства, первый вход сумматора по модулю два соединен с выходом многофункциональног узла того же одноразрядного многофункционального блока, информаи юн- ные входы многофункционального узла соединены с первым и вторым информационными входами соответствующего одноразрядного многофункционального блока и являются входами соответствующих разрядов первого и второго операндов устройства, управляющие входы многофункционального узла соединены с управляющими входами с первого по четвертый соответствующего одноразрядного многофункционального блока и являются управляющими входами соответ- ственно с первого по четвертый устройства, второй вход сумматора по модулю два соединен с входом переноса

Е к аы- IQ C ,

15151606

соответствующего одноразрядного функционального блока и для всеноразрядных многофункциональных

Q

5

0

5

Q

0

5

ков, кроме первого, соединен с выходами предыдущих разрядов блока формирования переносов, вход начального переноса которого соединен с входом переноса устройства и входом переноса первого одноразрядного многофункционального блока, выход последнего разряда блока формирования переносов соединен с выходом переноса устройства, выход многофункционального узла каждого одноразрядного многофункционального блока является выходом распространения переноса этого блока и соединен с входом распространения переноса соответствующего разряда блока формирования переносов, вход генерации переноса которого соединен с выходом генерации переноса соответствующего одноразрядного многофункционального блока, пятый и шестой управляющие входы которого соединены соответственно с пятым и шестым управляю-, щими входами устройства, отличающееся тем, что, с целью упрощения устройства, каждый одноразрядный многофункциональный блок содержит управляемый узел инверсии и элемент НЕ-И, входы которого соединены с выходами многофункционального узла и узла управляемой инверсии, а выход подключен к выходу генерации переноса этого одноразрядного многофункционального блока, первый информационный вход которого соединен с информационным входом узла управляемой инверсии, управляющие входы которого соединены с пятым и шестым управляющими входами этого одноразрядного многофункционального блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Комбинационный сумматор | 1979 |

|

SU849207A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| Устройство для умножения | 1978 |

|

SU896617A2 |

| Устройство для суммирования | 1979 |

|

SU864283A1 |

| Устройство для вычисления контрольного кода | 1982 |

|

SU1101826A1 |

| Многоразрядное устройство для сложения с контролем по четности | 1981 |

|

SU1035598A1 |

| Устройство для формирования остатка по модулю | 1989 |

|

SU1736006A1 |

Изобретение касается вычислительной техники. Целью изобретения является упрощение устройства. Устройство содержит одноразрядные многофункциональные блоки 1 и блок 2 формирования переносов. Каждый блок 1 содержит многофункциональный узел 3, управляемый узел 4 инверсии и сумматор по модулю два 6. 1 ил.

| Экспресс-информация | |||

| Вычислительная техника, 1972, № 23, с.23-38 | |||

| Мищенко В.А | |||

| и др | |||

| Многофункциональные автоматы и элементная база цифровых ЭВМ | |||

| М.: Радио и связь, 1981, с | |||

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1989-10-15—Публикация

1988-01-04—Подача