I I

«М f вн1.И

Изобретение относится к радиотехнике и связи и может быть использован в качестве образцового источника периодических сигналов любой формы с изменяющимися амплитудой и фазой по заданному закону.

Целью изобретения является расширение функциональных возможностей путем обеспечения независимой моду- лядии каждого из N генерируемых сигналов.

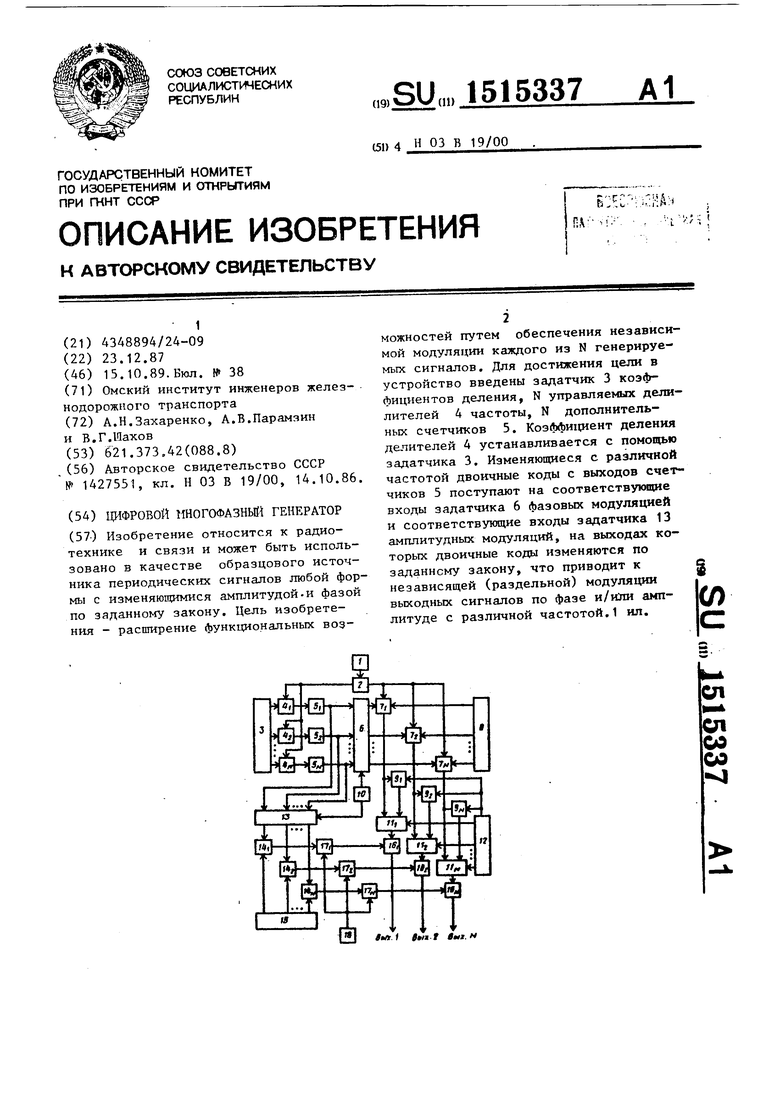

На чертеже представлена структурная электрическая схема цифрового многофазного генератора.

Цифровой многофазный генератор содержит опорный генератор 1, счетчик 2 задатчик 3 коэффициентов деления, первый, второй,..., N-й управляемые делители 41,4J,...,4 частоты, первый, второй,..., N-й дополнительные счетчики 5 ,5,j , . . ., , задатчик 6 фазовых модуляций, первый, второй,...,Н-й сумматоры 7 ,7 , , . . ,7f,, задатчик 8 фазовых сдвигов, первый, второй,...,К-й блоки 9т ,9 ,. . . ,9f сравнения кодов, задатчик 10 режимов, первый, второй,. N-й блоки 11,11,...,11„ оперативного запоминания, задатчик 12 формы сигналов, задатчик 13 амплитудных модуляций, первый, второй,...,N-й дополнительные суг-о аторы 14,14,...,

I4j, задатчик 15 амплитуд, первый, второй,...,N-й цифроаналоговые преобразователи 16 ,,16,...,16, первый, второй,...,N-u дополнительные цифро- аналоговые преобразователи 17,17, ..., 1 7 fJ и задатчик 18 масштаба.

Цифровой многофазный генератор ра ботает следующим образом.

Последовательность ш пульсов поступает с выхода опорного генератора 1 на счетный вход счетчика 2.Изменяющийся двоичный код поступает на первые входы первого, второго,..., . Н-го сумматора 7 ,7,. .. ,7,, на вторые входы которых с соответствующих выходов задатчика 8 подаются постоянные двoич ыe коды, обеспечивающие

относительный фазовый сдвиг между вы- 50 дуляции выходных сигналов по фазе

ходными сигналами. В задатчике 12 записаны коды мгновенных значений одного периода нескольких видов сигналов. Эти коды мгновенных значений требуемой формы сигнала переписьгеают- ее ся в.первьш, второй,...,N-й блоки 1 1 1, 11 2 , . . ., 1 Ifj по соответствующим адресам, коды которых с адресного выхода задатч1пса 12 поступают на вторые

и/или амплитуде с различной частот Формула изобретени

Цифровой многофазный генератор, держащий последовательно соединепн опорный генератор и счетчик, первы второй, ..., N-сумматоры, первый, рой,,..,N-й блоки оперативного зап

входы первого, второго, ..., N-ro блоков 9,9,,...,9. При совпадении кода адреса на адресном входе первого, второго, .. . ,JJ-ro блоков 11 , 11 2 , ...,11„ с кодом адреса на адресном выходе задатчика 12 на выходе соответственно первого, второго,...,N-ro блоков 9,,9,...,9 формируется импульс записи. Формирование выходных сигналов осуществляется путем циклического считывания записанной в первом, втором,...,N-M блоках 11,11,. 11м информации и последующего преоб

разования ее в аналоговую форму на первом, втором,...,N-M цифроаналого- вых преобразователях 1 6 ,, 1 6 , . . . , 1 6 |д. Амплитуда выходчьпс сигналов зависит от напряжения на выходах первого,второго, ... ,N-ro дополнительных цифро- аналоговых преобразователей 17,17 ,. ...,17, на информационные входы которых поступают двоичные коды с выходов первого, второго,...,N-го

дополнительных сумматоров 14,, 14, ...,14|, на опорные входы подается напряжение с выхода задатчика 18. На первые входы первого, второго,..., N-ro дополнительных сумматоров I4,l4,...,14jj поступают постоянные двоичные коды с соответствующих выходов задатчика 15. Включение задатчика 6 и задатчика 13 осуществляется с помощью задатчика 10. Последов ательность импульсов с дополнительного счетчика 2 поступает на счетные входы первого, второго, ...,Н-го управляемых делителей 4,, 4,... ,4 коэффициент, деления которьЪс

устанавливается с помощью задатчика 3. Изменяющиеся с различной частотой Г двоичные коды с выходов первого,второго, ... ,N-ro дополнительных счетчиков 5 , ,5,... ,5 1 поступают на соответствующие входы задатчика 6 и соответствующие входы задатчика 13, на выходах которых двоичные коды изменяются по заданному-закону, что приводит к независящей (раздельной) модуляции выходных сигналов по фазе

и/или амплитуде с различной частотой. Формула изобретения

Цифровой многофазный генератор,содержащий последовательно соединепные опорный генератор и счетчик, первый, второй, ..., N-сумматоры, первый, второй,,..,N-й блоки оперативного запоминания, первый, второй,...,N-ft блоки сравнения кодов, первый, второй, ...,Н-й цифроаналоговые преобразователи, первый, второй,...,Н-й дополни- тельные сумматоры, первый, второй,..., N-й дополнительные цифроаналоговые преобразователи, задатчик фазовых модуляций, задатчик фазовых сдвигов.

ных цифроаналоговых преобразователе первый, второй,...,Ы-й выходы задат чика амплитуд соединены с первыми входами соответственно первого, вто рого, ... ,N-ro дополнительных сумматоров, вторые входы которых соедине ны с соответствующими выходами зада чика амплитудных модуляций, выходы

задатчик формы сигналов, задатчик амп-ю первого, второго,...,N-ro дополниных цифроаналоговых преобразователей, первый, второй,...,Ы-й выходы задат- чика амплитуд соединены с первыми входами соответственно первого, второго, ... ,N-ro дополнительных сумматоров, вторые входы которых соединены с соответствующими выходами задат- чика амплитудных модуляций, выходы

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой многофазный генератор | 1986 |

|

SU1427551A1 |

| Инфузионный насос | 1985 |

|

SU1279635A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Дробно-пропорциональный преобразователь частот | 1987 |

|

SU1626383A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

| СПОСОБ ПЕРЕДАЧИ ДОПОЛНИТЕЛЬНОЙ ИНФОРМАЦИИ В СИСТЕМЕ УКВ-ВЕЩАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2030835C1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1642585A1 |

Изобретение относится к радиотехнике и связи и может быть использовано в качестве образцового источника периодических сигналов любой формы с изменяющимися амплитудой и фазой по заданному закону. Цель изобретения - расширение функциональных возможностей путем обеспечения независимой модуляции каждого из N генерируемых сигналов. Для достижения цели в устройство введены задатчик 3 коэффициентов деления, N управляемых делителей 4 частоты, N дополнительных счетчиков 5. Коэффициент деления делителей 4 устанавливается с помощью задатчика 3. Изменяющиеся с различной частотой двоичные коды с выходов счетчиков 5 поступают на соответствующие входы задатчика 6 фазовых модуляций и соответствующие входы задатчика 13 амплитудных модуляций, на выходах которых двоичные коды изменяются по заданному закону, что приводит к независящей (раздельной) модуляции выходных сигналов по фазе и/или амплитуде с различной частотой. 1 ил.

литудньбс модуляций, задатчик амплитуд и задатчик масштаба, причем выход счетчика соединен с первыми входами первого, второго, ... ,N-го сумматоров, выходы которых соединены с первыми входами соответственно первого, второго, ... ,N-ro блоков сравнения кодов и с адресными входами соответственно первого, второго, N-ro блоков оперативного запоминания, первый, второй, ...,М-ый выходы задатчика фазовых сдвигов соединены с вторыми входами соответственно первого, второго,..., N-ro сумматоров, третьи входы которых соединены с соответствующими вьгх:о-25 симой модуляции каждого из N генеридами залртчика фазовых модуляций, первый, второй,...,Н-й информационные выходы задатчика формы сигналов соединены с информационными входами соответственно первого, второго ,..,, N-ro блоков оперативного запоминания, входы записи которых соединены с выходами соответственно первого, второго, N-ro блоков сравнения кодов, адресный выход задатчика формы сигналов соединен с вторыми входами первого-, второго,...,N-ro блоков сравнения кодов, выходы первого, второго, ...,N-ro блоков оперативного запоминания соединены с информационными вхо-дд счетными входами соответственно пер

вого, второго,...,N-ro дополнительных счетчиков, счетные входы первого, второго,...,N-ro управляемых де лителей частоты соединены с дополни тельным выходом счетчика.

дами соответственно первого, второго,..., N-ro цифроаналоговых преобразователей, опорные входы которых соединены с выходами соответственно пер- .вого, второго,...,N-ro дополнительтельных сумматоров соединены с ин- формационными входами соответственно первого, второго,...,N-ro дополнительных цифроаналоговых преобразователей, опорные входы которых соединены с выходом задатчика масштаба, управляющий вход задатчика фазовых модуляций соединен с первым выходом задатчика режимов, второй выход которого соединен с управляющим входом задатчика амплитудных модуляций, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения незави0

5

руемых сигналов, введены задатчик коэффициентов деления, nepBbrt,второй,...,N-й управляемые делители частоты и первый,второй,...,N-й дополнительные счетчики, выходы которых соединены с соответствующими входами задатчика фазовых модуляций и соответствующими входами задатчика амплитудных модуляций, первый, BTopo,N-A выходы задатчика коэффициентов деления соединены с информационными входами соответственно первого,второго, ..., -го управляемых делителей частоты, выходы которых соединены со

счетными входами соответственно пер

вого, второго,...,N-ro дополнительных счетчиков, счетные входы первого, второго,...,N-ro управляемых делителей частоты соединены с дополнительным выходом счетчика.

| Цифровой многофазный генератор | 1986 |

|

SU1427551A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-15—Публикация

1987-12-23—Подача