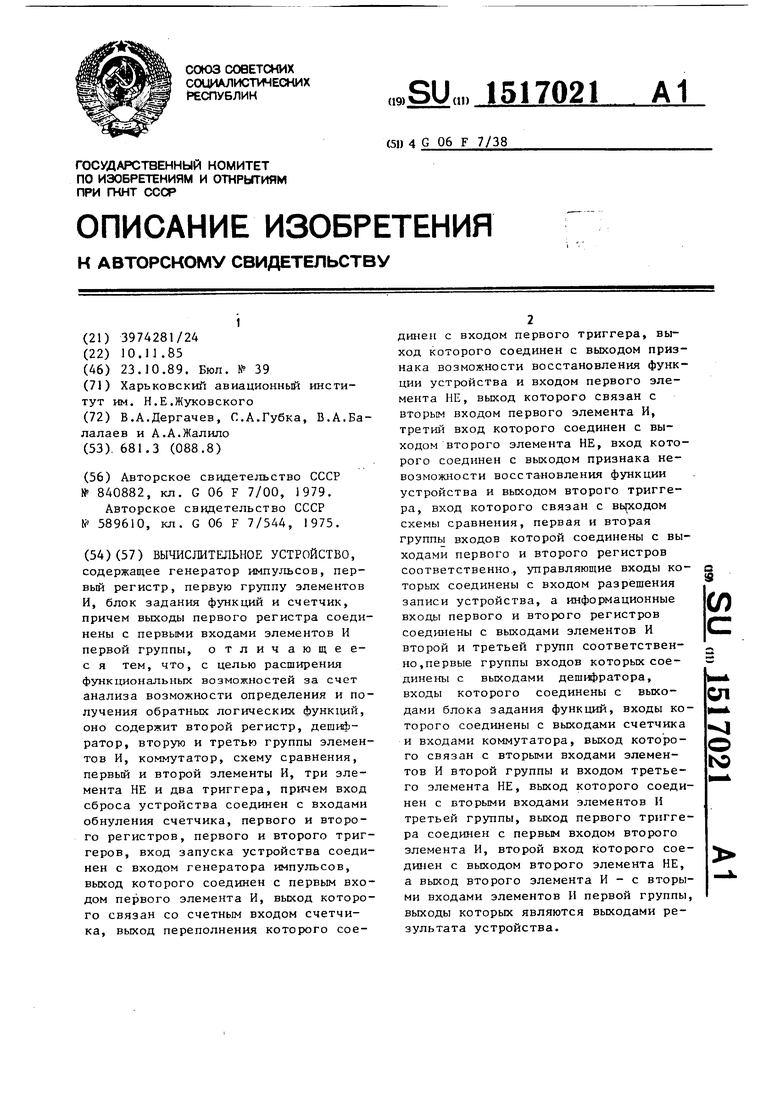

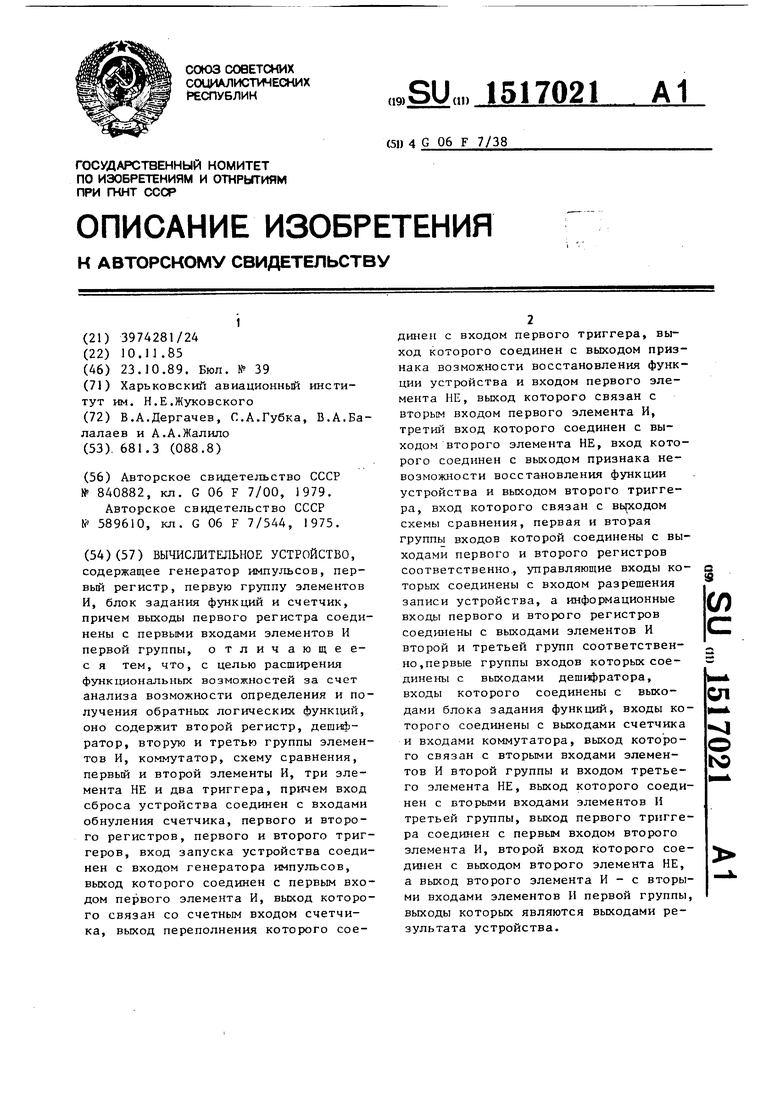

Изобретение относится к автоматике и вычислительной технике и предназначено для определения обратных логических (булевьк) функций при проектировании систем автоматизированного проектирования технических средств контроля, при решении логико-комбинаторных задач, для реализации макрокоманды определения обратных булевых функцш в специализированных процессорах,г

Цель изобретения - расширение функциональных возможностей устройства за счет анализа возможности опре- деления и получения обратных логических фуПКЦ1Ш.

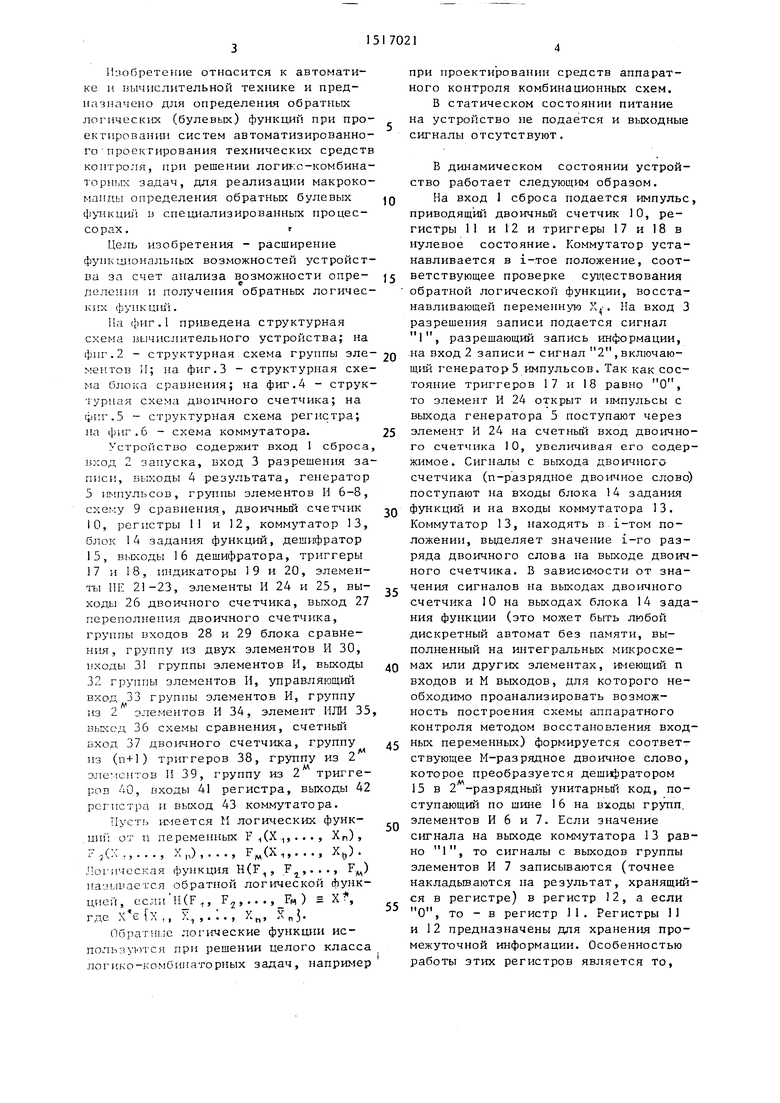

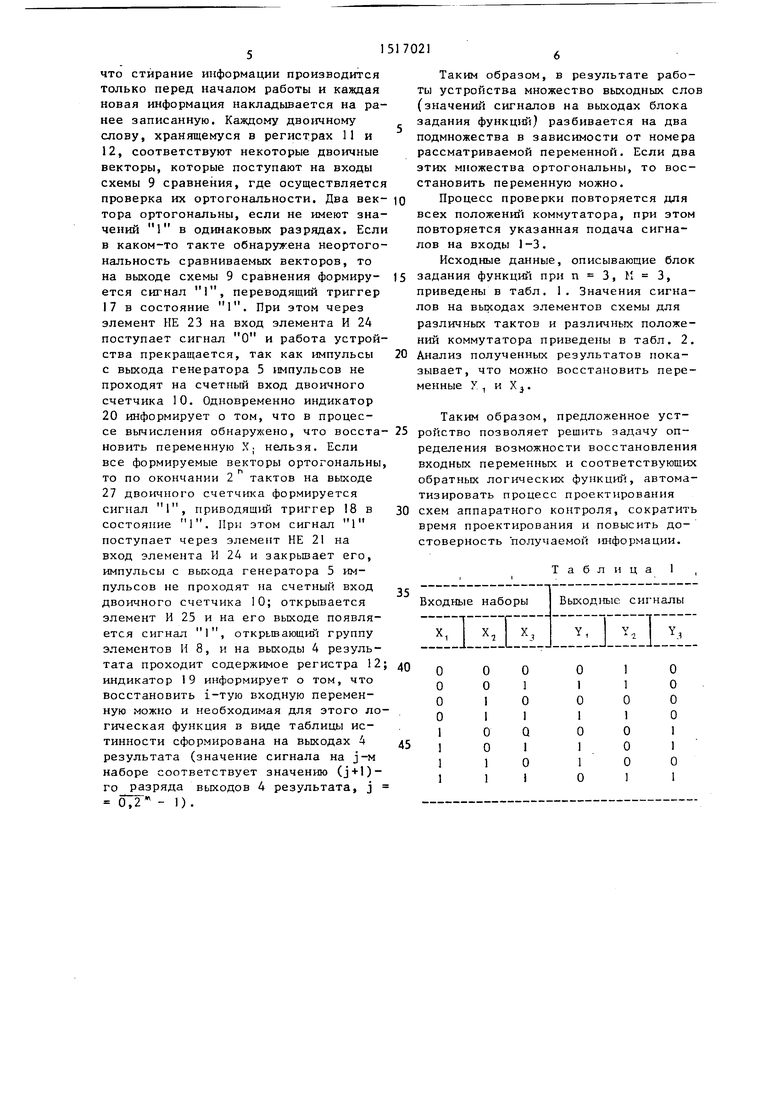

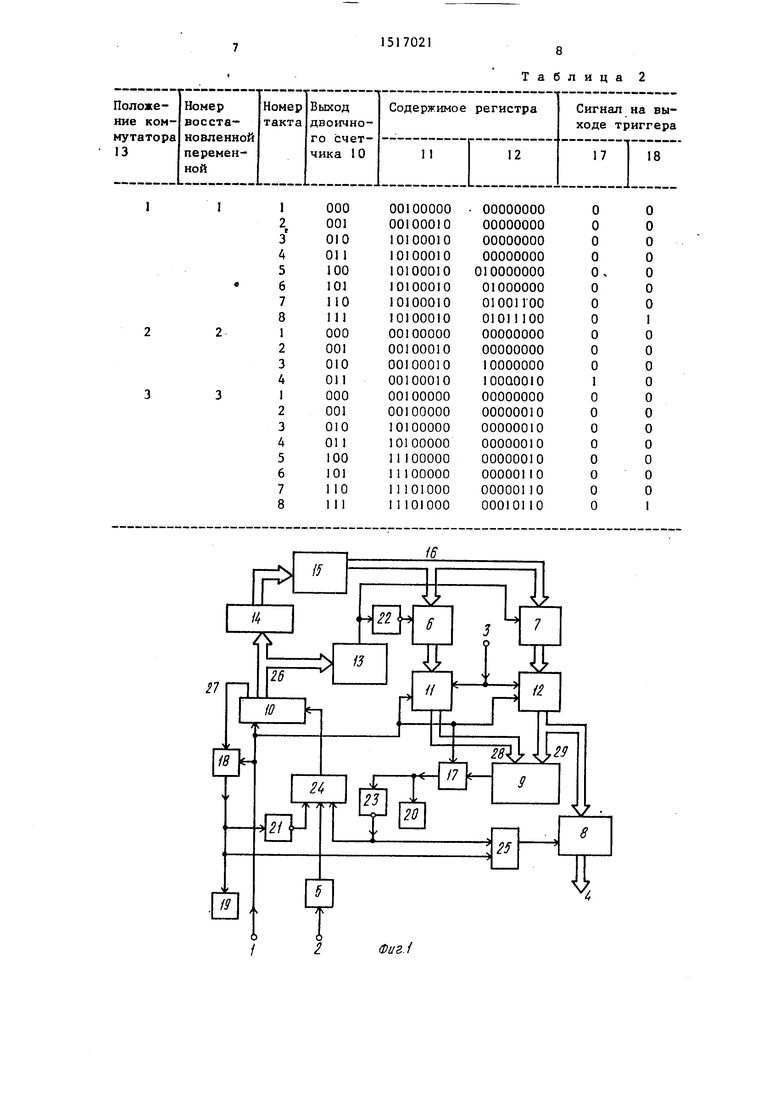

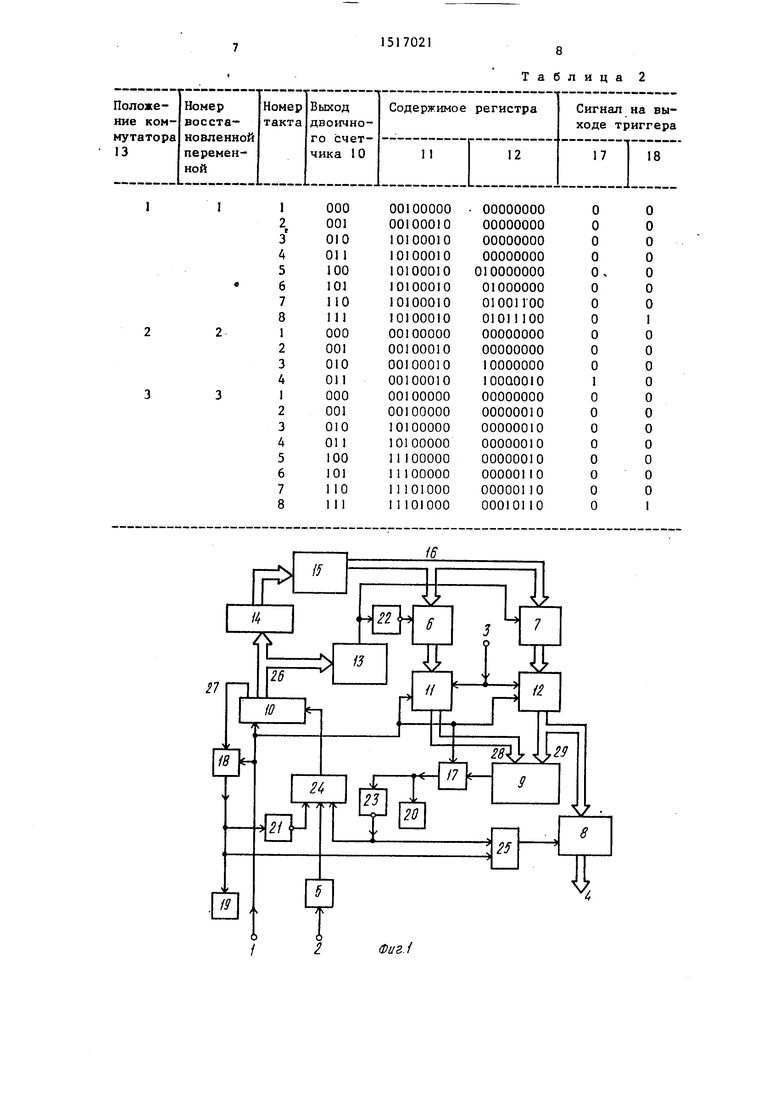

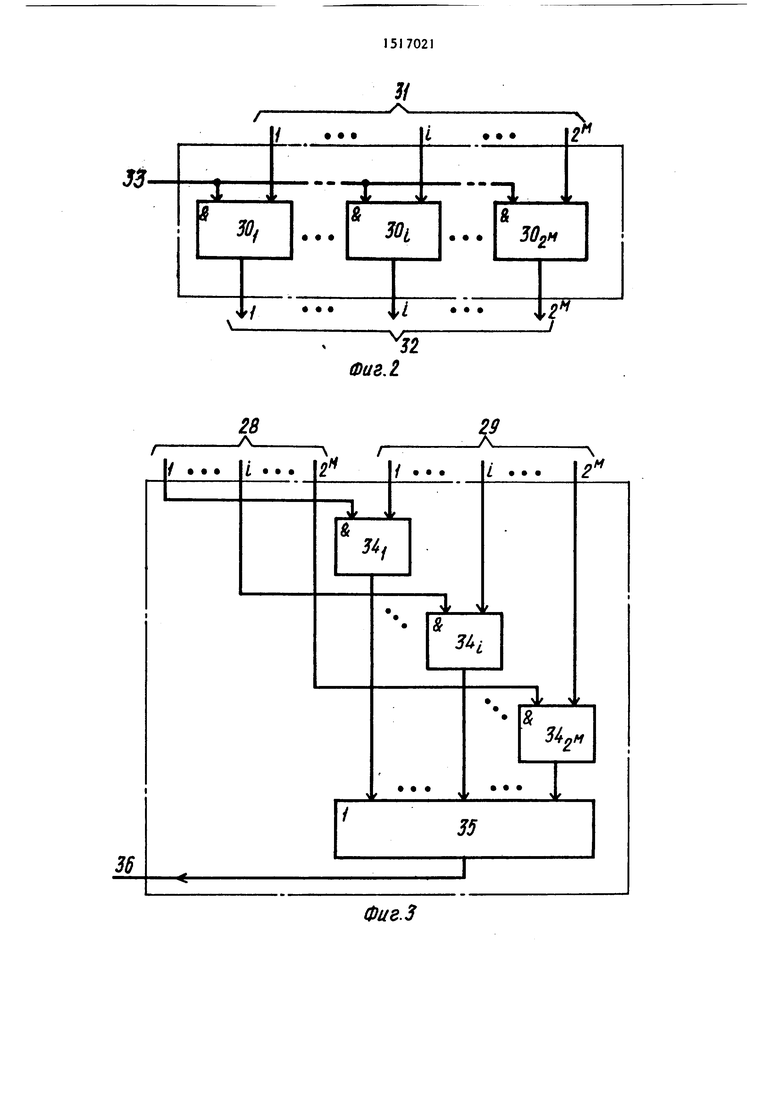

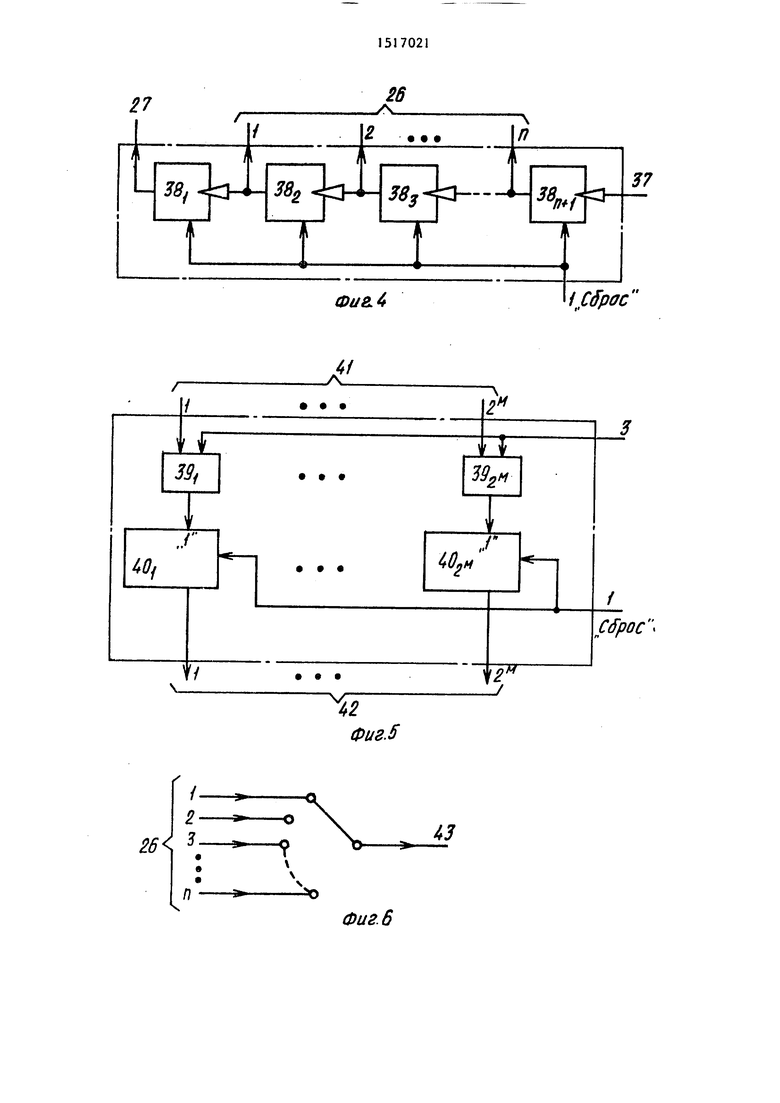

Па фиг.1 приведена структурная схема вычислительного устройства; на фиг.2 - структурная,схема группы эле- ментов И; на фиг.З - структурная схема блока сравнения; на фиг.4 - структурная схема двоичного счетчика; на фиг.5 - структурная схема регистра; на 11 иг.6 - схема коммутатора.

Устройство содержит вход 1 сброса вход 2 запуска, вход 3 разрешения записи, выходы 4 результата, генератор 5 мпульсов, группы элементов И 6-8, схему 9 сравнения, двоичный счетчик 10, регистры 11 и 12, коммутатор 13, блок: 14 задания функций, дешифратор 15, выходы 16 дешифратора, триггеры 17 и 18, индикаторы 19 и 20, элемен- 1ъ НЕ 21-23, элементы И 24 и 25, вы- ходы 26 двоичного счетчика, выход 27 переполнепия двоичного счетчика, группы входов 28 и 29 блока сравнения, группу из двух элементов И 30, входы 31 группы элементов И, выходы 32 группы элементов И, управляющий вход 33 группы элементов И, группу из 2 элементов И 34, элемент ИЛИ 35 выход 36 схемы сравнения, счетньп вход 37 двоичного счетчика, группу пз (п+1) триггеров 38, группу из 2 элементов И 39, группу из 2 триггеров 40, входы 41 регистра, выходы 42 рсг пстра и выход 43 коммутатора.

Пусть имеется Н логических функ- ПИ от и переменных РДХ,..., Хп) F.jC/i.,..., X I,) , . . . , Fj(Xi,..., Xj.,) . Логическая функция H(F, F,..., F,) на - ывается обратной логической функцией, если iKF , F,,..,FH) X , где ,, X,,.:., X,, X,J.

Обратные логические функции ис- пользу 1тся при решении целого класса логико-комбинаторных задач, например

при проектираван1П1 средств аппаратного контроля комбинационных схем. В статическом состоянии питание на устройство не подается и выходные сигналы отсутствуют.

В динамическом состоянии устройство работает следующим образом.

На вход 1 сброса подается импульс приводящий двоичный счетчик 10, регистры 11 и 12 и триггеры 17 и 18 в нулевое состояние. Коммутатор устанавливается в i-Toe положение, соответствующее проверке сугцествования обратной логической функции, восстанавливающей перемепную . На вход 3 разрешения записи подается сигнал 1, разрешающий запись информации, па вход 2 записи - сигнал 2,включающий генератор5 импульсов. Так как состояние триггеров 17 и 18 равно О, то элемент И 24 открыт и импульсы с выхода генератора 5 поступают через элемент И 24 на счетный вход двоичного счетчика 1 О, увеличивая его содержимое. Сигналы с выхода двоичного счетчика (п-разрядное двоичное слово) поступают на входы блока 14 задания функций и на входы коммутатора 13. Коммутатор 13, находять в 1-том положении, выделяет значение i-ro разряда двоичного слова на выходе двоичного счетчика. В зависимости от значения сигналов на выходах двоичного счетчика 10 на выходах блока 14 задания функции (это может быть любой дискретный автомат без памяти, выполненный на интегральных микросхемах или других элементах, имеющий п входов и М выходов, для которого необходимо проанализировать возможность построения схемы аппаратного контроля методом восстановления входных переменных) формируется соответствующее М-разрядное двоичное слово, которое преобразуется дешифратором

1 сО

15 в / -разрядньм унитарньи код, поступающий по шине 16 на входы групп, элементов И 6 и 7. Если значение сигнала на выходе коммутатора 13 равно 1, то сигналы с выходов группы элементов И 7 записываются (точнее накладьшаются на результат, хранящийся в регистре) в регистр 12, а если О, то - в регистр 11. Регистры 11 и 12 предназначены для хранения промежуточной информации. Особенностью работы этих регистров является то.

что стирание информации производится только перед началом работы и каждая новая информация накладьшается на ранее записанную. Каждому двоичному слову, хранящемуся в регистрах 11 и 12, соответствуют некоторые двоичные векторы, которые поступают на входы схемы 9 сравнения, где осуществляется проверка их ортогональности. Два век- тора ортогональны, если не имеют значений 1 в одинаковых разрядах. Если в каком-то такте обнаружена неортогональность сравниваемых векторов, то

Таким образом, в результате работы устройства множество выходных сло (значений сигналов на выходах блока задания функций) разбивается на два подмножества в зависимости от номера рассматриваемой переменной. Если два этих множества ортогональны, то восстановить переменную можно.

Процесс проверки повторяется для всех положений коммутатора, при этом повторяется указанная подача сигналов на входы 1-3.

Исходные данные, описывающие блок

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

| Устройство для распознавания на линейность булевых функций | 1988 |

|

SU1552169A1 |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Устройство для вычисления булевых производных | 1987 |

|

SU1481793A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для обучения | 1987 |

|

SU1580423A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

Цель изобретения - расширение функциональных возможностей за счет анализа возможности определения и получения обратных логических функций. Устройство содержит генератор импульсов, первый регистр, первую группу элементов И, блока задания функций и счетчик. В него дополнительно введены второй регистр, дешифратор, вторая и третья группы элементов И, коммутатор, схема сравнения, первый и второй элементы И, три элемента НЕ и два триггера.

на выходе схемы 9 сравнения формиру- 15задания функций при п 3, М 3,

ется сигнал 1, переводящий триггерприведены в табл. 1. Значения сигна17 в состояние 1. При этом черезлов на выходах элементов схемы для

элемент НЕ 23 на вход элемента И 24различных тактов и различных положепоступает сигнал О и работа устрой-ний коммутатора приведены в табл. 2.

20Анализ полученных результатов показывает, что можно восстановить переменные У

и X,

ства прекращается, так как импульсы

с выхода генератора 5 импульсов не

проходят на счетный вход двоичного

счетчика 10. Одновременно индикатор

20 информирует о том, что в процес- Таким образом, предложенное устсе вычисления обнаружено, что восста- 25 ройство позволяет решить задачу опновить переменную Xj нельзя. Если ределения возможности восстановления

все формируемые векторы ортогональны,

то по окончании 2 тактов на выходе

входных переменных и соответствующих обратных логических функций, автоматизировать процесс проектирования схем аппаратного контроля, сократить время проектирования и повысить достоверность получаемой информации.

27 двоичного счетчика формируется сигнал 1, приводящий триггер 18 в состояние 1. При этом сигнал 1 поступает через элемент НЕ 21 на вход элемента И 24 и закрьшает его, импульсы с выхода генератора 5 импульсов не проходят на счетный вход двоичного счетчика 10; открывается элемент И 25 и на его выходе появляется сигнал 1, открьюающий группу элементов И 8, и на выходы 4 результата проходит содержимое регистра 12 индикатор 19 информирует о том, что восстановить i-тую входную переменную можно и необходимая для этого логическая функция в виде таблицы истинности сформирована на выходах 4 результата (значение сигнала на j-м наборе соответствует значению (j+1)- го разряда выходов 4 результата, j 072 - 1) .

менные У

и X,

входных переменных и соответствующих обратных логических функций, автоматизировать процесс проектирования схем аппаратного контроля, сократить время проектирования и повысить достоверность получаемой информации.

Таблица 1 ,

наборы

Выходные сигналы

ЕП- ; 1- :- -:1-1- -1

0 5

0

О О

о о 1 1 1 1

о о

I 1

о о 1 1

о 1

о 1

Q

1 О

1

о 1

о 1

о 1 1 о

1

о 1

о о о

о о о о

о 1

Таблица 2

Фие.З

27

26

УЧ

Фив. 5

| Устройство для определения значений буле-ВыХ фуНКций | 1979 |

|

SU840882A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления обратных функций | 1975 |

|

SU589610A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1985-11-10—Подача