Изобретение относится к импульсной и вычислительной технике, в частности к счетчикам, и может быть применено в устройствах промышленной автоматики и вычислительной техники.

Цель изобретения - повьппение эксплуатационной отказоустойчивости двоично-десятичного счетчика.

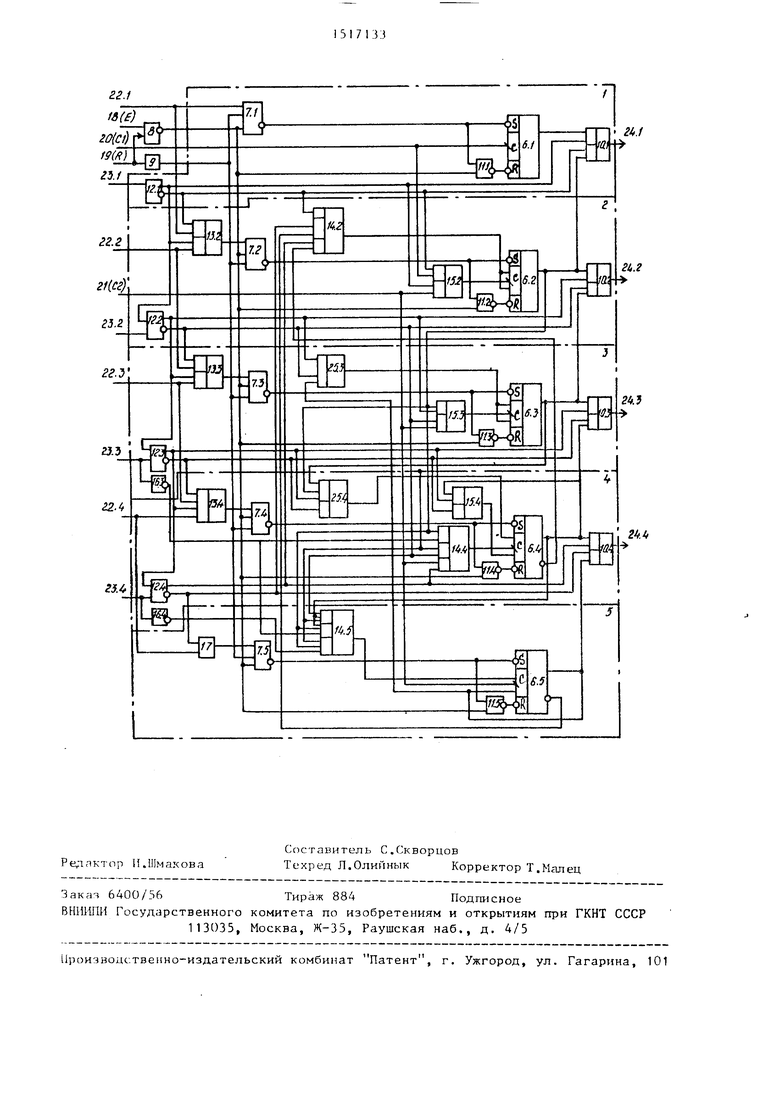

На чертеже приведена функциональная схема двоично-десятичного счетчика.

Двоично-десятичный счетчик содержит основные разряды 1-4, резервный

разряд 5, триггеры 6 „1-6 „5 разрядов, первые элементы И-НЕ 7.1-7.5 разрядов, элемент И-НЕ 8, элемент ИЛИ 9, третьи элементы 2И-ИЛИ 10.1-10.4 разрядов , вторые элементы И-НЕ I I . 1-1 1 . 5 разрядов , элементы И/И-НЕ 12.1-12.4 разрядов, первые элементы 2И-ИЛИ 13.2-13,4 разрядов, элементы ЗИ-ИЛИ 14,2,14,4 и 14,5 второго, четвертого и резервного разрядов, вторые г лементы 2И-ИЛИ 15.2-15.4 разрядов, элементы НЕ 16.3 и 16о4 третьего и четвертого разрядов, элемент И 17 резервного разря00

00

дл, лход 1 рлзрегаения предварительной установки, вход 19 установки в о, первый 20 и второй 21 синхро- ях-чды, ипформапионные входы 22.1-22 Г1(.ед1 арительной установки, вхо- дм 23.1-23.4 запрещения работы рач- ридор и информационные выходы 2А.11 /, , . ч . ч .

Вход 18 разрешения предваритель- лсп установки соединен с первым ii;iOM элемента 8, второй вход которого соединен с входом элемента И 111 9 и входом 19 установки в О. Перный синхровход 20 соединен со сли тным входом триггера 6.1 и вхо- jij ; .1 мервой группы входов элемента 2 -ii iil 15,2, второй синхровход 21 - г p-jonp.f.iH второй группы входов эле- г рптои 2И-11ЛИ 15.2 и 15.3, входом ) группы входов элемента ЗЧ-1 ЛИ 1 4 , 4 и со счетшз1м входом триг- Р 1 6.5. Вход 22.1 предварительной устпионки первого разряда соединен jr гч .одом элемента И-НЕ 7.1 и входом 1:1-п ой группы входов элемента 211- И.ПИ 13,2, вход 22.2 предварительной ;.( тл(Г:вки второго разряда - с вхо- ,ii;i: 1 юрой группы входов элемента И-ИМИ 13.2 и входом первой группы -;х(м;г1Т гхаемента 2И-ИЛИ 13.3, вход / . 3 гр едларительной установки тре- .п L4 o разряда - с входом второй гру Г: 1 Г .ходов 2И-ИЛИ 13.3 и г чодом первой группы входов элемен- Т- ZH-inil 13.4, а вход 22.4 предварительной установки четвертого раз- р,чда - с входом второй группы входо элемента 2П-ИЛИ 13.4 и входом элеме тг, Г 17. Вход 23.1 запрещения рабо тг:1 iiepBoro разряда соединен с вхо- лом злег-ента И/И-НЕ 12.1, вход 23.2 ;1ЛИ| с1;|;с11ил работы второго разряда - с вторым входом элемента И/И-НЕ 12. ч:;од 23.3 запрещения работы третьег разряда - с вторым входом элемента И/Г1-НТ 12.3 и входом элемента НЕ 1 6 . чч.хп 23,4 запрещения работы четвертго разряда - с вторым входом элемен i л ;/H-HF 12.4 и входом элемента

1 1 6 , 4 ,

и.:--: од

i:c:i.

. J--7.5 I ;.псмсм;тл егодлми

IS ПОР .

элемента И-НЕ 8 устройства с входами элементов И-НЕ ; П. 1-1 1.5 разрядов. Выход

ПИ 9 соединен с вторыми 1: сментов И-НЕ 7.1-7.5 раз7.5 п я

:лы первых элементов И-НЕ 7.J- рядов соединены с инверсными

S-входами триггеров 6 „1-6.5 одноименных разрядов и с первыми входами вто- piiix элементов И-НЕ 11.1-11 „5 соответствующих разрядов, выходы которых соединешэ с инверсными R-входами триггеров 6.1-6.5 одноименных им разрядов.

Прямой выход элемента И/И-НЕ 12.1 соединен с входом первой группы входов элемента 2И-ИЛИ 10,1, входами второй группы входов элементов 2И-ИЛИ 15.2 и 13.2 и входом элемента И/И- НЕ 12.2, а инверсный - с входом первой группы входов элемента 2И-ИЛИ 13.2, входом первой группы входов элемента ЗИ-ИЛИ 14,2, входом первой группы входов элемента 2И-Ш1И 15,2 и входом второй группы входов элемента 2И-ИЛИ 10J,

Прямой выход элемента И/И-НЕ 12,2. соединен с входами первой групгпз входов элементов 2И-ИЛИ 10,2 и 15.3, входом первой группы входов элемента 2И-ИЛИ 25,3, входом второй группы входов элемента 2И-ИЛИ 13,3 и входом элемента И/И-НЕ 12,3, а инверсный - с входами второй группы входов элементов 2И-ИЛИ 10,2 и 15,3, входом второй групны входов элемента ЗИ-ИЛИ 14,4, входом первой групп входов элемента ЗИ-ИЛИ 14,5, входом второй группы входов элемента 2И- 1ШИ 25.3 и входом первой группы входов элемента 2И-ИЛИ 13.3,

0

0

5

Прямой выход элемента И/И-НЕ 12,3 соединен с входами первой группы входов элементов 2И-ИЛИ 10,3, 15,4 и 25,4, входом второй группы входов элемента 2И-11ПИ 13.4 и входом элемента И/И-НЕ 12.4, а инверсный - с входами второй группы входов элементов 2И- ИЛИ 10,3, 15,4 и 25о4 и входом пер- 5 вой группы входов элемента 2И-Шта13.А, Выход элемента НЕ 16,3 соединен с входом первой группы входов элемента ЗИ-ИЛИ 14,4 и входом второй группы входов элемента ЗИ-ИЛИ 14,5,

Прямой выход элемента И/И-11ПИ 12,4 соединен с входом первой группы входов элемента 2И-ИЛИ 10,4 и входами третьей группы входов элементов ЗИ- ИЛИ 14„4 и 14,2, а инверсный - с входами второй группы входов элементов 2И-ИЛИ 10,4 и ЗИ-ИЛИ 14,2 и входом элемента И 17, Выход элемента НЕ 16,4 соединен с входом третьей группы входов элемента ЗИ-ИЛИ 14.5,

5

Выходы элементов 2И-ИЛИ 13.2-13. соединены с первыми входами соответвующих им элементов И-НЕ 7.2-7.4. Выход элемента И 17 соединен с первым входом элемента И-НЕ 7.5, выход элемента ЗИ-ИЛИ 14.2 - с входами разрешения счета триггера 6.2, выход элемента 2И-ИЛИ 25.3 - с входами разрешения счета триггера 6.3, выход элемента 2И-ИЛИ 25.4 - с пер- вьи входом разрешения счета триггера 6.4, выход элемента i 2И-ИЛИ15.4 с вторым входом разрешения счета триггера 6.4, выход элемента ЗИ- ИЛИ 14.5 - с первым входом разрешения счета триггера 6.5, второй вход разрешения счета которого соединен с прямым выходом триггера 6.5.

Выход элемента 2И-ИЛИ 15.2 сое- динен со счетным входом триггера 6. выход элемента 2И-ИЛИ 15.3 - со счетным входом триггера 6.3, выход элемента ЗИ-ИЛИ 14.4 - со счетным входом триггера 6.4.

Прямой выход триггера 6.1 соединен с входом первой группы входов элемента 2И-ИЛИ 10.1, прямой выход триггера 6.2 - с входом второй группы входов элемента 2И-ИЛИ 10.1, входами первой группы входов элементов 2И-ИЛИ 10.2, 15.3, 25.4 и элемента ЗИ-ИЛИ 14.4 и входами второй и третьей групп входов элемента ЗИ-ИЛИ 14.5, прямой выход тригге- ра 6„3 - с входом второй группы входов элемента 2И-ИЛИ 10.2, входами первой группы входов элементов 2И-ИЛИ 10.3 и 25.4, входом второй группы входов элемента ЗИ-ИЛИ 14.4 и входами первой и третьей групп входов элемента ЗИ-ИЛИ 14.5,

Прямой выход триггера 6.4 соединен с входом второй группы входов элемента 2И-Ш1И 10.3, входами первой группы входов элементов 2И-ИЛИ 15.4 и 10.4 и с входами первой и второй групп входов элемента ЗИ- ИЛИ 14.5, а инверсный - с входом третьей группы входов элемента ЗИ- ИЛИ

Прямой выход триггера 6.5 соединен с входом второй группы входов элемента 2И-ИЛИ 10.4, вторым входом разрешения счета триггера 6.5 и входом второй группы входов элемента 2И-И 2И-ИЛИ 25. 3, а инверсный - с входом второй группы входов элемента ЗИ-ИЛИ 14.2

336

Выходы элементов 2И-ИПИ 10.1-10.4 являются соответствугацими информационными выходами 24.1-24.4 счетчика.

Вход 18 разрешения предварительной установки позволяет начинать счет с произвольной цифры или от нуля до девяти. Такая организация дает возможность использовать двоично-десятичный счетчик в режиме 4-разрядного регистра-защелки.

На входы 22 и 21 подаются импульсы счета, При использовании двоично- десятичного счетчика по его назначению вход 21 соединяют с выходом 24.1. При использовании счетчика в качестве делителя выход 24.1 используется для деления частоты на два, а по входу 22 производится деление частоты на пять и т.д.

На входы 18.1-18о4 подается код числа, в которое предварительно устанавливается двоично-десятичный счетчик перед началом счета.

Входы 23.1-23.4 используются для управления работоспособной структурой двоично-десятичного счетчика. При отказе какого-либо из основных разрядов на соответствующий вход подается сигнал логического О. В случае исправности на соответствующих управляющих входах 23.1-23.4 присутствует сигнал логической 1.

Элементы И-НЕ 8 и ИЛИ 9 предназначены для установки режимов работы двоично-десятичного счетчика при установке его в О и при предварительной установке какого-либо числа перед началом счета.

Элементы И-НЕ 7.1-7.5 и 11.1-11.5 осуществляют реализацию функции входной логики при проведении установки в исходное состояние счетчика.

Элементы 2И-ИЛИ 10.1-10.4 предназначены для коммутации сигналов с прямых выходов триггеров 6.1-6.4 на выходы 24.1-24.4 в соответствии с состоянием сигналов на управляющих входах 23.1-23.4, т„е. в соответствии с исправным (неисправным) состоянием основных разрядов счетчика.

Элементы И/И-НЕ 12.1-12.4 формируют управляющие сигналы для коммутации внутренних цепей счетчика в зависимости от состояний управляющих сигналов на входах 23.1-23.4.

Элементы 2И-ИЛИ 13.2-13.4 и эЛе- мент И 17 служат для осуществления

7151

коммутации информационных цепей пррд- установа с входов 22.1-22,А на установочные входы триггеров 6.1-6.5.

Элементы 2И-ИЛИ 15.2, 15.3 и эле- мент ЗИ-ИЛИ 14.4 осуществляют комму- топию логической цепи счета импульсов в зависимости от исправного (неисправного) состояния основных разрядов .

:)лементы ЗИ-ИЛИ 14.2, 14.5 и 2И- 11ПИ 25.3, 25.4 предназначены для формт рования управляющих сигналов на входах разрешения счета триггеров 6.2 ;6.5 в зависимости от исправного (не- исправного) состояния основных разрядов

При этом элементы И/И-НЕ 12.1-J2.4 формируют на своих выходах функции учета исправного (неисправного) сост триггера одноименного и всех фсдыду11их разрядов. На прямом и 11иверс 1ом выходах элемента И/И-НЕ 12, сч Ч Мируются соответственно функции Z.I и Z.1 (где Z.1, имея значение логической 1,, означает исправность сор гветствующего триггера первого разряда, а Z,l, имея значение ло- ги 1еской означает неисправность этого триггера). Соответственно на выходах элемента И/И-НЕ 12.2 форми- 1уются функции Z. . 2 и Z.1 V Z.2 , па выходах элемента И/И-НЕ 12.3 - Z.1AZ.2AZ.3 и z7ivOvY73,Ha выходах эл емента И/Ц Е . Z. 1Л Z. 2А Z.3.NZ.4 и Z.1VZ.2YZ.31 Z.4.

Счетчик работает следующим образом.

Для установки двоично-десятичного счетчика в нулевое состояние на входы 18 и 19 подаются сигналы единичного логического уровня. В результате этого на выходе элемента И-НЕ 8 формируется сигнал нулевого логического уровня, который способствует выработке на выходах элементов И-НЕ 7.1-7.5 разрядов единичных логичес- к;.х уровней сигналов, которые, в очередь, устанавливают соответствующие им триггеры 6.1-6.5 в нулевое состояние. Состояния сигналов на «ходах 22.1-22.4 предустанова в этом случае не влияют на состояния логических уровней сигн алов на выходах эпоментов И-НЕ 7.1-7.4 „

Дпя установки двоично-десятичного счетчика в состояние, отличное от нулевого, на вход 18 разрешения предустанова подается сигнал логическо

го

Ч}

(при этом на входе 19 дол

Q

5

, 0 5

5

0

5

0

5

0

8

жен быть сигнал логической 1), В результате этого на двух входах элементов И-НЕ 7.1-7.5 присутствуют сигналы логической 1 и значение, в которое устанавливаются триггеры 6.1- 6.5, зависит от значений сигналов на соответствующих входах 22.1-22.4 предустанова .

При исправном состоянии основных разрядов 1-4 и режиме счета на входах 23.1-23о4 присутствуют сигналы логической I. В этом случае единичными разрешающими сигналами открыты следующие логические элементы счетчика: первые группы входов третыгх элементов 2И-ИЛИ 10.1-10,4 (разрешается прохождение на информационные выходы 24. 1-24.4 сигналов с прямых выходов триггеров 6.1-6.4 одноименных разрядов), вторые группы входов элементов 2И-ИЛИ 13.2-13.4 (разрешается прохождение сигналов с входов 22.1-22.4 предустапова на установоч- ные входы триггеров 6.1-6.4 одноименных разрядов), вторая группа входов элемента 2И-ИЛИ 15.2 (разрешается прохождение Сигналов с входа 21 на , счетный вход триггера 6.2), третья группа входов элемента ЗИ-1ШИ 14.2 (разрешается режим счета триггером 6.2 при единичном состоянии сигнала на инверсном выходе триггера 6,4), первая группа входов элемента 2И- HJlPi 25.3 (разрешаете рем1М счета триггера 6,3), первая группа элемента 2И-1 ШИ 15,3 (разрешено прохождение импульсов счета с прямого выхода триггера 6,2), первая группа входов элемента 2И-ИЛИ 25.4 (разрешено про- |Хождение счетного режима триггера при единичных состояниях триггеров 6.2 и 6,3), первая группа входов элемента 2И-ИЛИ 15,4 (разрешается счетный режим триггера 6,4 при его единичном состоянии),.третья группа входов элемента ЗИ-ИЛИ 14,4 (разрешается прохождение импульсов счета с входа 21 на счетный вход триггера 6.4), открытое или закрытое состояния групп входов элемента ЗИ-ИЛИ 14.5 значения в этом случае не имеют, так как прямой выход триггера 6.5 OTKjno4eH от выхода 24.4,

Остальные группы входов логических элементов 2И-ИЛИ 10,1-10,4, 13,2- 13.4, 14.2, 14,4, 25.3, 25.4, 15.2- 15.4 закрыты нулевыми логическими уровнями.

Счет импульсов производится по следующей логической ветви: с входа 20 ;на счетный вход триггера 6.1, через первую группу входов элемента 2И- ИЛН 10.1 на выход 24.1, через соединение выхода 24.1 с входом 21, через вторую группу входов элемента 2И-11ПИ

15.2на счетный вход триггера 6.2, через первую группу входов элемента 2И-ИЛИ 10.2 на выход 24.2, через первую группу входов элемента 2И-ИЛИ

15.3на счетный вход триггера 6.3, через первую группу входов элемента

крываются их вторые группы входов,а также элемент И 17. В результате этого входы 22.1-22.4 предустанова подключаются к установочным входам триггеров 6.2-6.5 последующих разрядов. Аналогично перестраивается и логическая ветвь подсчета импульсов в счетчике. Открытая в этом случае первая группа входов элемента 2И- ИЛИ 15.2 позволяет поступать синхро импульсам с входа 20 на счетный вход триггера 6.2. С прямого выхода триггера 6.2 информация поступает через

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

Изобретение относится, в частности, к счетчикам и делителями частоты следования импульсов и может быть использовано в устройствах промышленной автоматики и вычислительной техники. Целью изобретения является повышение эксплуатационной отказоустойчивости устройства. Это достигается путем введения в его структурно-логическую организацию резервного разряда и логических элементов автоматический реконфигурации работоспособной структуры. Счетчик выполнен на триггерах и логических элементах и соединен конструктивными связями по многоразрядной схеме. В двоично-десятичном счетчике осуществляется автоматическая реконфигурация его структурно-логической организации при подаче соответствующего сигнала на управляющий вход. При отказе одного из основных разрядов обеспечивается возможность перехода на резервную работоспособную структуру, что создает возможность обеспечения работоспобности логического устройства автоматики и вычислительной техники без замены данного устройства. Таким образом повышается его эксплуатационная отказоустойчивость. 1 ил., 2 табл.

2И-ИЛИ 10.3 на выход 24.3, с прямого 15 вторую группу входов элемента 2Ивыхода триггера 6.3 через первую группу входов элемента 2И-ИЛИ 25,4 на вход разрешения счетного режима триггера 6.4, с прямого выхода триггера 6.4 через первую группу входов

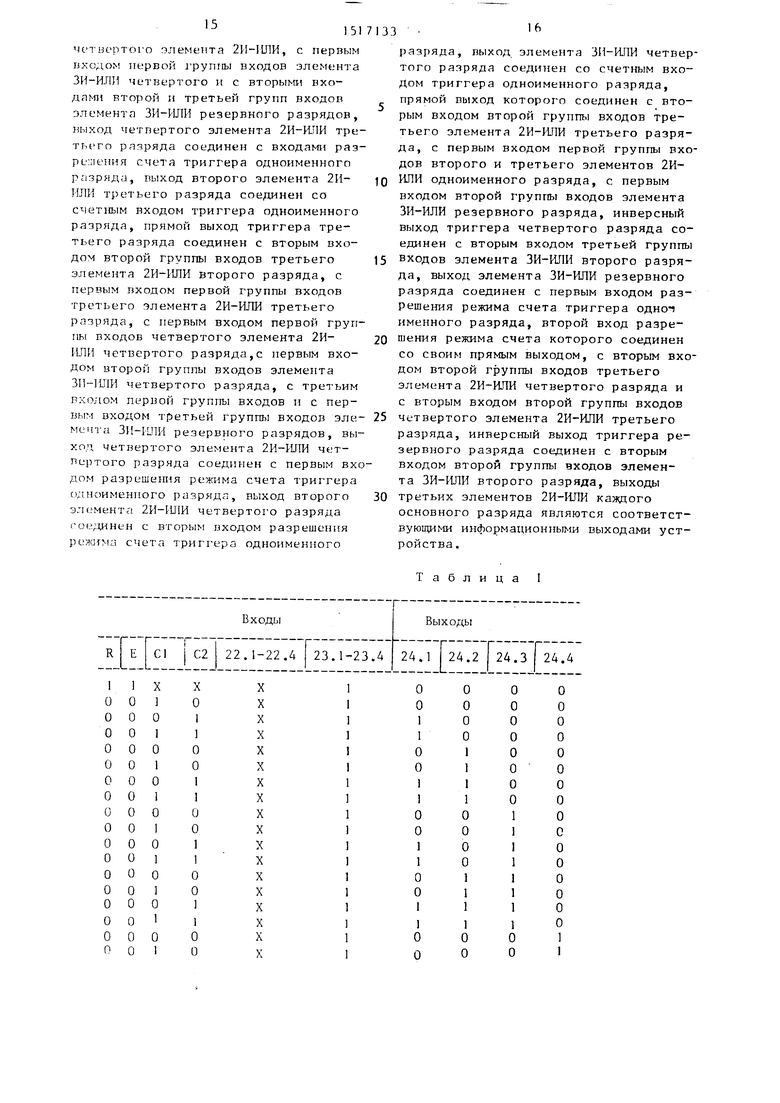

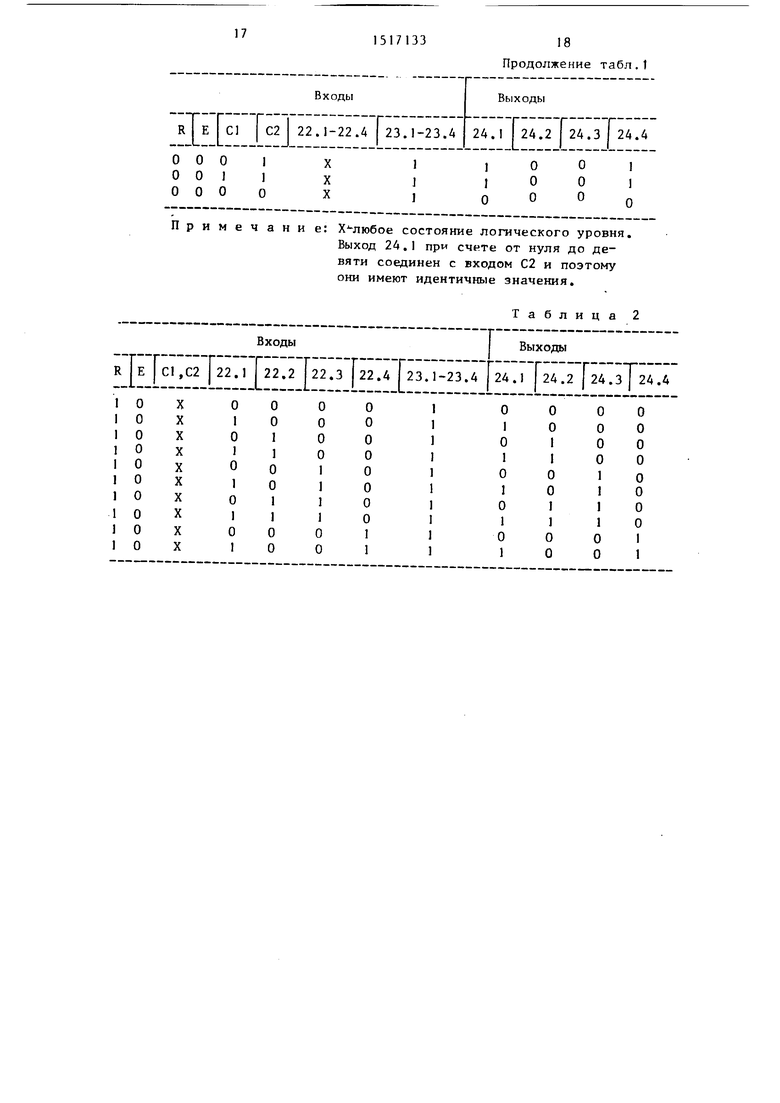

.элемента 2И-ИЛИ 10.4 на выход 24.4. В табл.1 приведено состояние вхо1дов и выходов счетчика при счете от ну.ля до девяти.

элемента 2И-ИЛИ 10.3 поступает на выход 24.3 и через вторую группу входов элемента 2И-ИЛИ на разрешающий вход релаша счета триггера 6.5. С прямого выхода триггера 6.5 состоя- :ние сигнала (и его изменение) через

В табл.2 приведены значения состо- 25 та ЗИ-ИЛИ 14.4 на счетный вход яний счетчика при использовании вхо- триггера 6,4. С прямого выхода триг- дов 22„1-22.4 прсдустанова и исправ- гера 6.4 состояние сигнала (и его из- Ьюй работе основных триггеров 6.1-6.4. менение) через вторую группу входов

При неисправном состоянии одного ИЗ триггеров 6.1-6.4 на соответствую- 30 щий управляющий вход 23.1-23.4 подается сигнал логического О.

Рассмотрим принцип перехода на работоспособную структуру счетчика на примерах, когда произошел отказ триг- 35 вторую группу входов элемента 2И- гера 6.1 или 6.3.ИЛИ 10.4 поступает на выход 24.4.

При отказе триггера 6.1 на управ- Первые и вторые входы разрешения ляющий вход 23,1 подается нулевой режима счета триггеров 6.4 и 6.5 сое- потенциал и данный триггер исключается из режима функционирования дво- 40 ично-десятичного счетчика. Это производится следующим образом.

Функции учета исправного (неисправного) состояния Z.i и Z.i в этом

45

50

случае изменяют значения состояний на прямых и инверсных выходах элементов И/И-НЕ 12.1-12.4 таким образом, что Z.1, Z.2,Z.3 и Z.4 принимают значение нулевого логического сигнала, а Z.1, Z.2, Z.3, Z.4 - значение 1. Вследствие этого закрываются первые группы входов элементов 2И-ИЛИ 10.1-10.4 и открываются их вторые группы входов, подключая тем самым к информационным выхо- дам 24 „1-24.4 прямые выходы тригге- ров 6«2-6.5 соответственно. Кроме .того, закрываются первые группы входов элементов 2И-ИЛИ 13.2-13.4 и отдинены по принципу селектора, т.е. по схеме ИЛИ между собой и по схеме И индивидуально каждый со счетным входом.

Алгоритм работы двоично-десятичного счетчика в этом случае полностью подчиняется закону, описанному таблицами состояний входов и выходов, представленными в табл.1 и 2.

При отказе триггера 6.3 на управляющий вход 23.3 подается нулевой сигнал и данный триггер исключается из режима функционирования двоично- десятичного счетчика. Сигнал, поступая с входа 23,3 на вход элемента И/И-НЕ 12.3, приводит к тому, что на его прямом и инверсном выходах, а также на аналогичных выходах элемента И/И-НЕ 12.4 функции учета исправного (неисправного) состояний изменяют свои логические значения на инверсные.

ИЛИ 10.1 на выход 24.1 и через соединение 24.1||21, открытую в этом случае вторую группу входов элемента 2И-ИЛИ 15.3 на счетный вход тригге- ра 6.3. С прямого выхода триггера 6.3 состояние сигнала (и его изменение) через вторую группу входов элемента 2И-ИЛИ 10.2 поступает на выход 24.2 и через вторую группу входов элеменэлемента 2И-ИЛИ 10.3 поступает на выход 24.3 и через вторую группу входов элемента 2И-ИЛИ на разрешающий вход релаша счета триггера 6.5. С прямого выхода триггера 6.5 состоя- :ние сигнала (и его изменение) через

вторую группу входов элемента 2И- ИЛИ 10.4 поступает на выход 24.4.

Первые и вторые входы разрешения режима счета триггеров 6.4 и 6.5 сое- 0

5

0

динены по принципу селектора, т.е. по схеме ИЛИ между собой и по схеме И индивидуально каждый со счетным входом.

Алгоритм работы двоично-десятичного счетчика в этом случае полностью подчиняется закону, описанному таблицами состояний входов и выходов, представленными в табл.1 и 2.

При отказе триггера 6.3 на управляющий вход 23.3 подается нулевой сигнал и данный триггер исключается из режима функционирования двоично- десятичного счетчика. Сигнал, поступая с входа 23,3 на вход элемента И/И-НЕ 12.3, приводит к тому, что на его прямом и инверсном выходах, а также на аналогичных выходах элемента И/И-НЕ 12.4 функции учета исправного (неисправного) состояний изменяют свои логические значения на инверсные.

1517133

Сле/итнателыю, первый и второй разря- ;п, п зтом случае функционируют анапо- .гп ып случ, исправности всех основ- lUiix разрядов, а третий и четвертый п.попды - случаю неисправности триг- ; 6.1. Таким образом логическая . Ki ypa дг .оично-десятичного счетчи- 1ер(м:траивается на работоспособную

, в - тесняя отказавший тре- ю 2И-ИЛИ, второй разряд содержит элемент ЗИ-ИЛИ, третий разряд содержит четвертый элемент 2И-1 ШИ и элемент НЕ, четвертый разряд содержит четвертый элемент 2И-ИЛИ, элемент ЗИ-ИЛИ

триггер 6.3, Прямые выходы триг- в 6.1 и 6.2 подключены на одно- H.t uiMe им выходы 24.1 и 24.2, а прямые выходы триггеров 6.4 и 6.5 - H;i выхо№1 24.3 и 24.4 соответственно 15 элемент НЕ, выход элемента И-НЕ

устройства соединен с третьим входом первого и с вторым входом второго элементов И-НЕ резервного разряда, выход элемента ИЛИ устройства соеди-::5амена отказавших второго и четвер- I oi o три1таров производится аналогично .

1аким образом, в предлагаемом двоично-десятичном счетчике осуществляет-20 с вторым входом первого элемеи- ся автоматическая реконфигурация его та И-НЕ резервно-Го разряда, выход лоси.чсской структуры при отказе одно- гч из основных разрядов,, что создает по: южиос гь обеспечения работоспособ- }и1сги этого счетчика без замены, еле- 25 Да, выход которого соединен с инвер- доиптельно, повьшается эксплуатацион- сным R-входом триггера резервного иля отказоустойчивость предложенного счетчика.

которого соединен с инверсным S-вхо- дом триггера и с первым входом второго элемента И-НЕ резервного разряразряда, первый синхровход устройства соединен с вторым входом первой группы входов второго элемента 2Ий ормула изобретения

Двоично-десятичный счетчик, содер- ЗО ИЛИ второго разряда, второй синхрожа ;1;ий элементы И-НЕ, ИЛИ и разряды, каждый из которых содержит триггер, два элемента И-НЕ, вход разрешения предварительной установки устройства соединен с первым входом элемента И-НЕ устройства, второй вход которог с входом элемента ИЛИ уст- роиства и с входом установки в О устройства, выход элемента И-НЕ уст- poi icTBa соединен с вторыми входами первого и второго элементов И-НЕ ка ;:дого разряда, выход элемента ИЛИ ус:ройства соединен с третьим входом первого элемента И-НЕ каждого разряда, вход предварительной установки первого разряда соединен с первым входом первого элемента И-НЕ одноименого разряда, выход первого элемента Н-НЕ каждого разряда соединен с ин- лерсным S-входом триггера и с пер- Г|/м входом второго элемента И-НЕ од- разряда, выход второго п;; лментп И-НЕ каждого разряда соеди- Ht -vi с п. лперсиым R-входом триггера одп.1менного разряда, первый синхро- пу.од устройства соединен со счетным 1 ходо;- ера первого разряда, о т л и ч а ю щ и и с я тем, что, с псль Г повьпаения экс1шуатационной от12

казоустойчивости, в него введены резервный разряд, содержащий триггер, два элемента И-НЕ, элемент И и элемент ЗИ-ИЛИ, а каждый разряд дополнительно содержит элемент И/И-НЕ , третий элемент 2И-ИЛИ, разряды, кроме первого и резервного, дополнительно содержат первый и второй элеменустройства соединен с третьим входом первого и с вторым входом второго элементов И-НЕ резервного разряда, выход элемента ИЛИ устройства соеди с вторым входом первого элемеи- та И-НЕ резервно-Го разряда, выход Да, выход которого соединен с инвер- сным R-входом триггера резервного

с вторым входом первого элемеи- та И-НЕ резервно-Го разряда, выход Да, выход которого соединен с инвер- сным R-входом триггера резервного

которого соединен с инверсным S-вхо- дом триггера и с первым входом второго элемента И-НЕ резервного разря с вторым входом первого элемеи- та И-НЕ резервно-Го разряда, выход Да, выход которого соединен с инвер- сным R-входом триггера резервного

разряда, первый синхровход устройства соединен с вторым входом первой группы входов второго элемента 2И5

0

5

0

5

вход устройства соединен с вторым входом второй группы входов вторых элементов 2И-Ш1И второго и третьего разрядов, с первым входом третьей группы входов элемента ЗИ-ИЛИ четвертого разряда и со счетным входом триггера резервного разряда, вход запрета работы первого разряда соединен с входом элемента И/И-НЕ одноименного разряда, вход запрета работы второго разряда соединен .с вторым входом элемента И/И-НЕ одноименного разряда, вход запрета работы третьего разряда соединен с вторым входом элемента И/И-НЕ и с входом элемента НЕ одноименного разряда, вход запрета работы четвертого разряда соединен с вторым входом элемента И/И-НЕ и с входом элемента НЕ одноименного разряда, вход предварительной установки второго разряда соединен с вторым входом второй группы входов первого элемента 2И-ИЛИ одноименного и с вторым входом первой группы входов первого элемента 2И-ИЛИ третьего разрядов, вход предварительной установки третьего разряда соединен с вторым входом второй группы входов первого 2И-ИЛИ одноименного и с в то1 3

рым входом первой группы входов первого элемента 2И-ИЛИ четвертого разрядов, вход предварительной установки четвертого разряда соединен с вторым входом второй группы входов первого элемента 2И-ИЛИ одноименного и с вторым входом элемента И резервного разрядов, вход предварительной установки .первого разряда дополнительно соединен с вторым входом первой группы входов первого элемента 2И-ИЛИ второго разряда, прямой выход элемента И/И- НЕ первого разряда соединен с вторым входом первой группы входов третьего элемента 2И-ИЛИ одноименного, с первым входом второй группы входов ВТО- ) рого элемента 2И-ЛПИ, с первы входом второй группы входов первого элемента 2И-ИЛИ и с первым входом элемента И/И-НЕ второго разрядов, инверсный выход элемента И/И-НЕ первого разряда соединен с первым входом второй группы входов третьего элемента 2И-ИЛИ одноименного, с первым входом первой группы входов первого и второго элементов 2И-ИЛИ и с входом первой группы входов элемента ЗИ-ИЛИ второго разрядов, прямой выход элемента

И/И-НЕ второго разряда соединен с вто-30 вым входом элемента И резервного раз- рым входом первой группы входов третьего элемента 2И-ИЛИ одноименного, с вторым входом первой группы входов второго, с входом первой группы входов четвертого и с первым входом второй группы входов первого элемен тов 2И-ИЛИ, а также с первым входом .

.элемента И/И-НЕ третьего разрядов, инверсный выход элемента И/И-НЕ вторядов, выход элемента НЕ четвертого разряда соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ резервного разряда, выход первых эле- эс Ментов 2И-ИЛИ вто оого, третьего и Четвертого разрядов соединен с первым входом первого элемента И-НЕ одноименного разряда, выход элемента И резервного разряда соединен с первым

рого разряда соединен с первым входом о входом первого элемента И-НЕ одно- второй группы входов третьего элемента 2И-ИЛИ одноименного, с первым входом первой группы входов первого, с первым входом второй группы входов

именного разряда, прямой выход триг гера первого разряда соединен с пер вым входом первой группы входов тре тьего элемента 2И-ИЛИ одноименного разряда, выход элемента ЗИ-ИЛИ втор го разряда соединен с входами разре ния режима счета триггера одноименн го разряда, выход второго элемента 2И-ИЛИ второго разряда соединен со счетным входом триггера одноименног разряда, прямой выход триггера второго разряда соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ первого разряда, с ег первым входом первой группы входов третьего элемента 2И-ИЛИ одноименного, с первым,входом первой группы вх дов второго элемента 2И-ШТИ третьего с вторым входом первой группы входов

четвертого, с первым входом второй группы входов второго элементов 2И- ШШ третьего, а также с вторым входом второй группы входов элемента ЗИ-ИЛИ четвертого, с первым входом первой группы входов элемента ЗИ- ИПИ резервного разрядов, прямой выход элемента И/И-НЕ третьего разряда соединен с вторым входом первой группы входов третьего элемента 2И- ИЛИ одноименного, с вторым входом первой группы входов второго, с третьим входом первой группы входов четвертого, с первым входом второй группы входов первого элементов 2И-ИЛИ

-713314

и с первым входом элемента И/И-ИЕ Четвертого разрядов, инверсны выход элемента И/И-НЕ третьего раяряда соединен с первым входом второй группы входов третьего элемента 2И-ИЛИ одноименного, с входом второй группы входов второго, с входом второй группы входов четвертого и с первым вхо1Q дом второй группы входов первого

элементов И/И-НЕчетвертого разрядов, выход элемента НЕ третьего разряда соединен с вторым входом первой группы входов элемента ЗИ-1ШИ четвертого

15 и с третьим входом второй группы входов элемента ЗИ-ИЛИ резервного разрядов, прямой выход элемента И/И-НЕ четвертого разряда соединен с первым входом третьей группы входов элемен20 та ЗИ-ИЛИ второго, с вторым входом

третьей группы входов элемента ЗИ-ИЛИ и с вторым входом первой группы входов третьего элемента 2И-1ШИ одноименного разрядов, инверсный выход

25 элемента И/И-НЕ четвертого разряда .Соединен с первым входом первой группы входов элемента ЗИ-ИЛИ второго,с первым входом второй группы входов третьего элемента 2И-ИЛИ одноименного и с первым входом элемента И резервного раз-

рядов, выход элемента НЕ четвертого разряда соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ резервного разряда, выход первых эле- Ментов 2И-ИЛИ вто оого, третьего и Четвертого разрядов соединен с первым входом первого элемента И-НЕ одноименного разряда, выход элемента И резервного разряда соединен с первым

входом первого элемента И-НЕ одно-

именного разряда, прямой выход триггера первого разряда соединен с первым входом первой группы входов третьего элемента 2И-ИЛИ одноименного разряда, выход элемента ЗИ-ИЛИ второго разряда соединен с входами разрешения режима счета триггера одноименного разряда, выход второго элемента 2И-ИЛИ второго разряда соединен со счетным входом триггера одноименного разряда, прямой выход триггера второго разряда соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ первого разряда, с первым входом первой группы входов третьего элемента 2И-ИЛИ одноименного, с первым,входом первой группы входов второго элемента 2И-ШТИ третьего, с вторым входом первой группы входов

1-5,5,

чс ТБС ртого элемента 2И-1ШИ, с первым входом первой I pyniibi входов элемежта ЗИ-ИЛИ четвертого и с вторыми вхо- даьп второй и третьей групп входов элемента ЗИ-ИЛИ резервного разрядов, яыход четвертого элемента 2И-ИЛИ третьего разряда соединен с входами раэ ре:пення счета триггера одноименного разряда, выход второго элемента 2И- ШШ третьего разряда соединен со c ieTiibiM входом триггера одноименного разряда, прямой выход триггера третьего разряда соединен с вторым входом второй группы входов третьего элемента 2И-1-ШИ второго разряда, с первым входом первой группы входов третьего элемента 2И-И1Ш третьего разряда, с первым входом первой группы входов четвертого элемента 2И- ШИ четвертого разряда,с первым входом второй группы входов элемента ЗП-ГШИ четвертого разряда, с третьим входом первой группы входов и с первым входом третьей группы входов элемента резервного разрядов, выход четвертого элемента 2И-ИЛИ чет- лертого разряда соединен с первым вхдом разрешеш1я режима счета триггера одноименного разряда, выход второго элемента 2И-Ш1И четвертого разряда гое;линен с вторым входом разрешения релмма счета триггера одноименного

133

16

разряда, выход элемента ЗИ-ИЛИ четвертого разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ третьего разряда, с первым входом первой группы входов второго и третьего элементов 2ИИЛИ одноименного разряда, с первым входом второй группы входов элемента ЗИ-ИЛИ резервного разряда, инверсный выход триггера четвертого разряда соединен с вторым входом третьей группы

входов элемента ЗИ-ИЛИ второго разряда, выход элемента ЗИ-ИЛИ резервного разряда соединен с первым входом раз- Решения режима счета триггера одно1 именного разряда, второй вход разрешения режима счета которого соединен со своим прямым выходом, с вторым входом второй группы входов третьего элемента 2И-ИЛИ четвертого разряда и с вторым входом второй группы входов

четвертого элемента 2И-ИЛИ третьего разряда, инверсный выход триггера резервного разряда соединен с вторым входом второй группы входов элемента ЗИ-ИЛИ второго разряда, выходы

третьих элементов 2И-ИЛИ каждого

основного разряда являются соответствующими информационными выходами устройства.

Таблица I

17

1517133

18 Продолжение табл,1

гг.1

г.{

Zt,.2

24

2k it

| Матвеев В.В„ и др | |||

| Приборы для измерения ионизирующих излучений.- М.: Атомиздат, 1972, с.546, рис.229(В) | |||

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник./Под ред.Б.Н.Файзулаева, Б.В.Тарабаринэ - М.: Радио и связь, 1987, с.40, рис.3.32. |

Авторы

Даты

1989-10-23—Публикация

1988-05-13—Подача