разряда;

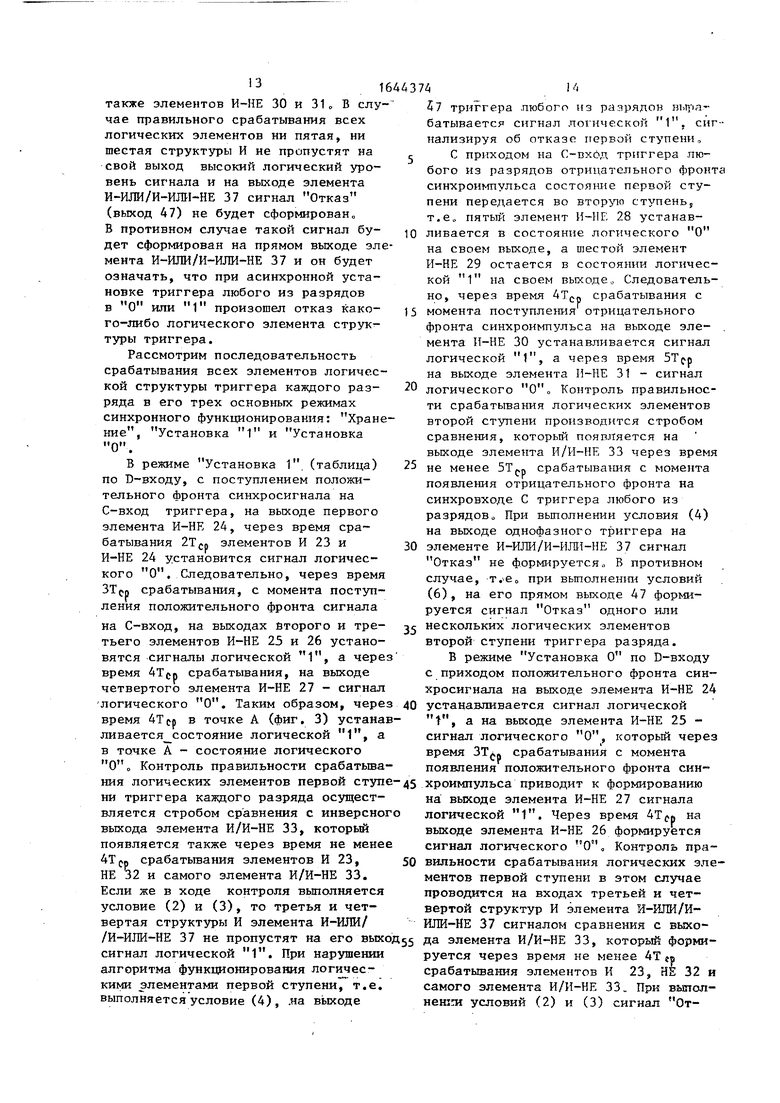

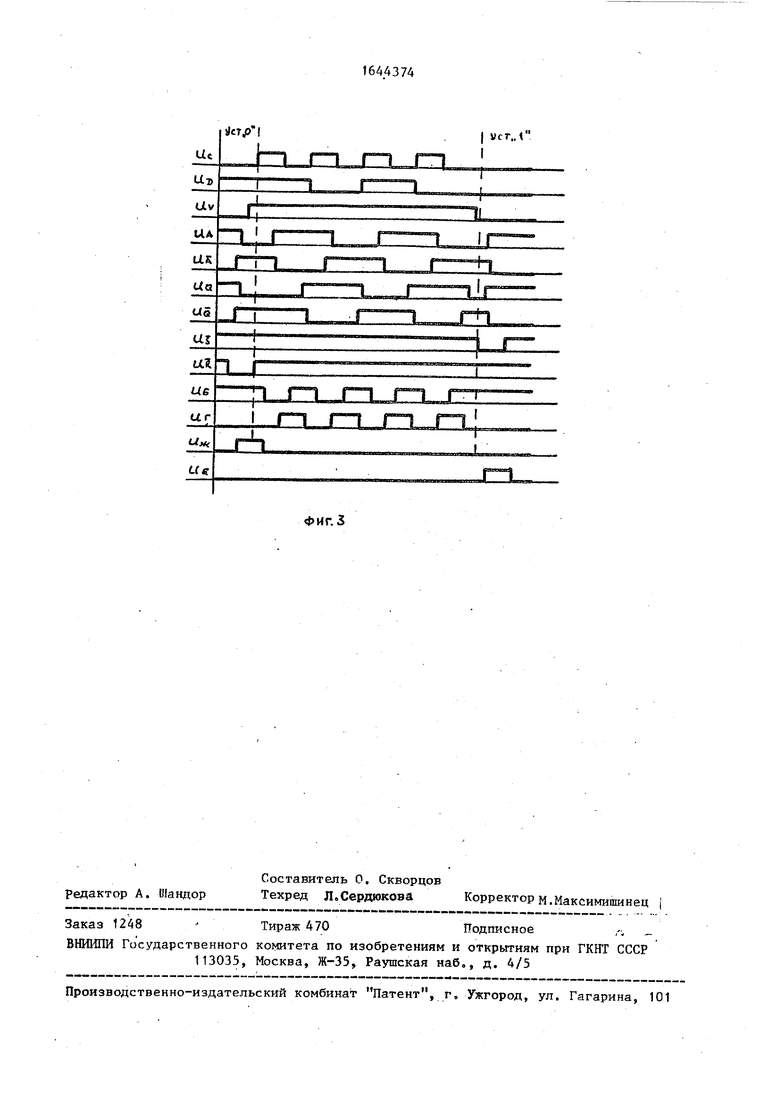

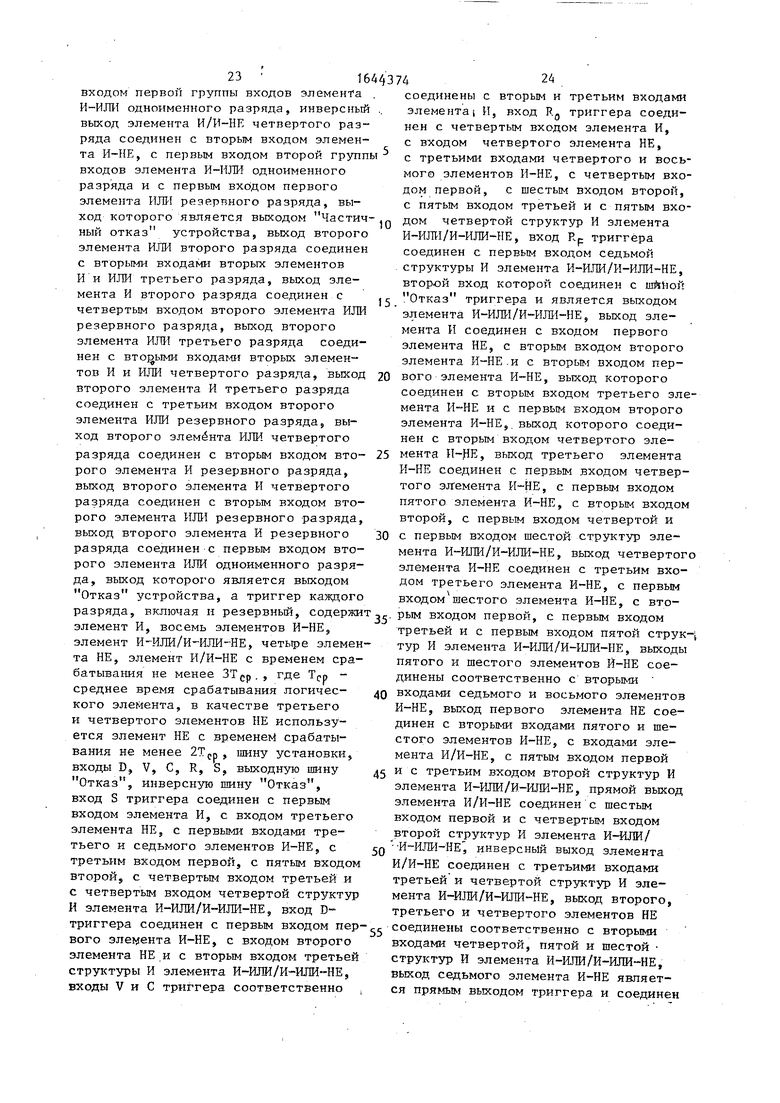

S,S - единичное и нулевое соответственно состояния сигналов на S-входе триггера каж дого разряда; Q, О - состояния сигналов на прямом 44 и инверсном 45 выходах триггера каждого разряда.

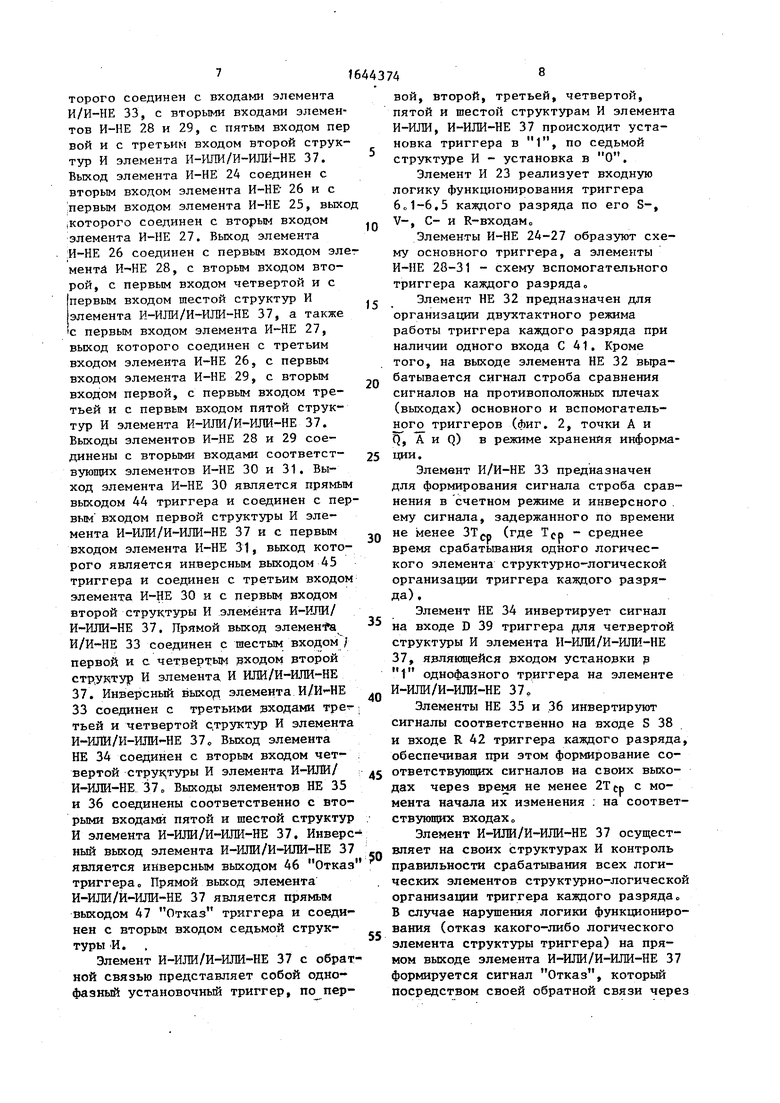

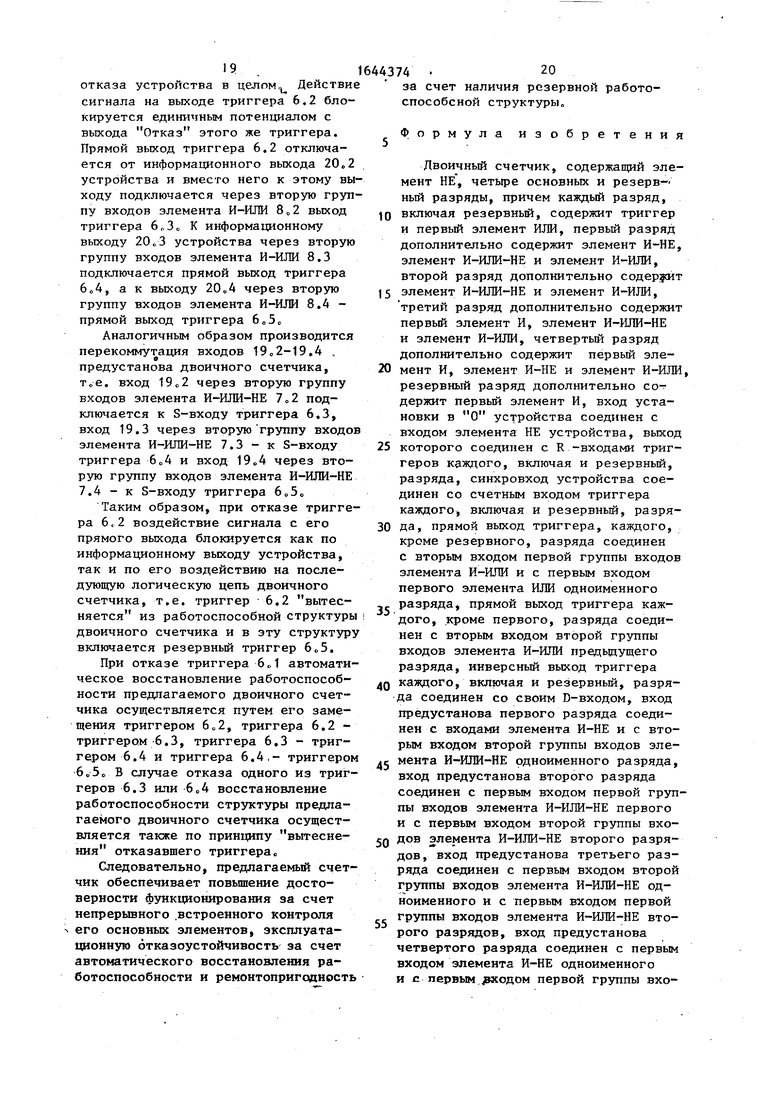

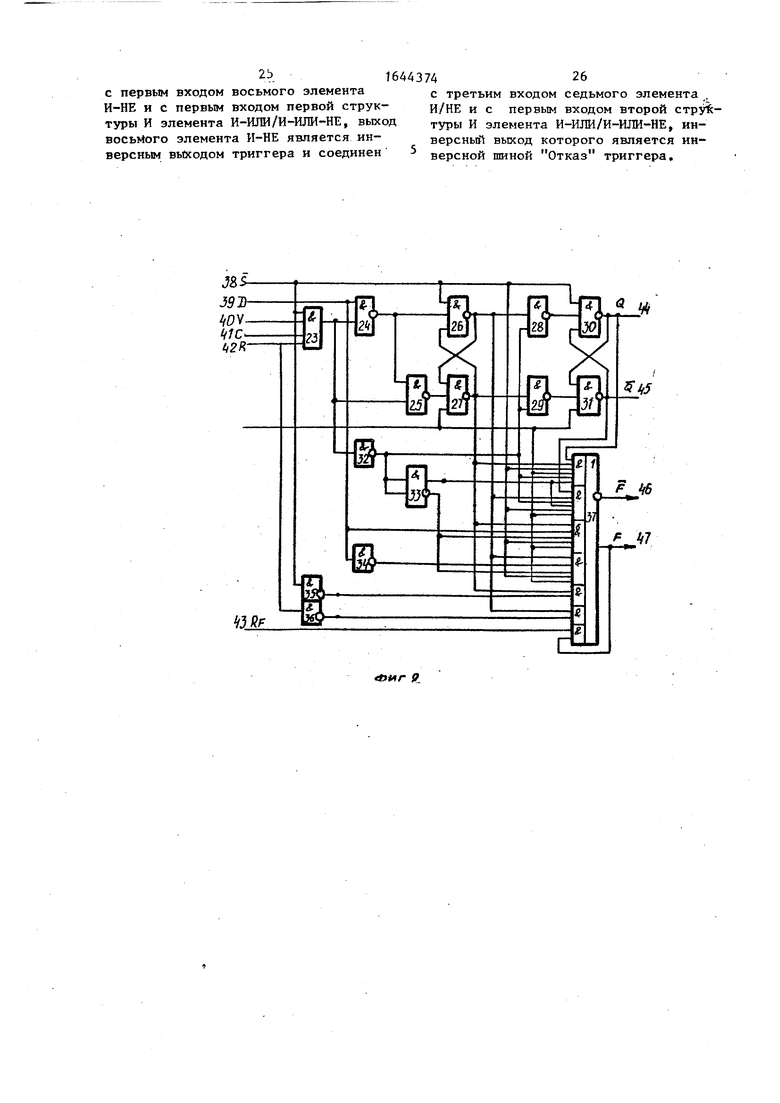

Отличительной особенностью элементов И/И-НЕ 33 и НЕ 35 и 36 н структуре триггера каждого разряда является то, что кроме функционально- логической нагрузки они выполняют

функционального контроля, так как в силу случайного характера переходных процессов во время включения питания однофазный триггер на элементе И ИЛИ/И-ИЛИ-НЕ 37 может изначально установиться в единичное состояние, соответствующее сигналу Отказ соответствующего триггера о

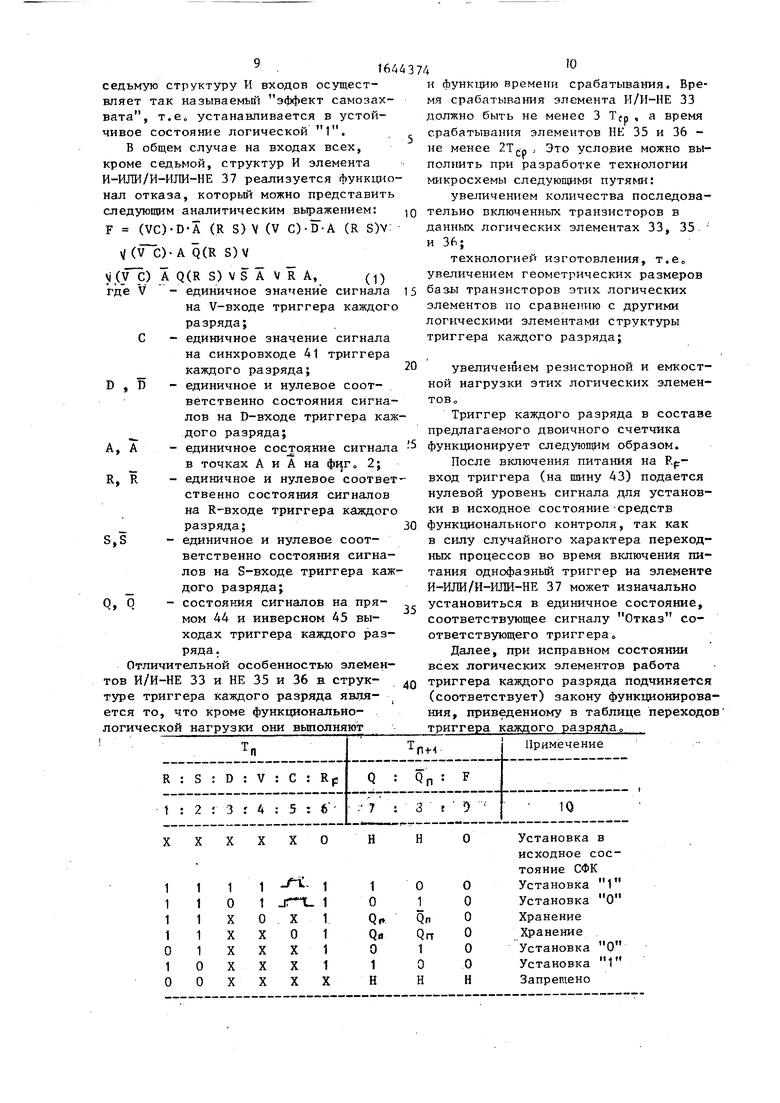

Далее, при исправном состоянии всех логических элементов работа

триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в таблице переходов триггера каждого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

X X

Установка в исходное состояние СФК Установка 1 Установка О Хранение Хранение Установка О

Установка Запрещено

Ч1

лице обозначены:

момент времени последующего состояния триггера каждого ра зряда;

момент времени последующего состояния триггера каждого разряда;

безразличное состояние сигнала на соответствующем входе триггера каждого разряда; неопределенное состояние соответствующего выхода; переход от низкого логического уровня сигнала к высокому и обратно (импульс);

предыдущее состояние соответствующего выхода триггера каждого разряда.

цессе своего функционироваая ступень триггера каждого подчиняется закону, предому следующим аналитичесением:

F(A

F(A

где V

1) (VC)-D-(RS) V S;(2) 1) (VC)-D (RS) v R, (3)

единичное состояние сигнала на V-входе триггера каждого разряда;

С - единичное состояние сигнала на синхровходе С 41 триггер каждого разряда;

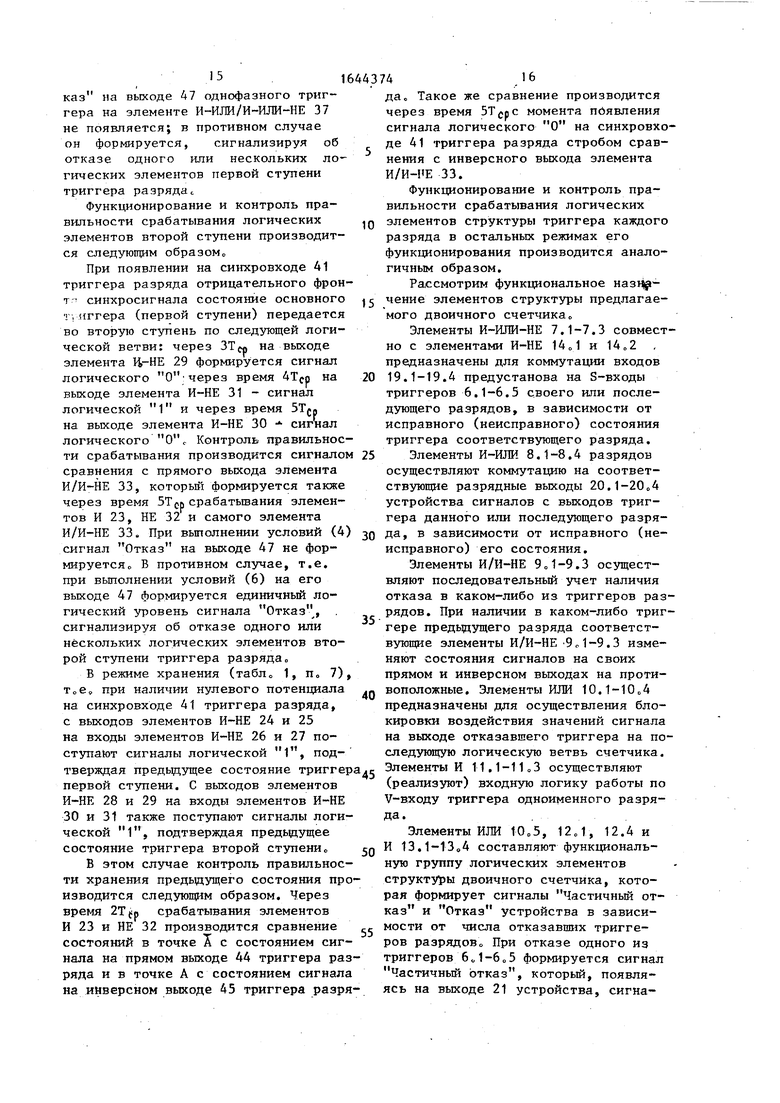

D, D - единичное и нулевое соответственно состояния сигналов на D-входе триггера каждого разряда; А, А - состояния сигналов в точках

А и А на фиг. 2;

R, R - единичное и нулевое соответственно состояния сигналов на R-входе триггера каж дого разряда;

S, S - единичное и нулевое соответственно состояния сигналов на S-входе триггера каждого разряда.

За выполнением условий выражений (2) и (3) следят третья и четвертая структуры И элемента И-ИЛИ/И-ИЛИ- НЕ 37.

В процессе своего функционировани вторая ступень (вспомогательный триггер) триггера каждого разряда подчиняется закону, который можно представить следующим аналитическим выражением:

0

5

0

Q-(RS)(VC)(RS)(VC)A 1(4)

где VC - единичное состояние на выходе элемента НЕ 32,триггера каждого разряда;

Q,Q - состояния сигналов на прямом и инверсном соответственно выходах триггера каждого разряда

За выполнением условий выражения (4) следят первая и вторая структуры И элемента И-ИЛИ/И-ИЛИ-НЕ 37„

Функционал отказа любого из логических элементов первой ступени (основного триггера), реализованный в триггере каждого разряда, можно представить следующим аналитическим выражением:

F, (VC)- D A(RS)v(VG)D A(RS)vSAvRA ;

(5)

В случае нарушения условий функционирования, представленных в выражениях (2) и (3), на выходе элемен5 Та И-ИЛИ/И-ИЛИ-НЕ 37 уже в момент срабатывания логических элементов первой ступени вырабатывается сигнал Отказ триггера каждого из разрядов. Функционал отказа любого из логи0 ческих элементов второй ступени

(вспомогательного триггера), реализованный в техническом решении триггера каждого разряда, можно представить следующим выражением:

5 FЈ (VC) AQ(RS)v(VC) A Q(RS) , (6)

В случае нарушения условий функционирования, представленных в выражении (4), на выходе элемента

0 И-ИЛИ/И-ИЛИ-НЕ 37 также вырабатывается сигнал Отказ триггера любого из разрядов

Асинхронный режим функционирования триггера каждого из разрядов

5 контролируется пятой и шестой структурами И элемента И-ИЛИ/И-ИЛИ-НЕ 37. Режим установки в 1 контролирует пятая структура И, режим установки в О - шестая структура И элемента

0 И-ИЛИ/И-ИЛИ-НЕ 37. Характерной особенностью этого режима является то, что установка основного и вспомогательного триггеров структуры триггера каждого разряда осуществляется

5 одновременноо Вот почему строб сравнения на выходах элементов НЕ 35 и 36 вырабатывается через время не менее 2Тср, т0е0 через время срабатывания элементов И-НЕ 26 и 27, а

также элементов И-НЕ 30 и 31„ В случае правильного срабатывания всех логических элементов ни пятая, ни шестая структуры И не пропустят на свой выход высокий логический уровень сигнала и на выходе элемента И-ИЛИ/И-ИЛИ-НЕ 37 сигнал Отказ (выход 47) не будет сформирован, В противном случае такой сигнал будет сформирован на прямом выходе элемента И-ИЛИ/И-ИЛИ-НЕ 37 и он будет означать, что при асинхронной установке триггера любого из разрядов в О или 1 произошел отказ какого-либо логического элемента структуры триггера.

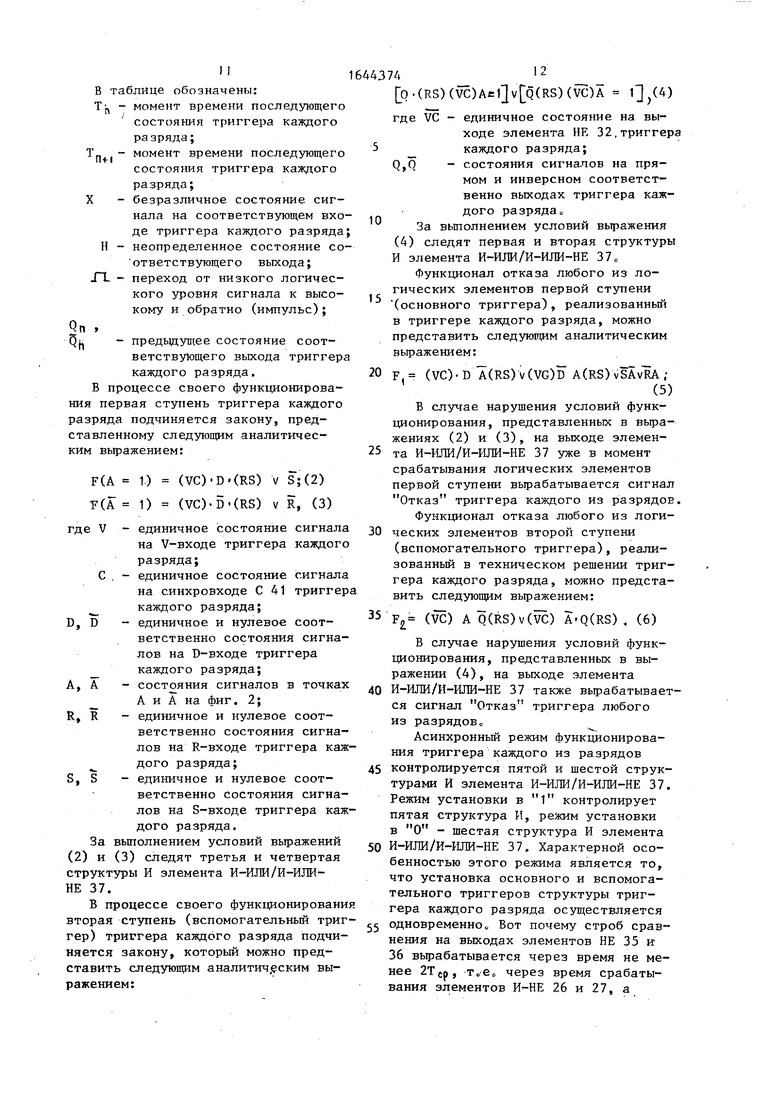

Рассмотрим последовательность срабатывания всех элементов логической структуры триггера каждого разряда в его трех основных режимах синхронного функционирования: Хранение, Установка 1 и Установка О.

В режиме Установка 1. (таблица) по D-входу, с поступлением положительного фронта синхросигнала на С-вход триггера, на выходе первого элемента И-НЕ 24, через время срабатывания 2Тс. элементов И 23 и И-НЕ 24 установится сигнал логического О. Следовательно, через время ЗТСр срабатывания, с момента поступления положительного фронта сигнала

на С-вход, на выходах Второго и третьего элементов И-НЕ 25 и 26 установятся сигналы логической 1, а чере время 4Т(чр срабатывания, на выходе четвертого элемента И-НЕ 27 - сигнал логического время 4Т ер в

ливается состояние логической 1, а в точке А - состояние логического

О. Таким образом, чере точке А (фиг. 3) устанаВ режиме Установка 0 по D-входу с приходом положительного фронта синхросигнала на выходе элемента И-НЕ 24 устанавливается сигнал логической t, а на выходе элемента И-НЕ 25 - сигнал логического О, который через время срабатывания с момента

Контроль правильности срабатывания логических элементов первой ступе-45 хроимпульса приводит к формированию ни триггера каждого разряда осущест- на выходе элемента И-НЕ 27 сигнала вляется стробом сравнения с инверсного выхода элемента И/И-НЕ 33, который появляется также через время не менее 4ТСп срабатывания элементов И 23, НЕ 32 и самого элемента И/И-НЕ 33. Если же в ходе контроля выполняется условие (2) и (3), то третья и четвертая структуры И элемента И-ИЛИ/

появления положительного фронта силлогической 1. Через время 4Tfp на выходе элемента И-НЕ 26 формируется сигнал логического О, Контроль пра- 50 вильности срабатывания логических элементов первой ступени в этом случае проводится на входах третьей и четвертой структур И элемента И-ИЛИ/ИИЛИ-НЕ 37 сигналом сравнения с выхо/И-ИЛИ-НЕ 37 не пропустят на его выход55 да элемента И/И-НЕ 33, который форми- сигнал логической 1. При нарушении алгоритма функционирования логическими элементами первой ступени, т.е. выполняется условие (4) , .на выходе

руется через время не менее 4Т е« срабатывания элементов И 23, НЕ 32 и самого элемента И/И-НЕ 33. При выпол- ненги условий (2) и (3) сигнал От

5

триггера любого из разрядов вырабатывается сигнал логической 1, сигнализируя об отказе первой ступени,

С приходом на С-вхбд триггера любого из разрядов отрицательного фронта синхроимпульса состояние первой ступени передается во вторую ступень, т.е„ пятый элемент И-НЕ 28 устанавливается в состояние логического О на своем выходе, а шестой элемент И-НЕ 29 остается в состоянии логической 1 на своем выходе„ Следовательно, через время 4Тср срабатывания с момента поступления отрицательного фронта синхроимпульса на выходе элемента И-НЕ 30 устанавливается сигнал

логической 1, а через время 5Т

ср

на выходе элемента И-НЕ 31 - сигнал логического Контроль правильности срабатывания логических элементов второй ступени производится стробом сравнения, который появляется на выходе элемента И/И-НЕ 33 через время не менее 5ТСр срабатывания с момента

появления отрицательного фронта на синхровходе С триггера любого из разрядов о При выполнении условия (4) на выходе однофазного триггера на элементе И-ИЛИ/И-ИЛИ-НЕ 37 сигнал Отказ не формируется„ В противном случае, т.е при выполнении условий (6), на его прямом выходе 47 формируется сигнал Отказ одного или нескольких логических элементов второй ступени триггера разряда.

В режиме Установка 0 по D-входу с приходом положительного фронта синхросигнала на выходе элемента И-НЕ 24 устанавливается сигнал логической t, а на выходе элемента И-НЕ 25 - сигнал логического О, который через время срабатывания с момента

хроимпульса приводит к формированию на выходе элемента И-НЕ 27 сигнала

появления положительного фронта силхроимпульса приводит к формированию на выходе элемента И-НЕ 27 сигнала

логической 1. Через время 4Tfp на выходе элемента И-НЕ 26 формируется сигнал логического О, Контроль пра- вильности срабатывания логических элементов первой ступени в этом случае проводится на входах третьей и четвертой структур И элемента И-ИЛИ/Ида элемента И/И-НЕ 33, который форми-

руется через время не менее 4Т е« срабатывания элементов И 23, НЕ 32 и самого элемента И/И-НЕ 33. При выпол- ненги условий (2) и (3) сигнал От1516

каз на выходе А7 однофазного триггера на элементе И-ИЛИ/И-ИЛИ-НЕ 37 не появляется; в противном случае он формируется, сигнализируя об отказе одного или нескольких логических элементов первой ступени триггера разрядас

Функционирование и контроль правильности срабатывания логических элементов второй ступени производится следующим образом,,

При появлении на синхровходе 41 триггера разряда отрицательного фрон- т синхросигнала состояние основного , иггера (первой ступени) передается во вторую ступень по следующей логической ветви: через ЗТ на выходе элемента Иу-НЕ 29 формируется сигнал логического О через время 4Tfp на выходе элемента И-НЕ 31 - сигнал логической 1 и через время 5ТС на выходе элемента И-НЕ 30 сигнал логического Контроль правильности срабатывания производится сигналом сравнения с прямого выхода элемента И/И-НЕ 33, который формируется также через время 5Т0р срабатывания элементов И 23, НЕ 32 и самого элемента И/И-НЕ 33. При выполнении условий (4) сигнал Отказ на выходе 47 не формируется с В противном случае, т.е. при выполнении условий (6) на его выходе 47 формируется единичный логический уровень сигнала Отказ, сигнализируя об отказе одного или нескольких логических элементов второй ступени триггера разряда

В режиме хранения (таблс 1, п„ 7), т0е, при наличии нулевого потенциала

I л

на синхровходе 41 триггера разряда, с выходов элементов И-НЕ 24 и 25 на входы элементов И-НЕ 26 и 27 поступают сигналы логической 1, подтверждая предыдущее состояние триггер первой ступени. С выходов элементов И-НЕ 28 и 29 на входы элементов И-НЕ 30 и 31 также поступают сигналы логической 1, подтверждая предыдущее состояние триггера второй ступени„

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом. Через время 2Ttp срабатывания элементов И 23 и НЕ 32 производится сравнение состояний в точке К с состоянием сигнала на прямом выходе 44 триггера разряда и в точке А с состоянием сигнала на инверсном выходе 45 триггера разря

3

д

0 5

п

с 0

с

5

да. Такое же сравнение производится через время 5Тсрс момента появления сигнала логического О на синхровходе 41 триггера разряда стробом сравнения с инверсного выхода элемента И/И-НЕ 33.

Функционирование и контроль правильности срабатывания логических элементов структуры триггера каждого разряда в остальных режимах его функционирования производится аналогичным образом.

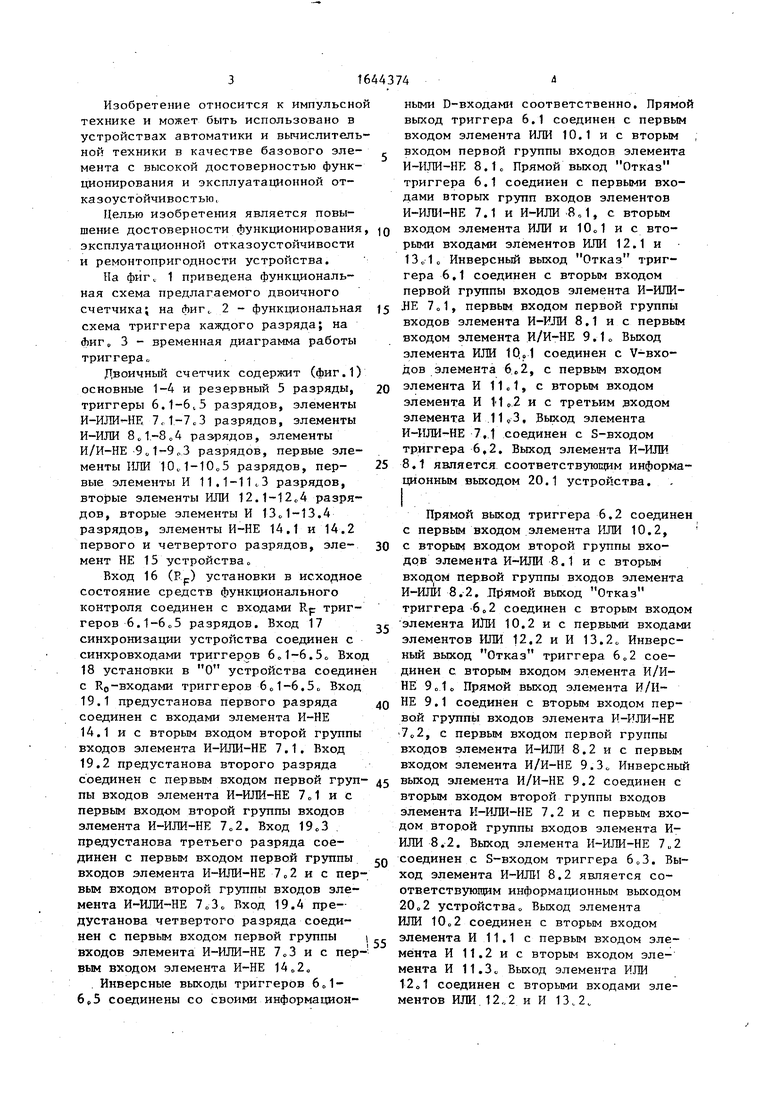

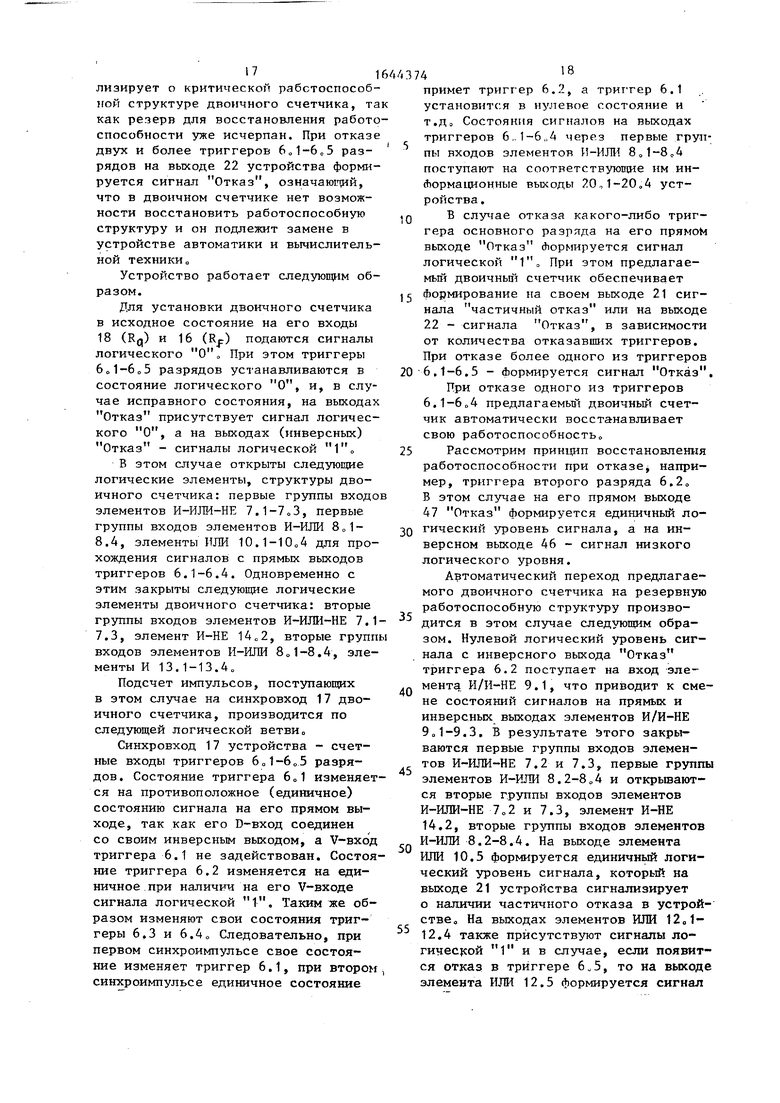

Рассмотрим функциональное назНф- чение элементов структуры предлагаемого двоичного счетчика

Элементы И-ИЛИ-НЕ 7.1-7.3 совместно с элементами И-НЕ 14„1 и 14„2 предназначены для коммутации входов 19.1-19.4 предустанова на S-входы триггеров 6.1-6.5 своего или последующего разрядов, в зависимости от исправного (неисправного) состояния триггера соответствующего разряда.

Элементы И-ИЛИ 8.1-8.4 разрядов осуществляют коммутацию на соответствующие разрядные выходы 20.1-20„4 устройства сигналов с выходов триггера данного или последующего разряда, в зависимости от исправного (неисправного) его состояния.

Элементы И/И-НЕ 9„1-9.3 осуществляют последовательный учет наличия отказа в каком-либо из триггеров разрядов. При наличии в каком-либо триггере предыдущего разряда соответствующие элементы И/И-НЕ 9„1-9.3 изменяют состояния сигналов на своих прямом и инверсном выходах на противоположные. Элементы ИЛИ 10.1-10„4 предназначены для осуществления блокировки воздействия значений сигнала на выходе отказавшего триггера на последующую логическую ветвь счетчика. Элементы И 11.1 -11 , 3 осуществляют (реализуют) входную логику работы по V-входу триггера одноименного разряда.

Элементы ИЛИ 10„5, 12 „ 1, 12.4 и И 13.1-13,4 составляют функциональную группу логических элементов структуры двоичного счетчика, которая формирует сигналы Частичный отказ и Отказ устройства в зависимости от числа отказавших триггеров разрядово При отказе одного из триггеров 6„1-6о 5 формируется сигнал Частичный отказ, который, появляясь на выходе 21 устройства, сигнализирует о критической работоспособной структуре двоичного счетчика, та как резерв для восстановления работоспособности уже исчерпан. При отказе двух и более триггеров 601-605 разрядов на выходе 22 устройства формируется сигнал Отказ, означающий, что в двоичном счетчике нет возможности восстановить работоспособную структуру и он подлежит замене в устройстве автоматики и вычислительной техники о

Устройство работает следующим образом.

Для установки двоичного счетчика в исходное состояние на его входы 18 (Rq) и 16 (Rp) подаются сигналы логического При этом триггеры 6 о 1-6„5 разрядов устанавливаются в состояние логического О, и, в случае исправного состояния, на выходах Отказ присутствует сигнал логического О, а на выходах (инверсных) Отказ - сигналы логической 1

В этом случае открыты следующие логические элементы, структуры двоичного счетчика: первые группы входо элементов И-ИЛИ-НЕ 7.1-703, первые группы входов элементов И-ИЛИ 8„1- 8.4, элементы ИЛИ 10.1-1004 для прохождения сигналов с прямых выходов триггеров 6.1-6.4. Одновременно с этим закрыты следующие логические элементы двоичного счетчика: вторые группы входов элементов И-ИЛИ-НЕ 7.1 7.3, элемент И-НЕ 14„2, вторые групп входов элементов И-ИЛИ 801-8.4, элементы И 13.1-13.4„

Подсчет импульсов, поступающих в этом случае на синхровход 17 двоичного счетчика, производится по следующей логической ветви„

Синхровход 17 устройства - счетные входы триггеров 6„1-6„5 разрядов. Состояние триггера 6„1 изменяется на противоположное (единичное) состоянию сигнала на его прямом выходе, так как его D-вход соединен со своим инверсным выходом, а V-вход триггера 6.1 не задействован. Состояние триггера 6.2 изменяется на единичное при наличии на его V-входе сигнала логической 1, Таким же образом изменяют свои состояния триггеры 6.3 и 6.4о Следовательно, при первом синхроимпульсе свое состояние изменяет триггер 6.1, при втором синхроимпульсе единичное состояние

0

5

0

5

0

5

0

5

0

5

примет триггер 6.2, а триггер 6.1 установится в нулевое состояние и т.д0 Состояния сигналов на выходах триггеров 6 1-6„4 через первые группы входов элементов И-ИЛИ 8„1-8 4 поступают на соответствующие им информационные выходы 20,1-20,4 устройства .

В случае отказа какого-либо триггера основного разряда на его прямом выходе Отказ сформируется сигнал логической 1м о При этом предлагаемый двоичный счетчик обеспечивает Формирование на своем выходе 21 сигнала частичный отказ или на выходе 22 - сигнала Отказ, в зависимости от количества отказавших триггеров. При отказе более одного из триггеров 6.1-6.5 - Формируется сигнал Отказ.

При отказе одного из триггеров 6.1-6„4 предлагаемый двоичный счетчик автоматически восстанавливает свою работоспособность

Рассмотрим принцип восстановления работоспособности при отказе, например, триггера второго разряда 6.2„ В этом случае на его прямом выходе 47 Отказ формируется единичный логический уровень сигнала, а на инверсном выходе 46 - сигнал низкого логического уровня.

Автоматический переход предлагаемого двоичного счетчика на резервную работоспособную структуру производится в этом случае следующим образом. Нулевой логический уровень сигнала с инверсного выхода Отказ триггера 6.2 поступает на вход элемента И/И-НЕ 9.1, что приводит к смене состояний сигналов на прямых и инверсных выходах элементов И/И-НЕ 9„1-9.3. В результате этого закрываются первые группы входов элементов И-ИЛИ-НЕ 7.2 и 7.3, первые группы элементов И-ИЛИ 8.2-8«, 4 и открываются вторые группы входов элементов И-ИЛИ-НЕ 7о2 и 7.3, элемент И-НЕ 14.2, вторые группы входов элементов И-ИЛИ 8.2-8.4. На выходе элемента ИЛИ 10.5 формируется единичный логический уровень сигнала, который на выходе 21 устройства сигнализирует о наличии частичного отказа в устройстве. На выходах элементов ИЛИ 12„1- 12.4 также присутствуют сигналы логической 1 и в случае, если появится отказ в триггере 6,5, то на выходе элемента ИЛИ 12.5 формируется сигнал

отказа устройства в целом Действие сигнала на выходе триггера 6.2 блокируется единичным потенциалом с выхода Отказ этого же триггера. Прямой выход триггера 6.2 отключается от информационного выхода 20.2 устройства и вместо него к этому выходу подключается через вторую группу входов элемента И-ИЛИ 8„2 выход триггера 6„3о К информационному выходу 20о 3 устройства через вторую группу входов элемента И-ИЛИ 8.3 подключается прямой выход триггера 604, а к выходу 20„4 через вторую группу входов элемента И-ИЛИ 8.4 - прямой выход триггера 605С

Аналогичным образом производится перекоммутация входов 19„2-19.4 , предустанова двоичного счетчика, т„е. вход 19„2 через вторую группу входов элемента И-ИЛИ-НЕ 7„2 подключается к S-входу триггера 6.3, вход 19.3 через вторую группу входов элемента И-ИЛИ-НЕ 7.3 - к S-входу триггера 604 и вход 19„4 через вторую группу входов элемента И-ИЛИ-НЕ 7.4 - к S-входу триггера 6„5с

Таким образом, при отказе триггера 6,2 воздействие сигнала с его прямого выхода блокируется как по информационному выходу устройства, так и по его воздействию на последующую логическую цепь двоичного счетчика, т.е. триггер 6.2 вытесняется из работоспособной структуры двоичного счетчика и в эту структуру включается резервный триггер 6«5.

При отказе триггера 6С1 автоматическое восстановление работоспособности предлагаемого двоичного счетчика осуществляется путем его замещения триггером 6.2, триггера 6.2 - триггером 6.3, триггера 6.3 - триггером 6.4 и триггера 6.4,- триггером 6,5С В случае отказа одного из триггеров 6.3 или 6о4 восстановление работоспособности структуры предлагаемого двоичного счетчика осуществляется также по принципу вытеснения отказавшего триггера.

Следовательно, предлагаемый счетчик обеспечивает повышение достоверности функционирования за счет непрерывного встроенного контроля его основных элементов, эксплуатационную отказоустойчивость за счет автоматического восстановления работоспособности и ремонтопригодность

за счет наличия резервной работо- способсной структуры.

Формула изобретения

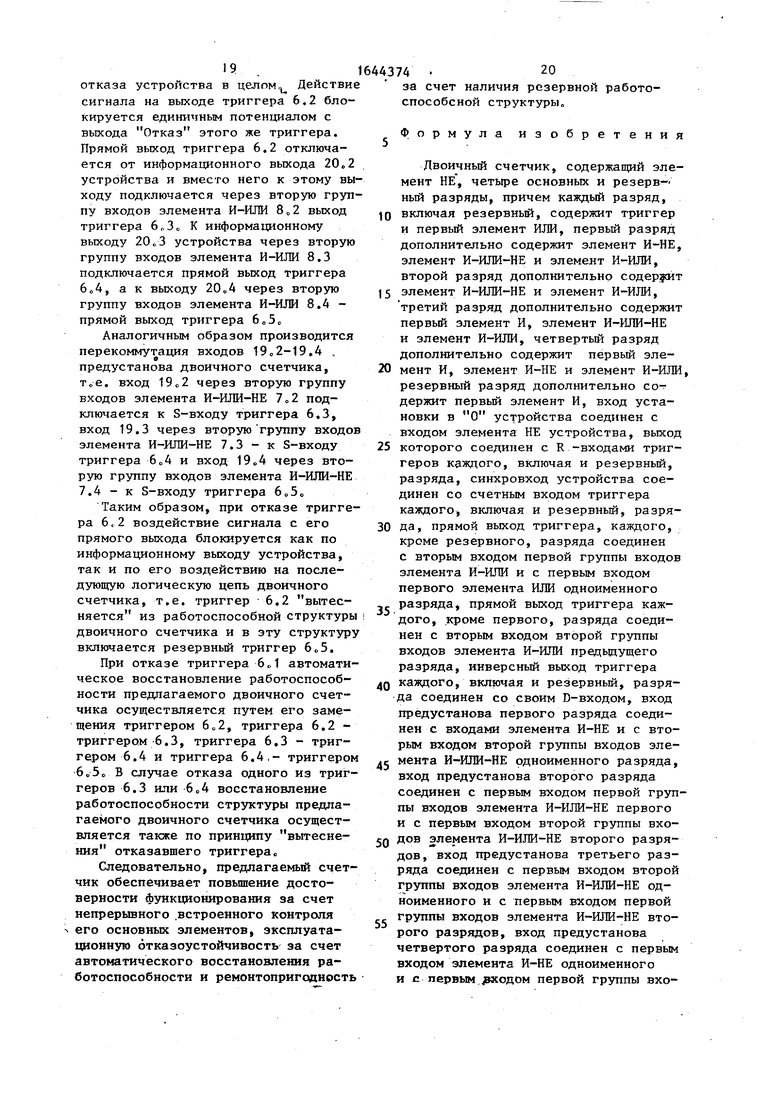

Двоичный счетчик, содержащий элемент НЕ, четыре основных и резервный разряды, причем каждый разряд,

включая резервный, содержит триггер и первый элемент ИЛИ, первый разряд дополнительно содержит элемент И-НЕ, элемент И-ИЛИ-НЕ и элемент И-ИЛИ, второй разряд дополнительно содержит

5 элемент И-ИЛИ-НЕ и элемент И-ИЛИ, третий разряд дополнительно содержит первый элемент И, элемент И-ИЛИ-НЕ и элемент И-ИЛИ, четвертый разряд дополнительно содержит первый эле0 мент И, элемент И-НЕ и элемент И-ИЛИ, резервный разряд дополнительно содержит первый элемент И, вход установки в О устройства соединен с входом элемента НЕ устройства, выход

5 которого соединен с R -входами триггеров каждого, включая и резервный, разряда, синхровход устройства соединен со счетным входом триггера каждого, включая и резервный, раэря0 да, прямой выход триггера, каждого, кроме резервного, разряда соединен с вторым входом первой группы входов элемента И-ИЛИ и с первым входом первого элемента ИЛИ одноименного

s разряда, прямой выход триггера каждого, кроме первого, разряда соединен с вторым входом второй группы входов элемента И-ИЛИ предыдущего разряда, инверсный выход триггера

0 каждого, включая и резервный, разряда соединен со своим D-входом, вход предустанова первого разряда соединен с входами элемента И-НЕ и с вторым входом второй группы входов эле5 мента И-ИЛИ-НЕ одноименного разряда, вход предустанова второго разряда соединен с первым входом первой группы входов элемента И-ИЛИ-НЕ первого и с первым входом второй группы вхо0 дов элемента И-ИЛИ-НЕ второго разрядов, вход предустанова третьего разряда соединен с первым входом второй группы входов элемента И-ИЛИ-НЕ одноименного и с первым входом первой группы входов элемента И-ИЛИ-НЕ второго разрядов, вход предустанова четвертого разряда соединен с первым входом элемента И-НЕ одноименного и с. первым .входом первой группы вхо5

дов элемента И-ИЛИ-НЕ третьего разрядов, выход элемента PI-HE первого разряда соединен с S-входом триггера одноименного разряда, выход элемента И-ИЛИ-НЕ первого, второго и третьего разрядов соединен с S-входов триггера последующего разряда, выход элемента И-НЕ четвертого разряда соединен с S-входом триггера резервного разряда, выходы элементов И-ИЛИ, кроме резервного, разряда являются соответствующим разрядным выходом устройства, отличающий - с я тем, что, с целью повышения достоверности функционирования, эксплуатационной отказоустойчивости и ремонтопригодности, в него дополнительно введены во второй разряд элемент И, второй элемент ИЛИ и элемент И/И-НЕ, третий разряд дополнительно содержит элемент И/И-НЕ, второй элемент ИЛИ и второй элемент И, четвертый разряд дополнительно содержит элемент И/И-НЕ, второй элемент И и второй элемент ИЛИ, резервный разряд дополнительно содержит второй элемент ИЛИ и второй элемент И, причем прямой выход Отказ триггера первого разряда соединен с вторым входом элемента ИЛИ, с первыми входами вторых групп входов элементов И-ИЛИ и И-ИЛИ-НЕ одноименного разряда и с вторыми входами второго элемента ИЛИ и элемента И второго разряда, инверсный выход Отказ триггера первого разряда соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ, с первым входом первой группы входов элемента И-ИЛИ одноименного и с первым входом элемента И/И-НЕ второго разрядов, инверсный выход Отказ триггеров второго, третьего и четвертого разрядов соединен соответственно с вторым входом элемента И/И-НЕ одноименного разряда, прямой выход Отказ триггера второго разряда соединен с вторым входом первого элемента ИЛИ и с первыми входами второго элемента ИЛИ и элемента И одноименного разряда, прямой выход Отказ триггера третьего разряда соединен с вторым входом второго элемента ИЛИ и с первыми входами вторых элементов ИЛИ и И одноименного разряда, прямой выход Отказ триггера четвертого разряда соединен с вторым входом первого элемента ИЛИ и с первыми входами

5

0

5

0

вторых элементов ИЛИ и И одноименного разряда, прямой выход Отказ триггера резервного разряда соединен с

вторым входом первого элемента ИЛИ и с первым входом второго элемента И одноименного разряда, вход Rp установки в исходное состояние средств функционального контроля устройства

0 соединен с Rp-входами триггера каждого, включая и резервный, разряда, выход элемента ИЛИ первого разряда соединен с V-входом триггера второго разряда, с первым входом первого элемента И третьего, с вторым входом первого элемента И четвертого и с третьим входом первого элемента И резервного разрядов, выход первого элемента ИЛИ второго разряда соединен. с вторым дходом первого элемента И третьего разряда, с первым входом первого элемента И четвертого разряда и с вторым входом первого элемента И резервного разряда, выход первого элемента ИЛИ третьего разряда соединен с третьим входом первого элемента И четвертого разряда и с первым входом первого элемента И резервного разряда, выход первого элемента ИЛИ четвертого разряда соединен с четвертым входом первого элемента И резервного разряда, выходы элементов И третьего, четвертого и резервного разрядов соединены с V-входами триггеров одноимен5 ного разряда, прямой выход элемента И/И-НЕ второго разряда соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ, с первым входом первой группы входов элемента И-ИЛИ

0 одноименного и с первым входом элемента И/И-НЕ третьего разрядов, инверсный выход элемента И/И-НЕ второго разряда соединен с вторым входом второй группы входов элемента И-ИЛИ-НЕ,

5 с первым входом второй группы входов эл-емента И-ИЛИ одноименного разрядаs прямой выход элемента И/И-НЕ третьего разряда соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ,с первым

0 входом первой группы входов элемента И-ИЛИ одноименного и с первым входом элемента И/И-НЕ четвертого разряда, инверсный выход элемента И/И-НЕ третьего разряда соединен с вторым вхо- ,

5 Дом второй группы входов элемента

И-ИЛИ-НЕ, с первым входом второй группы входов элемента И-ИЛИ одноименного разряда, прямой выход элемента И/И-НЕ четвертого разряда соединен с первым

входом первой группы входов элемента И-ИЛИ одноименного разряда, инверсный выход элемента И/И-НЕ четвертого разряда соединен с вторым входом элемента И-НЕ, с первым входом второй групп входов элемента И-ИЛИ одноименного разряда и с первым входом первого элемента ИЛИ резервного разряда, выход которого является выходом Частичный отказ устройства, выход второго элемента ИЛИ второго разряда соединен с вторыми входами вторых элементов И и ИЛИ третьего разряда, выход элемента И второго разряда соединен с четвертым входом второго элемента ИЛИ резервного разряда, выход второго элемента ИЛИ третьего разряда соединен с вторыми входами вторых элементов И и ИЛИ четвертого разряда, выход второго элемента И третьего разряда соединен с третьим входом второго элемента ИЛИ резервного разряда, выход второго элемента ИЛИ четвертого разряда соединен с вторым входом второго элемента И резервного разряда, выход второго элемента И четвертого разряда соединен с вторым входом второго элемента ИЛИ резервного разряда, выход второго элемента И резервного разряда соединен с первым входом второго элемента ИЛИ одноименного разряда, выход которого является выходом Отказ устройства, а триггер каждого

разряда, включая и резервный, содержит рым входом первой, с первым входом элемент И, восемь элементов И-НЕ, третьей и с первым входом пятой струк- элемент И-ИЛИ/И-ИЛИ-НЕ, четыре элемен- Тур и элемента И-ИЛИ/И-ИЛИ-НЕ, выходы та НЕ, элемент И/И-НЕ с временем ера- пятого и шестого элементов И-НЕ сое- батывания не менее ЗТср., где Тср - динены соответственно с вторыми

40

среднее время срабатывания логического элемента, в качестве третьего и четвертого элементов НЕ используется элемент НЕ с временем срабатывания не менее 2Тср} шину установки, входы D V, С, R, S, выходную шину Отказ, инверсную шину Отказ, вход S триггера соединен с первым входом элемента И, с входом третьего элемента НЕ, с первыми входами третьего и седьмого элементов И-НЕ, с третьим входом первой, с пятым входом второй, с четвертым входом третьей и с четвертым входом четвертой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, вход D- триггера соединен с первым входом первого элемента И-НЕ, с входом второго элемента НЕ и с вторым входом третьей структуры И элемента И-ИЛИ/И-ИЛИ-НЕ, входы V и С триггера соответственно

45

50

55

входами седьмого и восьмого элементов И-НЕ, выход первого элемента НЕ соединен с вторыми входами пятого и шестого элементов И-НЕ, с входами элемента И/И-НЕ, с пятым входом первой и с третьим входом второй структур И элемента И-ИЛИ/И-ИЛИ-НЕ, прямой выход элемента И/И-НЕ соединен с шестым входом первой и с четвертым входом второй структур И элемента И-ИЛИ/ И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с третьими входами третьей и четвертой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, выход второго, третьего и четвертого элементов НЕ соединены соответственно с вторыми входами четвертой, пятой и шестой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, выход седьмого элемента И-НЕ является прямым выходом триггера и соединен

0

соединены с вторым и третьим входами элемента| И, вход РО триггера соединен с четвертым входом элемента И, с входом четвертого элемента НЕ, с третьими входами четвертого и восьмого элементов И-НЕ, с четвертым входом первой, с шестым входом второй, с пятым входом третьей и с пятым входом четвертой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, вход Rp триггера соединен с первым входом седьмой структуры И элемента И-ИЛИ/И-ИЛИ-НЕ, второй вход которой соединен с шиной Отказ триггера и является выходом элемента И-ИЛИ/И-ИЛИ-НЕ, выход элемента И соединен с входом первого элемента НЕ, с вторым входом второго элемента И-НЕ и с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И--НЕ и с первым входом второго элемента И-НЕ, выход которого соединен с вторым входом четвертого эле- 5 мента Н-НЕ, выход третьего элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, с первым входом пятого элемента И-НЕ, с вторым входом второй, с первым входом четвертой и с первым входом шестой структур элемента И-ИЛИ/И-ИЛИ-НЕ, выход четвертого элемента И-НЕ соединен с третьим входом третьего элемента И-НЕ, с первым входом шестого элемента И-НЕ, с вто5

0

0

входами седьмого и восьмого элементов И-НЕ, выход первого элемента НЕ соединен с вторыми входами пятого и шестого элементов И-НЕ, с входами элемента И/И-НЕ, с пятым входом первой и с третьим входом второй структур И элемента И-ИЛИ/И-ИЛИ-НЕ, прямой выход элемента И/И-НЕ соединен с шестым входом первой и с четвертым входом второй структур И элемента И-ИЛИ/ И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с третьими входами третьей и четвертой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, выход второго, третьего и четвертого элементов НЕ соединены соответственно с вторыми входами четвертой, пятой и шестой структур И элемента И-ИЛИ/И-ИЛИ-НЕ, выход седьмого элемента И-НЕ является прямым выходом триггера и соединен

с первым входом восьмого элемента И-НЕ и с первым входом первой структуры И элемента И-ИЛИ/И-ИЛИ-НЕ, выход восьмого элемента И-НЕ является инверсным выходом триггера и соединен

JSS

с третьим входом седьмого элемента . И/НЕ и с первым входом второй струй- туры И элемента И-ИЛИ/И-ИЛИ-НЕ, инверсный выход которого является инверсной шиной Отказ триггера.

ыяг 9.

&P

ь.

j-i m f-i

U«

Фиг. 3

| Vcr..

rh

Авторы

Даты

1991-04-23—Публикация

1989-03-27—Подача