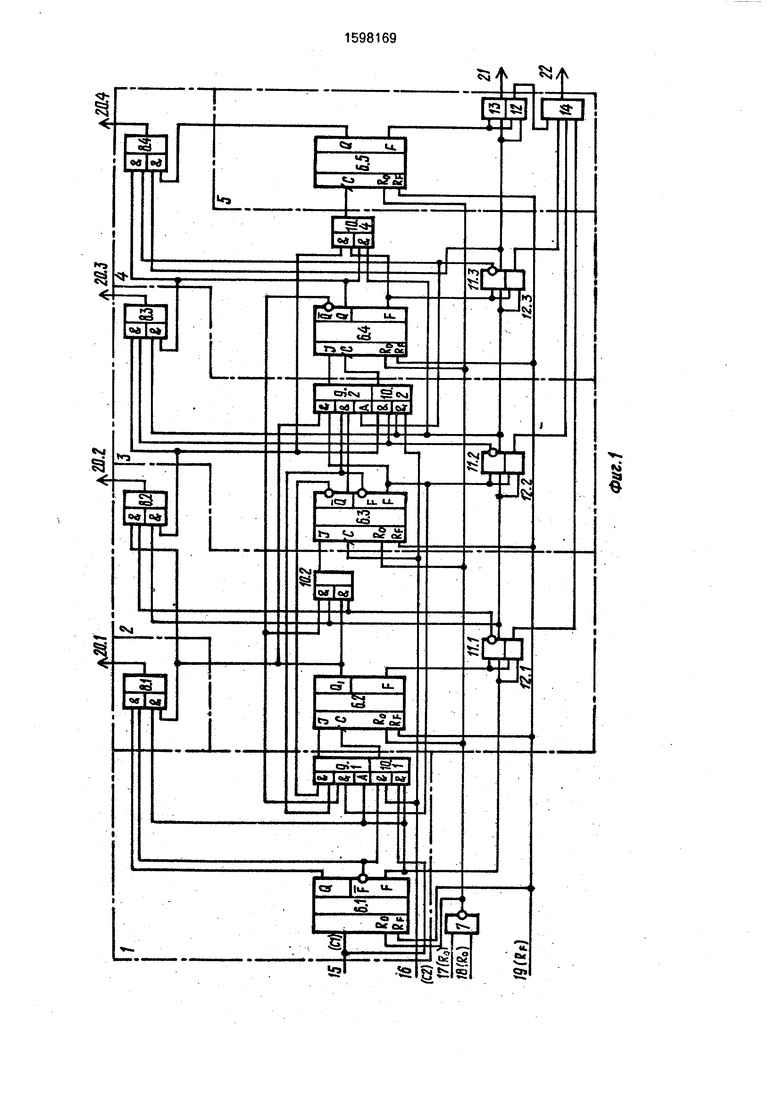

6,5 разрядов, элемент И-НЕ 7 устройства, первые 8.1-8.4 элементы 2-2И-ИЛИ разрядов, элементы 3-2И-ИЛИ 9.1 и 9.2 первого и третьего разрядов, вторые 10.1-10.4 элементы 2-2И-ИЛИ разрядов, элементы ИЛИ/ИЛИ-НЕ 11.1-11.3 разрядов, элементы И 12.1-12.4 разрядов, первый 13 и второй 14 элементы ИЛИ резервного разряда.

Вход 15 синхронизации устройства соединен со счетным входом триггера 6.1 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 10.1. Второй 16 вход синхронизации устройства соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 10.1, со счетным входом триггера 6.3 и с вторым входом второй группы входов элемента 2-2И-ИЛИ 10.3. Первый 17 и второй 18 входы установки в О устройства соединены соответственно с первым и вторым входами элемента И-НЕ 7 устройства. Вход 19 установки в исходное состояние средств функционального контроля устройства соединен с Rp- входами триггеров 6.1-6.5. Выход элемента И-НЕ 7 устройства соединен с R-входами триггеров 6.1-6.5.

Прямой выход триггера 6.1 соединен с первым входом первой группы входов элемента 2-2И-ИЯИ 8.1. Инверсный выход Отказ триггера 6.1 соединен с вторым входом первой группы входов элемента 2- 2И-ИЛИ 8.1 и с первым входом первой группы входов элемента 2-2И-ИЛИ 10.1, Прямой выход Отказ триггера 6.1 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 8.1, с входом по ИЛИ элемента 3-2И-ИЛИ 9.1, с вторым входом второй группы входов элемента 2- 2И-ИЛИ 10.1 и с вторыми входами элементов ИЛИ/ИЛИ-НЕ 11.1 и И 12.1. Выход элемента 3/2И-ИЛИ 9.1 соединен с t-вхо- дом триггера 6.2, счетный вход которого соединен с выходом элемента 2-2И-ИЛИ 10.1.

Прямой выход триггера 6.2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 10.2, с вторым входом второй группы входов элемента 2-2И-ИЛИ 8.1, с первым входом первой группы входов элемента 2-2И-ИЛИ 8.2 и с первым входом первой группы входов элемента 3- 2И-ИЛИ 9.2. Прямой выход Отказ триггера 6.2 соединен с первыми входами элементов ИЛИ/ИЛИ-НЕ 11.1 и И 12.1. Выход элемента 2-2Й-ИЛИ 10.2 соединен с Ьвходом триггера 6.3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 11.1 соединен с вторым входом вtopoй группы входов эле- ента 2-2И-ИЛИ 10.2 и с вторым входом

первой группы входов элемента 2-2И- ИЛИ 8.2. Прямой выход элемента 2-2И- ИЛИ 11.1 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 5 8.2, с вторым входом первой группы входов элемента 2-2И-ИЛИ 10.2 и с вторыми входами элементов ИЛИ/ИЛИ-НЕ 11.2 и И 12.2.

Инверсный выход триггера 6.3 соеди- 0 нен с первым входом первой группы входов элемента 3-2И-ИЛИ 9.1. Прямой выход триггера 6.3 соединен с вторым входом второй группы входов элемента 2-2И- ИЛИ 8.2, с первым входом первой группы 5 входов элемента 2-2И-ИЛИ 8.3, с первым входом первой группы входов элемента 2- 2И-ИЛИ 10.4, с вторым входом второй группы входов элемента 3-2И-ИЛИ 9.2 и с первым входом первой группы входов эле0 мента 2-2И-ИЛИ 10.3. Инверсный выход Отказ триггера 6.3 соединен с вторым входом первой группы входов элемента 3- 2И-ИЛИ 9.1 и с первым входом второй группы входов элемента 2-2И-ИЛИ 9.2.

5 Прямой выход Отказ триггера 6.3 соединен с вторым входом второй группы входов элемента 3-2И-ИЛИ 9.1, с вторым входом первой группы входов элемента 3- 2И-ИЛ1/1 9.2, с первым входом элемента

0 ИЛИ/ИЛИ-НЕ 11.2. с первым входом элемента И 12.2.

Инверсный выход элемента ИЛИ/ИЛИ-НЕ 11.2 соединен с вторым входом первой группы входов элемента 25 2И-ИЛИ 8.i3, с вторым входом первой группы входов элемента 2-2И-ИЛИ 10.3. Прямой выход элемента ИЛИ/ИЛИ-НЕ 11.2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 8.3, с

0 первым входом второй группы входов элемента 2-2И-ИЛИ 10.3, с вторым входом второй группы входов элемента 2-2И-ИЛИ 10.4 и с вторыми входами элементов ИЛИ/ИЛИ-НЕ 11.3 и И 12.3. Выход эле5 мента 3-2И-ИЛИ 9.2 соединен с 1-входом триггера 6-4, счетный вход которого соединен с выходом элемента 2-2И-ИЛИ 10.3.

Инверсный выход триггера 6.4 соединен с первым входом второй группы вхо0 дов элемента 3-2И-ИЛИ 9.1 и с первым входом первой группы входов элемента 2- 2И-ИЛИ 10.2. Прямой выход триггера 6.4 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 8.3, с первым

5 входом первой группы входов элемента 2- 2И-ИЛИ 8.4 и с первым входом второй группы входов элемента 2-2И-ИЛИ 10.4. Прямой выход Отказ триггера 6.4 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 10.4 и с первыми

входами элементов ИЛИ/ИЛИ-НЕ 11.3 и И 12.3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 11.3 соединен с входом по ИЛИ третьей группы входов элемента 3- 2И-ИЛИ 9.2 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 8.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ 11.3 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 8.4 и с вторыми входами элементов ИЛИ 13 и И 12.4. Выход элемента 2-2И-ИЛИ 10.4 соединен с счетным входом триггера 6.5.

Прямой выход триггера 6.5 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 8.4. Прямой выход Отказ триггера 6.5 соединен с первыми входами элементов ИЛИ 13 и И 12.4. Выходы элементов И 12.1-12.4 соединены соответственно с первым, вторым, третьим и четвертым входами элемента ИЛИ 14.

Выходы элементов 2-2И-ИЛИ 8.1-8.4 являются соответствующими информационными выходами 20.1-20.4 устройства. Выход элемента ИЛИ 13 является выходом 21 Частичный отказ устройства. Выход элемента ИЛИ 14 является выходом 22 Отказ устройства.

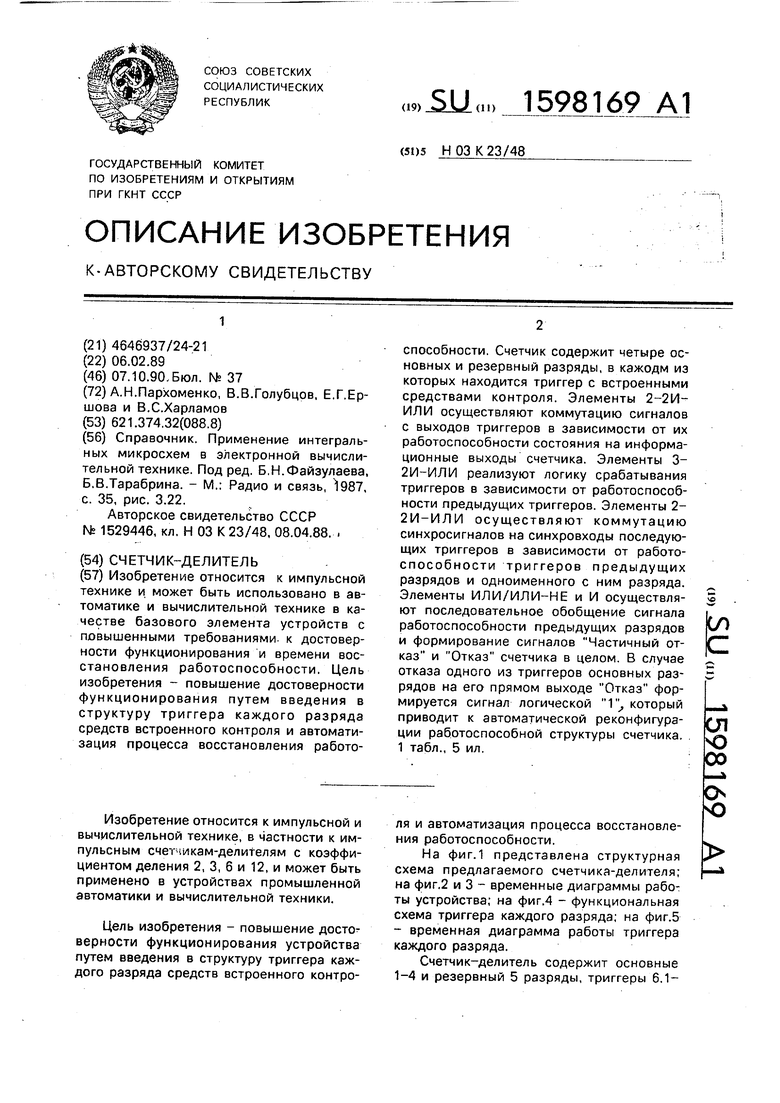

Триггер каждого канала (фиг.4) содержит первый 23 и второй 24 элементы И- ИЛИ-НЕ, первый 25 и второй 26 элементы И, четыре элемента И-НЕ 27-30, первый 31 и второй 32 элементы НЕ, четвертый 33 и третий 34 элементы И, элемент И/И-НЕ 35, элемент И-ИЛИ/И-ИЛИ НЕ 36.

R-вход триггера каждого канала (фиг.4) соединен с вторым входом первой, с первым входом второй групп входов элемента И-ИЛИ-НЕ 23, с первым входом элемента И-НЕ 30, с первым входом элемента И 25 и с первым входом элемента И 34. 1-вход 38 триггера соединен с третьим входом второй группы входов элемента И-ИЛИ- НЕ 23, с вторым входом элемента И-ИЛИ- НЕ 35 и с вторым входом третьей группы входов элемента И-ИЛИ/И-ИЛИ-НЕ 36. Синхровход триггера соединен с входом элемента НЕ 31, с четвертым входом 39 второй группы входов элемента И-ИЛИ- НЕ 23 и с первым входом первой группы входов элемента И-ИЛИ-НЕ 24. К-вход 40 триггера соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ 24, с первым входом элемента И/И-НЕ 35 и с первым входом четвертой группы входов элемента И-ИЛИ/И-ИЛИ-НЕ 36. S- вход 41 триггера соединен с четвертым входом первой, с первым входом второй групп входов элемента И-ИЛИ-НЕ 24, с вторым входом элемента И 34, с третьим входом элемента И 26 и с третьим входом

элемента И-НЕ 29. Вход 42 установки в исходное состояние средств функционального контроля триггера соединен с первым входом седьмой группы входов элемента И-ИЛИ/И-ИЛИ-НЕ 36,

Выход элемента И-ИЛИ-НЕ 23 соединен с вторым входом элемента И 26 и с вторым входом второй группы входов элемента И-ИЛИ-НЕ 24. Выход элемента И0 ИЛИ-НЕ 24 соединен с вторым входом элемента И 25 и с первым входом первой группы входов элемента И-ИЛИ-НЕ 23. X Выход элемента И 25 соединен с первым входом элемента И-НЕ 27, с третьим

5 входом второй, с вторым входом четвертой и с вторым входом пятой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36. Выход элемента НЕ 31 соединен с вторым входом элемента И-НЕ 27, с первым входом зле0 мента И-НЕ 28, с третьим входом первой и с третьим входом второй групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36. Выход элемента И 26 соединен с вторым входом элемента И-НЕ 28, с четвертым входом

5 первой, с первым входом третьей и с вторым входом шестой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36.

Выход элемента И-НЕ 27 соединен с вторым входом элемента И-НЕ 29. с пер0 вым входом элемента И 33 и с первым входом элемента И 26. Выход элемента И-НЕ 28 соединен с третьим входом элемента И 25, с вторым входом элемента И 33 и с вторым входом элемента И-НЕ 30. Выход

5 элемента И 33 соединен с третьим входом третьей, с третьим входом четвертой, с третьим входом пятой и с третьим входом шестой групп входов элемента И-ИЛИ/И- ИЛИ-НЕ 36. Выход элемента И 33 допол0 нительно соединен с входом элемента НЕ 32. Выход элемента НЕ 32 соединен с вторым входом первой и с первым входом второй , групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36.

5 Выход элемента И 34 соединен с пятыми входами первой и второй, с четвертыми входами третьей, четвертой, пятой и шестой Групп входов элемента И-ИЛИ/И- ИЛИ-НЕ 36.

0Инверсный выход элемента И/И-НЕ

35 соединен с пятыми входами третьей и четвертой групп входов элемента И- ИЛИ/И-ИЛИ-НЕ 36. Прямой выход элемента И/И-НЕ 35 соединен с пятыми

5 входами пятой и шестой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36.

Выход Элемента И-НЕ 29 является прямым выходом триггера каждого разряда и соединен с третьим входом элемента . И-НЕ 30, с третьим входом первой группы

входов элемента И-ИЛИ-НЕ 24 и с первыми входами первой и пятой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ 36. Выход элемента И-НЕ 30 является инверсным выходом 44 триггера каждого разряда и соединен с первым входом элемента И-НЕ 29, с вторым входом второй группы входов элемента И-ИЛИ-НЕ 23, с четвертым входом второй и с первым входом шестой групп входов элемента И-ИЛИ/И-ИЛИ- НЕ 36, инверсный выход элемента И- ИЛИ-И-ИЛИ-НЕ 36 является инверсным выходом 45 Отказ триггера каждого разряда. Прямой выход элемента И-ИЛИ/И- ИЛИ-НЕ 36 является прямым выходом 46 Отказ триггера каждого разряда и соединен с вторым входом своей седьмой группы входов.

Элементы, входящие в структуру триггера каждого разряда, выполняют следующее функциональное назначение.

Элементы И-ИЛИ-НЕ 23 и 24, И 25 и 26, НЕ 31 и И-НЕ 27 и 28 образуют схему вспомогательного триггера с входной логикой работы I К-или RS-трмггера.

Элементы И-НЕ 29 и 30 образуют схему основного триггера.

Элемент НЕ 31 предназначен для организации двухтактного режима работы триггера каждого разряда при наличии одного тактового входа 39. Кроме того, на выходе злемента НЕ 31 вырабатывается сигнал разрешения сравнения сигналов на противоположных плечах (выходах) основного и вспрмогател ного триггеров (фиг.4, точка А м Q, точка А и Q) в режиме хранения информации.

Элемент И 33 обеспечивает контроль наличия сигнала запрета работы основного триггера и формирует на своем выходе сигнал строба сравнения, задержанного относительно положительного фронта тактового сигнала на входе 39 на время не менее ЗТ, (где Т - время задержки логического элемента), т.е. на время срабатывания элемента НЕ 9, И-НЕ 5 или 7, а также на время срабатывания самого элемента И 33, Особенностью элемента И 33 является то, что его время срабатывания должно быть не менее Т, т.е. если для всех остальных логических элементов структуры триггера каждого канала время срабатывания возможно не более Т, то для элемента И 32 оно должно быть не менее Т. Данное ограничение можно выполнить при разработке технологии микросхемы.

Элемент НЕ 33 предназначен для формирования на своем выходе сигнала строба сравнения, задержанного на время 4Т

относительно отрицательного фронта тактового сигнала на входе 39.

Элемент И 34 предназначен для формирования сигнала запрета сравнения во 5 второй, третьей, четвертой, пятой, шестой и седьмой структурах И элемента И- ИЛИ/И-ИЛИ-НЕ 36 в момент асинхронной установки триггера каждого разряда по его входам 37 и 41 соответственно в 10 нулевое или единичное состояние.

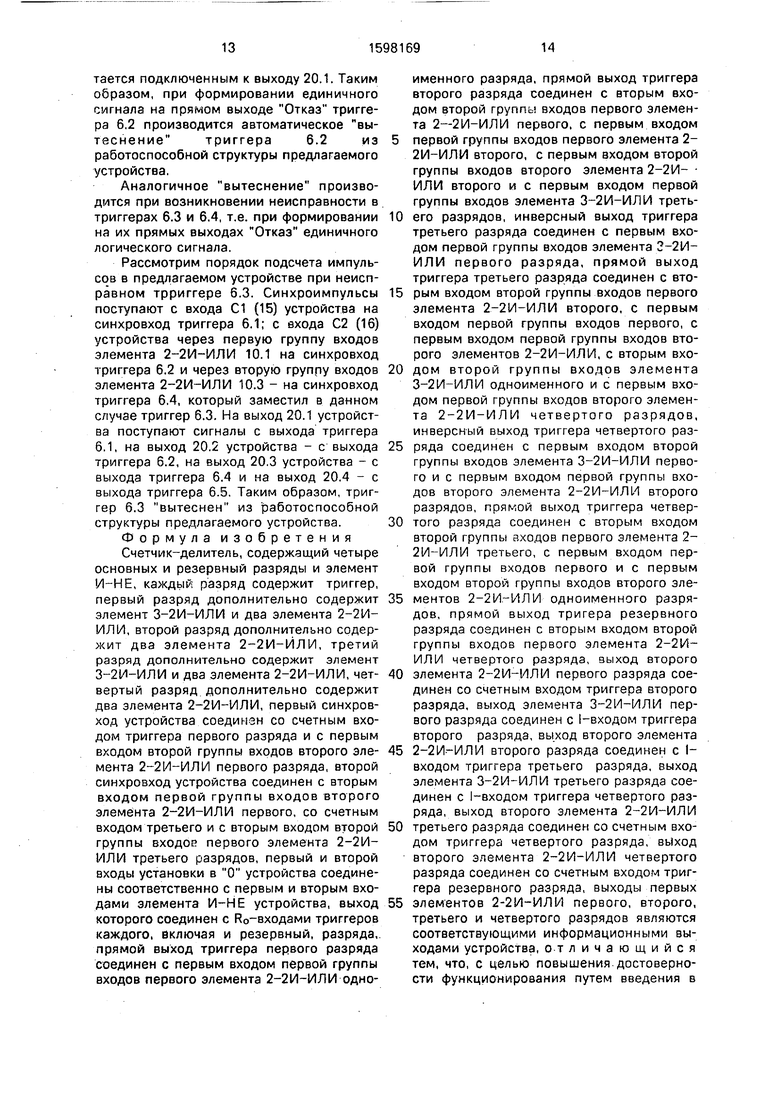

Элемент И/И-НЕ 35 на своем прямом и инверсном в 1хрдах формирует сигнал функций 1°К и 1 которыми открываются соответственно шестая, седьмая, а также 15 четвертая и пятая структуры по И элемента И-ИЛИ/И-ИЛИ-НЕ 36, который осуществляет на своих входах структур по И контроль правильности срабатывания всех логических элементов структуры 11 -тригге- 20 ра. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера каждого разряда) на выходе 46 элемента И-ИЛИ/И- ИЛИ-НЕ 36 формируется сигнал Отказ, 25 который посредством своей обратной связи через вход первой структуры по И осуществляет так называемый эффект самозахвата, т.е. устанавливается в устойчивое состояние логической единицы, 30 В общем случае на входах элемента И- ИЛИ/И-ИЛИ НЕ 36 реализуется функционал отказа, который можно представить следующим аналитическим выражениемF /CIKRS/.-AV/cTKRS/-AV/CiKRS/-A-QV 5 /CIKRS/-A-QVCAQRSVCAQRS,

где С, С - единичное и нулевое состояния тактового сигнала на входе 39 триггера;

1, I - единичное и нулевое состояния сигнала на входе 38 триггера: 0 К, К - единичное и нулевое состояния сигнала на входе 40 триггера,R - единичное состояние сигнала на входе 37 триггера:

S - единичное состояние сигнала на 5 входе триггера:

А, А - единичное и нулевое состоя ния сигнала соответственно в точках А и А на фиг.4:

Q, Q - состояния сигналов на прямом 0 и инверсном (43 и 44 соответственно) выходах 45 триггера.

Таким образом, счетчик-делитель имеет в каждом разряде триггер с встроенными средствами контроля, которые в случае 5 отказа какого-либо логического элемента структуры любого из триггеров формируют сигнал Отказ на его прямом выходе 46.

Рассмотрим функциональное назначение элементов структуры предлагаемого счетчика-делителя.

Элементы 2-2И-ИЛИ 8.Ь8.4 предназначены для коммутации на соответствующие информационные выходы 20.1-20.4 устройства значений сигналов с прямых выходов триггеров данного или последующего разрядов, в зависимости от исправного или неисправного состояния триггера данного или какого-либо предыдущего разрядов.

Элементы 3-2И-ИЛИ 9.1 и 9.2 обеспечивают правильный алгоритм функционирования триггеров 6.2 и 6.4 по их 1-входам в зависимости от исправности (неисправности) триггеров предыдущих разрядов.

Элемент 2-2И-ИЛИ 10.1 предназначен для коммутации синхросигналов с первого 15 или второго 16 синхровходов устройства, в зависимости от исправного (неисправного) состояния триггера 6.1.

Элемент 2-2И-ИЛИ 10.2 предназначен для коммутации сигнала на -входе триггера 6.3, лмбо с прямого выхода триггера 6.2 (в случае исправности триггеров 6.1 и 6.2), либо с инверсного выхода триггера 6.4 (при неисправности одного из триггеров 6.1 или 6.2).

Элемент 2-2И-ИЛИ 10.3 предназначен для коммутации сигнала, поступающего на синхровход триггера 6.4. При исправном состоянии триггеров 6.1-6.3 через элемент 2-2И-ИЛИ 10.3 проходит сигнал с выхода триггера 6.3. При неисправном состоянии одного из триггеров 6.1-6.3 через элемент 2-2И -ИЛИ 10.3 проходит сигнал с второго 16 синхровхода устройства.

Элемент 2-2И-ИЛИ 10.4 предназначен для коммутации сигнала, поступающего на синхровход резервного триггера 6.5. При неисправном состоянии одного из триггеров 6.1-6.4 через элемент 2-2И- ИЛИ 10.4 проходит сигнал с прямого выхода триггера 6.4. При неисправном состоянии триггера 6.4 через элемент 2- 2И-ИЛИ проходит сигнал с прямого выхода триггера 6.3. Элементы ИЛИ/ИЛИ-НЕ 11.1-11.3 осуществляют последовательное обобщение исправного (неисправного) состояния триггеров соответствующих и предыдущих им разрядов. На своих прямом и инверсном выходах они формируют сигналы, которые управляют работоспособной конфигурацией устройства.

Элементы И 12.1-12.4 осуществляют формирование сигнала Отказ устройства а целом. Условием формирования этого сигнала является отказ двух и более триггеров разрядов.

Элемент ИЛИ 13 формирует сигнал Частичный отказ устройства. Условием формирования этого сигнала является отказ хотя бы одного из триггеров 6.1-6.5 разрядов.

Счетчик-делитель работает следующим образом.

Для установки счетчика-делителя в ис- 10 ходное состояние на входы 17 и 18 подаются сигналы логической единицы. При этом все триггеры 6.1-6.5 устанавливаются в нулевое состояние. Для установки в исходное состояние средств функционально- 15 го контроля устройства на вход 19 подается сигнал логического нуля.

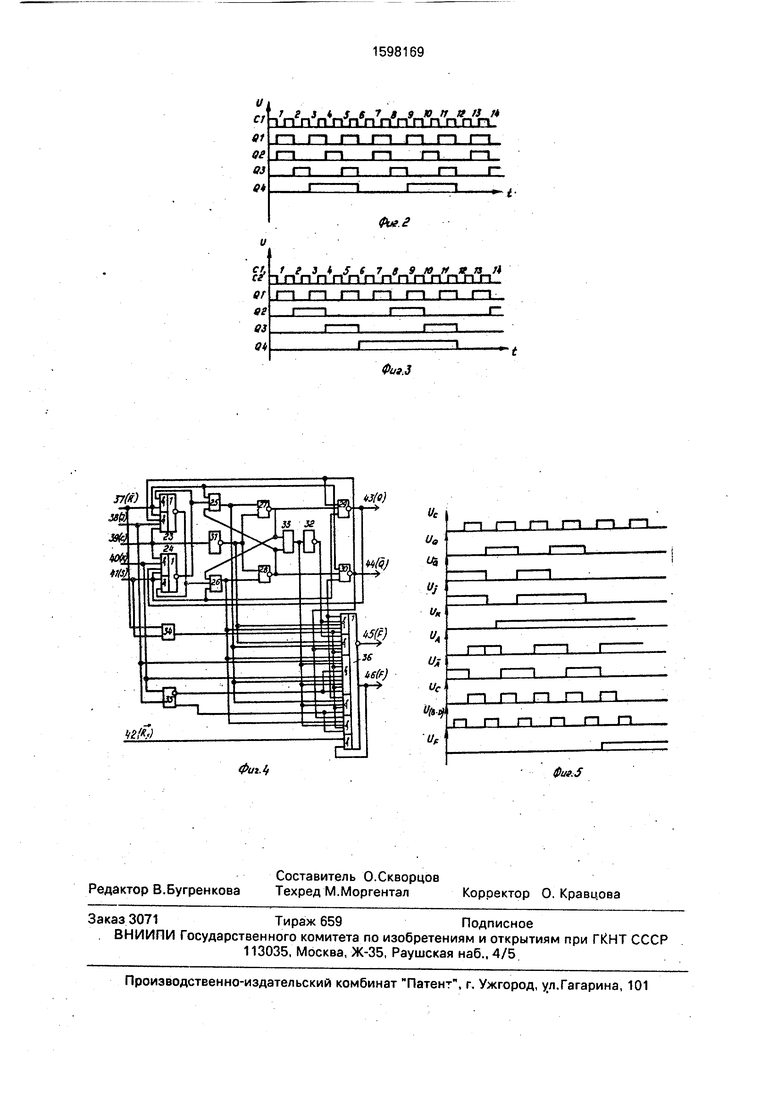

Счетчик-делитель работает в трех режимах: деление частоты на 2 и 6; деление частоты на 2, 6 и 12 одновременно и деле- 20 ние частоты на 6 и 3.

Рассмотрим подробнее каждый из трех режимов работы счетчика-делителя.

В первом режиме (деление 2 и 6) и при исправном состоянии триггеров 6.1-6.4 25 счетчик-делитель работает следующим образ :iM.

На выходах (прямых) Отказ триггеров 6.1-6.4 присутствуют сигналы логического нуля, а на инверсного выходе Отказ триг- 30. гера 6.3 - сигнал логической единицы. В этом случае на инверсных выходах элементов ИЛИ/ИЛИ-НЕ 11.2-11.3 присутствуют сигналы логическом единицы, а на их прямых выходах - сигналы логического нуля. 35 На выходах 21 Частичный отказ и 22 От-: каз устройства присутствуют сигналы логического нуля.

Следовательно единичным разрешающим сигналом открываются следующие ло- 0 гические элементы структуры устройства; первые группы входов элементов 2-2И- ИЛИ 8.1-8.4, первая группа входов элемента 3-2И-ИЛИ 9.1, первая группа входов элемента 2-2И-ИЛИ 10.1, вторая 5 группа входов элемента 2-2И-ИЛИ 10.2, вторая Труппа входов элемента 3-2И-ИЛИ 9.2, первая группа входов элемента 2-2И- ИЛИ 10,3. Одновременно с этим закрываются следующие логические элементы 0 структуры устройства: вторые группы входов элементов 2-2И-ИЛИ 8.1-8.4, вторая и третья группы входов элемента 3-2И-ИЛИ 9.1, вторая группа входов элемента 2-21/ - ИЛИ 10.1. первая группа входов элемента 5 2-2И-ЙЛИ 10.2, первая группа входов элемента 3-2И-ИЛИ 9,2, вторая группа входов элемента 2-2И-ИЛИ 10.3. Заметим, что элемент 2-2И-ИЛИ 10.4 в этом случае закрыт как по первой, так и по второй группам входов.

В этом случае на выходы 20.1-20.4 устройства через первые группы входов соответствующих элементов 2-2И-ИЛИ 8.1-8.4 поступают сигналы с прямых выходов одноименных им триггеров 6.1-6.4. Триггер- 6.5 находится в горячем резерве. Деление частоты на 2, поступающей на первый синхровход 15 устройства, осуществляется триггером 6,1. Деление частоты на 3 осу- ш,ествляется триггерами 6.2 м 6.3, так как на 1-вход триггера 6.2 через первую группу входов элемента 3-2И-ИЛИ 9.1 поступает сигнал с инверсного выхода триггера 6.3. Деление частоты на 6 осуществляется триггером 6.4, так как на его синхровход через первую группу входов элемента 2- 2И-ИЛИ 10.3 поступает сигнал с выхода триггера 6.3При необходимости деления частоты на 12 выход 20.1 устройства соединяют с входом С2 (16).

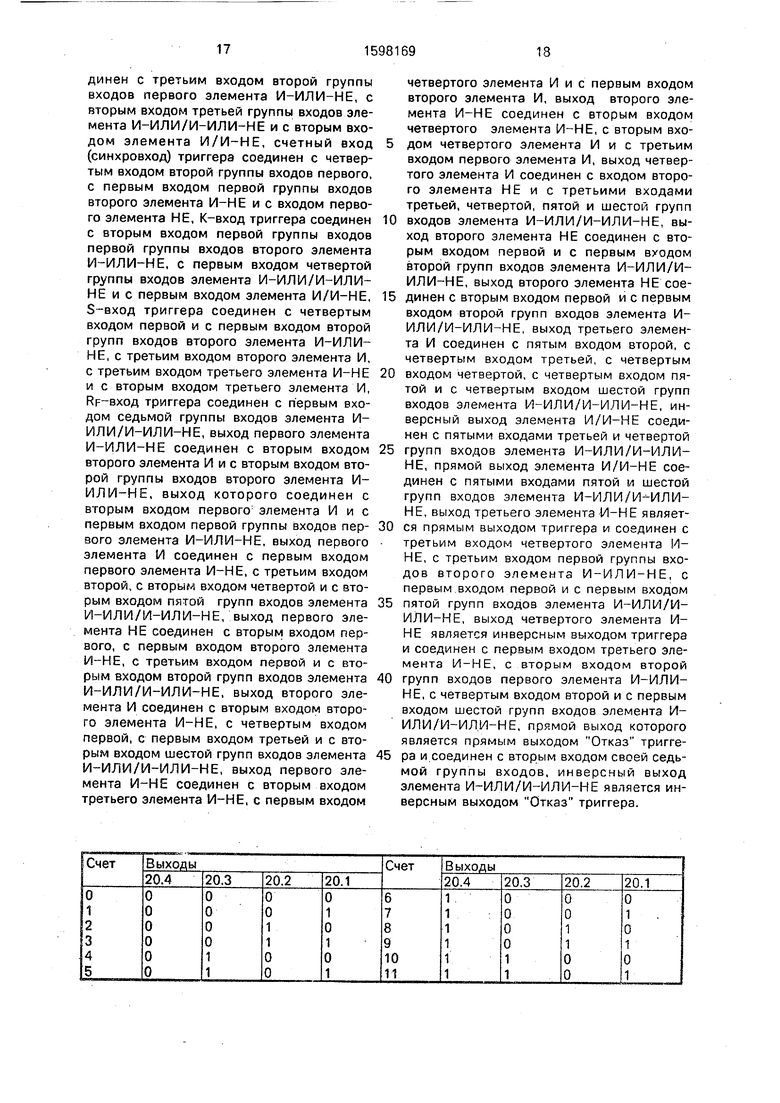

В таблице представлены данные работы устройства.

В режиме деления частоты следования на 2, 3 и 6 подсчет импульсов в устройстве производится по следующим логическим цепям, С входа С1 (15) - на синхровход триггера 6.1 (деление на 2). С выхода триггера 6.1 через первую группу аходов элемента 2-2И-ИЛИ 8.1 на выход 20.1 устройства. С входа С2 (16) через первую группу входов элемента 2-2И-ИЛИ 10.1 - на синхровход триггера 6.2 м с входа С2 (16) непосредственно на смнхровход триггера 6.3. Логику деления на 3 реализуют KOHCTpv/ктмвные связи 1-входов триггеров

6.2и 6.3 с инверсным выходом триггера

6.3и прямым выходом триггера 6.2 соот- аетстве.нно через соответствующие группы входов элементов 3-2И-ИЛИ 9.1 и 2-2И- ИЛИ 10.2. Сигналы с выходов триггеров 6.2 и 6.3 поступают на одноименные мм выходы 20.2 и 20.3 устройства через первые группы входов соответствующих им элементов 2-2И-ИЛИ 8.2 и 8,3 соответственно. Синхронизирующий сигнал триггера

6.4поступает на его синхровход с выхода триггера 6.3 через первую группу входов элемента 2-2И-ИЛИ 10.3.

Врврченная диаграмма работы устройства в этом режиме показана на фиг.2.

При делении частоты следования на 12 вход 20.1 устройства соединяют с входом 02 (16), а не подают изначальную частоту следования параллельно, как это было в первом случае, на оба входа С1 (15) и С2 (13) синхронизации устройства.

Временная диаграрлма работы устройства в этом режиме показана на фиг.З.

Рассмотрим примеры работы предлагаемого устройства при отказе одного из основных триггеров 6.1-6.4.

При отказе триггера 6.1 на прямом его

выходе Отказ формируется сигнал логической единицы, а на инверсном выходе Отказ - сигнал логического нуля.

При этом на прямом и инверсном выходах элементов ИЛИ/ИЛИ-НЕ происхо0 дит смена состояний сигналов на противоположные. В результате закроются первые группы входов- элементов 2-2И- ИЛИ 8.1-8.4, откроется третья структура по ИЛИ элемента 3-2И-ИЛИ 9.1, откроют5 ся вторые группы входов элементов 2-2И- ИЛИ 8,1-8.4, закроется первая и откроется вторая группа входов элемента 2-2Й-ИЛИ 10.1, откроется первая м закроется вторая групппь входов элемента 2-2И-ИЛИ 10.2,

0 закроется третья структура по ИЛИ элемента 3-2И-ИЛ1/1 9.2, закроется первая м откроется вторая группа входов элемента 2-2И-ИЛИ 10,3, откроется вторая группа входов элемента 2-2И-ИЛИ 10.4. На выхо5 де элемента ИЛИ 13 будет сформирован единичный логический уровень сигнала, который поступит на выход 21 Частичный отказ устройства.

Таким образом, формированме единич0 ного сигнала на прямом выходе Отказ триггера 6.1 приводит к автоматической реконфигурации работоспособной структуры устройства, при которой триггер 6.1 вытесняется из этой структуры и замещается

5 триггером 6,2, вместо которого подключается триггер 6.3, триггер 6.3 замещается триггером 6.4, а триггер 6.4 - замещается триггером 6.5. При этом выходы устройства остаются неизменными.

0 В случае неисправности триггера 6.2 на его прямом выходе Отказ формируется сигнал логической единицы, который также приводит к смене сигналов на выходах (прямом и инверсном) элементов

5 ИЛИ/ИЛИ-НЕ 11.1-11.3, что, в свою очередь, закроет первые и откроет вторые группы входов элементов 2-2И-ИЛИ 8.2- 8.4, откроет первую и закроет вторую группу входов элемента 2-2И-ИЛИ 10.2,

0 закроет третью структуру элемента 3-2И- ИЛИ по ИЛИ 9.2, при этом остается открытой вторая структура по И этого элемента 3-2И-ИЛИ 9.2, закроет первую и откроет вторую группу входов элемента 2-2И-ИЛИ

5 10.3, откроет вторую группу входов элемента 2-2И-ИЛИ 10.4.

В результате триггер 6,2 отключается м вместо него подключается триггер 6.3, триггер 6.3 замещается триггером 6.4, а триггер 6.4 - триггером 6.5. Триггер 6.1 остается подключенным к выходу 20.1. Таким образом, при формировании единичного сигнала на прямом выходе Отказ триггера 6.2 производится автоматическое вытеснение триггера 6.2 из работоспособной структуры предлагаемого устройства.

Аналогичное вытеснение производится при возникновении неисправности в триггерах 6.3 и 6,4, т.е. при формировании на их прямых выходах Отказ единичного логического сигнала.

Рассмотрим порядок подсчета импульсов в предлагаемом устройстве при неисправном трриггере 6.3. Синхроимпульсы поступают с входа С1 (15) устройства на синхровход триггера 6.1; с входа С2 (16) устройства через первую группу входов элемента 2-2И-ИЛИ 10.1 на синхровход триггера 6.2 и через вторую группу входов элемента 2-2И-ИЛИ 10.3 - на синхровход триггера 6.4, который заместил в данном случае триггер 6.3. На выход 20.1 устройства поступают сигналы с выхода триггера 6.1, на выход 20.2 устройства - с выхода триггера 6.2, на выход 20.3 устройства - с выхода триггера 6.4 и на выход 20.4 - с выхода триггера 6.5. Таким образом, триггер 6.3 вытеснен из работоспособной структуры предлагаемого устройства.

Формула изобретения

Счетчик-делитель, содержащий четыре основных и резервный разряды и элемент 1/1-НЕ, каждый разряд содержит триггер, первый разряд дополнительно содержит элемент 3-2И-ИЛИ и два элемента 2-2И- ИЛИ, второй разряд дополнительно содержит два элемента 2-2И-ЙЛИ, третий разряд дополнительно содержит элемент 3-2И-ИЛИ и два элемента 2-2И-ИЛИ, чет- вертый разряд дополнительно содержит два элемента 2-2И-ИЛИ, первый синхровход устройства соединен со счетным входом триггера первого разряда и с первым входом второй группы входов второго эле- мента 2-2И-ИЛИ первого разряда, второй синхровход устройства соединен с вторым входом первой группы входов второго элемента 2-2И-1/1ЛЙ первого, со счетным входом третьего и с вторым входом второй группы входов первого элемента 2-2И- ИЛИ третьего разрядов, первый и второй входы установки в О устройства соединены соответственно с первым и вторым входами элемента И-НЕ устройства, выход которого соединен с Ro-входами триггеров каждого, включая и резервный, разряда, прямой выход триггера первого разряда соединен с первым входом первой группы входов первого элемента 2-2И-ИЛИ одноименного разряда, прямой выход триггера второго разряда соединен с вторым входом второй группы входов первого элемента 2-2И-ИЛИ первого, с первым входом первой группы входов первого элемента 2- 2И-ИЛИ второго, с первым входом второй группы входов второго элемента 2-2И- ИЛИ второго и с первым входом первой группы входов элемента 3-2И-ИЛИ третьего разрядов, инверсный выход триггера третьего разряда соединен с первым входом первой группы входов элемента 3-2И- ИЛИ первого разряда, прямой выход триггера третьего разряда соединен с вторым входом второй группы входов первого элемента 2-2И-ИЛИ второго, с первым входом первой группы входов первого, с первым входом первой группы входов второго элементов 2-2И-ИЛИ, с вторым входом второй группы входов элемента 3-2И-ИЛ1/1 одноименного и с первым входом первой группы входов второго элемента 2-2И-ИЛИ четвертого разрядов, инверсный выход триггера четвертого разряда соединен с первым входом второй группы входов элемента 3-2И-ИЛИ первого и с первым входом первой группы входов второго элемента 2-2И-ИЛИ второго разрядов, прямой выход триггера четвертого разряда соединен с вторым входом второй группы входов первого элемента 2- 2И-ИЛИ третьего, с первым входом первой группы входов первого и с первым входом второй группы входов второго элементов 2-2И-ИЛИ одноименного разрядов, прямой выход тригера резервного разряда соединен с вторым входом второй группы входов первого элемента 2-2И- ИЛИ четвертого разряда, выход второго элемента 2-2И-ИЛИ первого разряда соединен со счетным входом триггера второго разряда, выход элемента 3-2И-ИЛИ первого разряда соединен с 1-входом триггера второго разряда, выход второго элемента 2-2И-ИЛИ второго разряда соединен с I- входом триггера третьего разряда, выход элемента 3-2И-ИЛИ третьего разряда соединен с 1-входом триггера четвертого разряда, выход второго элемента 2-2И-ИЛИ третьего разряда соединен со счетным входом триггера четвертого разряда, выход второго элемента 2-2И-ИЛИ четвертого разряда соединен со счетным входом триггера резервного разряда, выходы первых элементов 2-2И-ИЛИ первого, второго, третьего и четвертого разрядов являются соответствующими информационными выходами устройства, от личающийся тем, что, с целью повышения достоверности функционирования путем введения в

структуру триггера каждого разряда средств встроенного контроля и автоматизации процесса восстановления |эабото- способности, в него дополнительно введены во второй, третий и четвертый разряды элементы ИЛИ/ИЛИ-НЕ и И, а резервный разряд дополнительно содержит два элемента ИЛИ и элемент И, вход RF установки в исходное состояние средств функционального контроля устрой- ства соединен с Яр-входами триггеров каждого, включая и резервный, разряда, инверсный выход Отказ триггера первого разряда соединен с вторым входом первой группы входов первого и с первым входом первой группы входов второго элементов 2- 2И-ИЛИ одноименного разряда, прямой выход Отказ триггера первого разряда соединен с первым входом второй группы входов первого, с вторым входом второй группы входов второго элементов 2-2И- ИЛИ и с входом по ИЛИ третьей структуры элемента 3-2И-ИЛИ одноименного, а также с вторым входом элемента ИЛИ/ИЛИ- НЕ и с вторым входом элемента И второго разрядов, прямой выход Отказ триггера второго разряда соединен с первыми входами элементов И и ИЛИ/ИЛИ-НЕ одноименного разряда, инверсный выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с вторым входом первой группы входов первого и с вторым входом второй группы входов двторого элементов 2-2И- ИЛИ одноимённого разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с первым входом второй групппы входов первого, с вторым входом первой группы входов второго элементов 2-2И-ИЛИ одноименного и с вторыми входами элементов ИЛИ/ИЛИ-НЕ и И третье- го разрядов, выход элемента И второго разряда соединен с четвертым входом второго элемента ИЛИ резервного разряда, инверсный выход Отказ триггера третьего разряда соединен с вторым входом пер- вой группы входов элемента 3-2И-ИЛИ первого разряда, прямой выход Отказ триггера третьего разряда соединен с вторым входом второй группы входов элемента 3-2И-ИЛИ первого и с первыми входами элементов ИЛИ/ИЛИ-НЕ и И одноименного разрядов, инверсный выход элемента ИЛИ/ИЛИ-НЕ третьего разряда соединен с вторым входом первой группы входов первого, с вторым входом первой группы входов второго элементов 2-2И- ИЛИ и с первым входом второй группы входов элемента 3-2И-ИЛИ одноименного разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ третьего разряда соединен

с первым, входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ, с вторым входом первой группы входов элемента 3-2И-ИЛИ одноименного и с вторыми входами элементов И и ИЛИ/ИЛИ-НЕ четвертого разрядов, выход элемента И третьего разряда соединен с третьим входом второго элемента ИЛИ резервного разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ третьего разряда дополнительно соединен с вторым входом второй группы входов второго элемента 2-2И- ИЛИ четвертого разряда, выход Отказ триггера четвертого разряда соединен с вторым входом первой группы входов второго элемента 2-2И-ИЛИ и с первыми входами элементов ИЛИ/ИЛИ-НЕ и И одноименного разряда, инверсный выход элемента ИЛИ/ИЛИ-НЕ четвертого разряда соединен с вторым входом первой группы входов первого элемента 2-2И-ИЛ1/1 одноименного разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ четвертого разряда соединен с первым входом второй группы входов первого элемента 2-2И-ИЛИ одноименного и с вторыми входами первого элемента ИЛИ и элемента И резервного разрядов, выход элемента И четвертого разряда соединен с вторым входом второго элемента ИЛИ резервного разряда, первый вход которого соединен с выходом элемента И резервного разряда, прямой выход Отказ триггера резервного разряда соединен с первыми входами первого элемента ИЛИ и элемента И одноименного разряда, выход первого элемента ИЛИ резервного разряда является выходом Частичный отказ устройства, аыход второго элемента ИЛИ резервного разряда является выходом Отказ устройства, а триггер каждого разряда содержит два элемента И-ИЛИ-НЕ с временем срабатывания не более Т (где Т - время срабатывания, одинаковое для всех логических элементов), два элемента НЕ с временем срабатывания не более Т, три элемента И с временем срабатывания не более Т. четыре элемента И-НЕ с временем срабатывания не более Т. четвертый элемент И с временем срабатывания не менее Т. элемент И/И-НЕ с временем срабатывания не более Т и эле- л;ент И-ИЛИ/И-ИЛИ-НЕ с временем срабатывания не более Т. R-вход триггера соединен с вторым входом первой и с первым входом второй групп входов первого элемента И-ИЛИ-НЕ, с первым входом первого рлемента И. с первым входом четвертого улемента И-НЕ и с первым входом третьего элемента И. 1-вход триггера соединен с третьим входом второй группы входов первого элемента И-ИЛИ-НЕ, с вторым входом третьей группы входов элемента И-ИЛИ/И-ИЛИ-НЕ и с вторым входом элемента И/И-НЕ, счетный вход (синхровход) триггера соединен с четвертым входом второй группы входов первого, с первым входом первой группы входов второго элемента И-НЕ и с входом первого элемента НЕ, К-вход триггера соединен с вторым входом первой группы входов первой группы входов второго элемента И-ИЛИ-НЕ, с первым входом четвертой группы входов элемента И-ИЛИ/И-ИЛИ- НЕ и с первым входом элемента И/И-НЕ, S-вход триггера соединен с четвертым входом первой и с первым входом второй групп входов второго элемента И-ИЛИ- НЕ, с третьим входом второго элемента И, с третьим входом третьего элемента И-НЕ и с вторым входом третьего элемента И, RF-ВХОД триггера соединен с первым входом седьмой группы входов элемента И- ИЛИ/И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с вторым входом второго элемента И и с вторым входом второй группы входов второго элемента И- ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И и с первым входом первой группы входов пер- вого элемента И-ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента И-НЕ, с третьим входом второй, с вторым входом четвертой и с вторым входом пятой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ, выход первого элемента НЕ соединен с вторым входом первого, с первым входом второго элемента И-НЕ, с третьим входом первой и с вторым входом второй групп входов элемента И-ИЛИ/И-ИЛИ-НЕ, выход второго элемента И соединен с вторым входом второго элемента И-НЕ, с четвертым входом первой, с первым входом третьей и с вторым входом шестой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ, выход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, с первым входом

четвертого элемента И и с первым входом второго элемента И, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, с вторым входом четвертого элемента И и с третьим входом первого элемента И, выход четвертого элемента И соединен с входом второго элемента НЕ и с третьими входами третьей, четвертой, пятой и шестой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ, выход второго элемента НЕ соединен с вторым входом первой и с первым входом второй групп входов элемента И-ИЛИ/И- ИЛИ-НЕ, выход второго элемента НЕ соединен с вторым входом первой и с первым входом второй групп входов элемента И- ИЛИ/И-ИЛИ-НЕ, выход третьего элемента И соединен с пятым входом второй, с четвертым входом третьей, с четвертым входом четвертой, с четвертым входом пятой и с четвертым входом шестой групп входов элемента И-ИЛИ/И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с пятыми входами третьей и четвертой групп входов элемента И-ИЛИ/И-ИЛИ- НЕ, прямой выход элемента И/И-НЕ соединен с пятыми входами пятой и шестой групп входов элемента И-ИЛИ/И- ИЛИ- НЕ, выход третьего элемента И-НЕ является прямым выходом триггера и соединен с третьим входом четвертого элемента И- НЕ, с третьим входом первой группы входов второго элемента И-ИЛИ-НЕ, с первым входом первой и с первым входом пятой групп входов элемента И-ИЛИ/И- ИЛИ-НЕ, выход четвертого элемента И- НЕ является инверсным выходом триггера и соединен с первым входом третьего элемента И-НЕ, с вторым входом второй групп входов первого элемента И-ИЛИ- НЕ, с четвертым входом второй и с первым входом шестой групп входов элемента И- ИЛИ/И-ИЛ.И-НЕ, прямой выход которого является прямым выходом Отказ триггера и.соединен с вторым входом своей седьмой группы входов, инверсный выход элемента И-ИЛИ/И-ИЛИ-НЕ является инверсным выходом Отказ триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| Счетчик импульсов | 1985 |

|

SU1298906A1 |

Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике в качестве базового элемента устройств с повышенными требованиями к достоверности функционирования и времени восстановления работоспособности. Цель изобретения - повышение достоверности функционирования путем введения в структуру триггера каждого разряда средств встроенного контроля и автоматизация процесса восстановления работоспособности. Счетчик содержит четыре основных и резервный разряды, в каждом из которых находится триггер с встроенными средствами контроля. Элементы 2-2И-ИЛИ осуществляют коммутацию сигналов с выходов триггеров в зависимости от их работоспособного состояния на информационные выходы счетчика. Элементы 3-2И-ИЛИ реализуют логику срабатывания триггеров в зависимости от работоспособности предыдущих триггеров. Элементы 2-2И-ИЛИ осуществляют коммутацию синхросигналов на синхровходы последующих триггеров в зависимости от работоспособности триггеров предыдущих разрядов и одноименного с ним разряда. Элементы ИЛИ/ИЛИ-НЕ и И осуществляют последовательное обобщение сигнала работоспособности предыдущих разрядов и формирование сигналов "Частичный отказ" и "Отказ" счетчика в целом. В сллучае отказа одного из триггеров основных разрядов на его прямом выходе "Отказ" формируется сигнал логической "1", который приводит к автоматической реконфигурации работоспособной структуры счетчика. 1 табл., 5 ил.

sl

и

CJ

01 QS 03 О

-i n nVnWnWn nVnV-k

f/ вг вг

03 Qti

,У„У„/„ „г У У У /

iilW

| Справочник | |||

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Под ред | |||

| Б.Н.Файзулаева | |||

| Б.В.Тарабрина | |||

| - М.: Радио и связь, 987, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , | |||

Авторы

Даты

1990-10-07—Публикация

1989-02-06—Подача