резервный разряды, При откате одного1 из or ионных разрядов двоично-десятичного счетчика предоставляется позмож- iiorib nrxTiпновить работоспособность путем подачи на соответствующий уп- ранляющин нход 24,3-24,6 нулевого по- то-ндиапа. При этом происходит автоматическая реконфигурация работоспособной структуры устройства методом

вытеснения из нес неисправного разряда „,Данное техническое решение позволяет повысить эксплуатационную отказоустойчивость базовых компонентов устройств промышленной автоматики и вычислительной техники, а также значительно сократить расход интегральных микросхем на этапе эксплуатации этих счетчиков с, 2 ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

Изобретение относится к импульсной и вычислительной технике, в частности к синхронным счетчикам, и может быть использовано в устройствах промышленной автоматики и вычислительной техники. Целью изобретения является повышение эксплуатационной отказоустойчивости. Двоично-десятичный счетчик реализован по многоразрядной схеме на триггерах 15„3-15,7, элементах И, И/К-НГ, И-НЕ, 2-2И-ИЛИ, ИЛИ, НЕ и содержит четыре основных 3-6 и- 0 ю to & оэ Фис7

Изобретение относится к импульс- нон и вычислительной технике, в частности к синхронным счетчикам, и может быть использовано в устройствах про- мычшенпой автоматики и вычислитель

ном техники

Целью изобретения является повышение эксплуатационной отказоустойчивости устройства

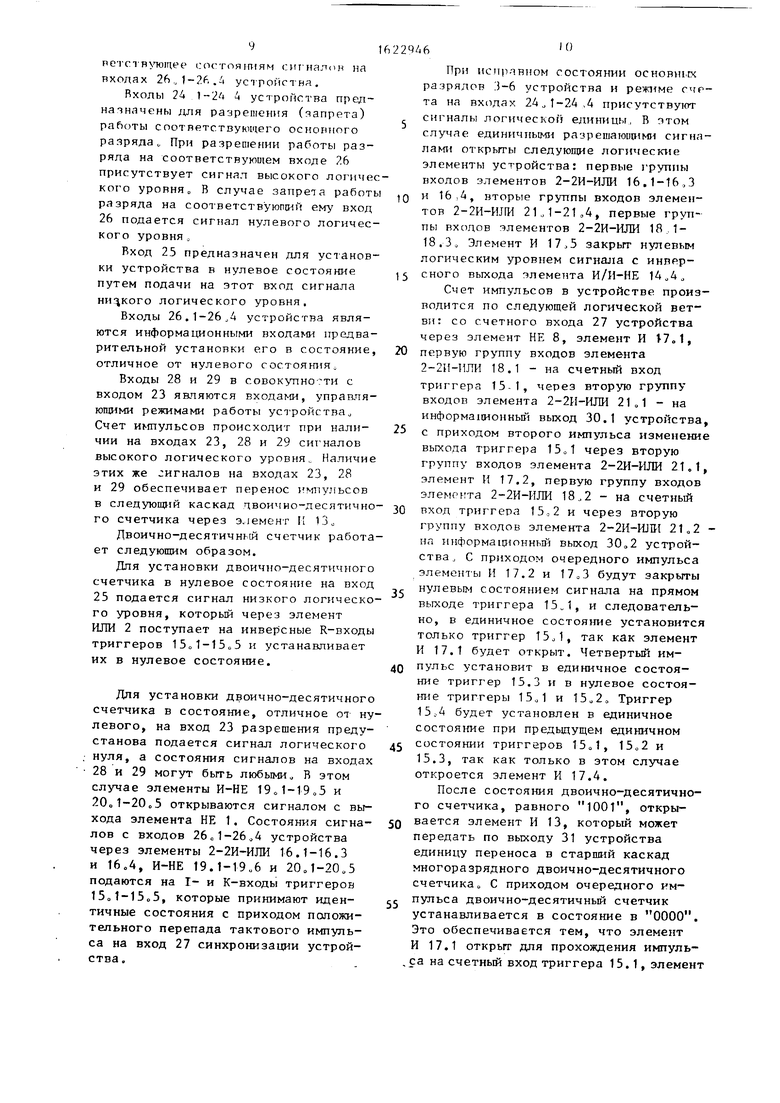

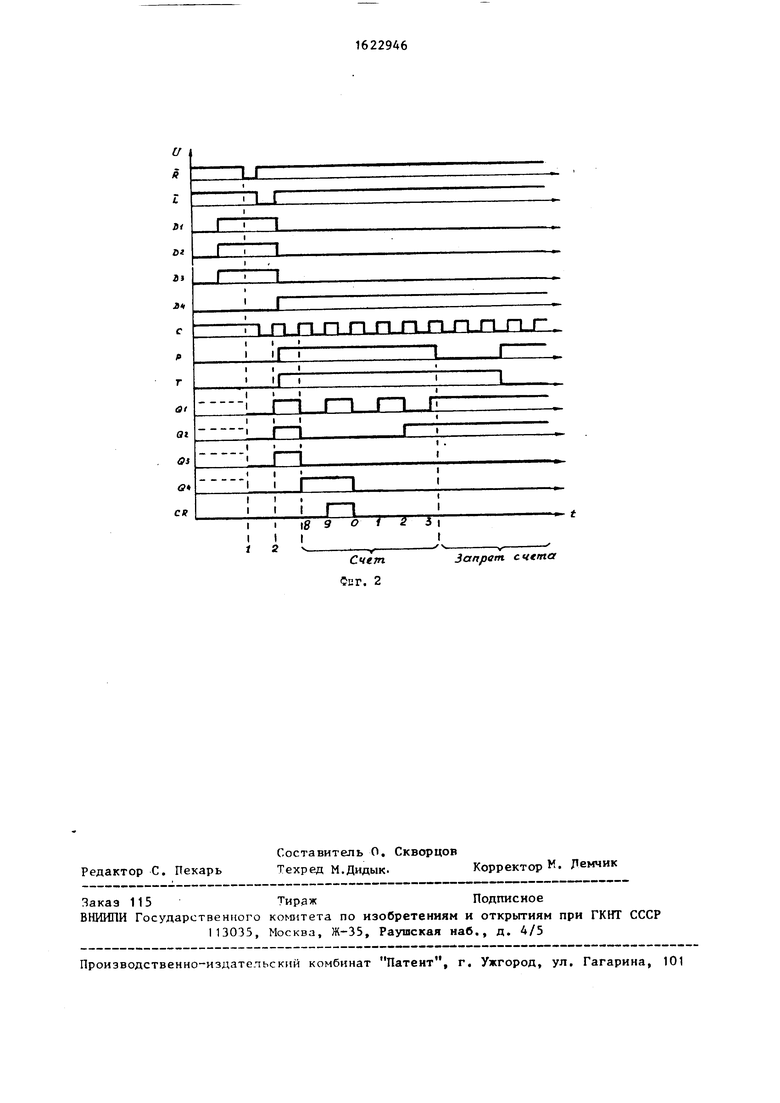

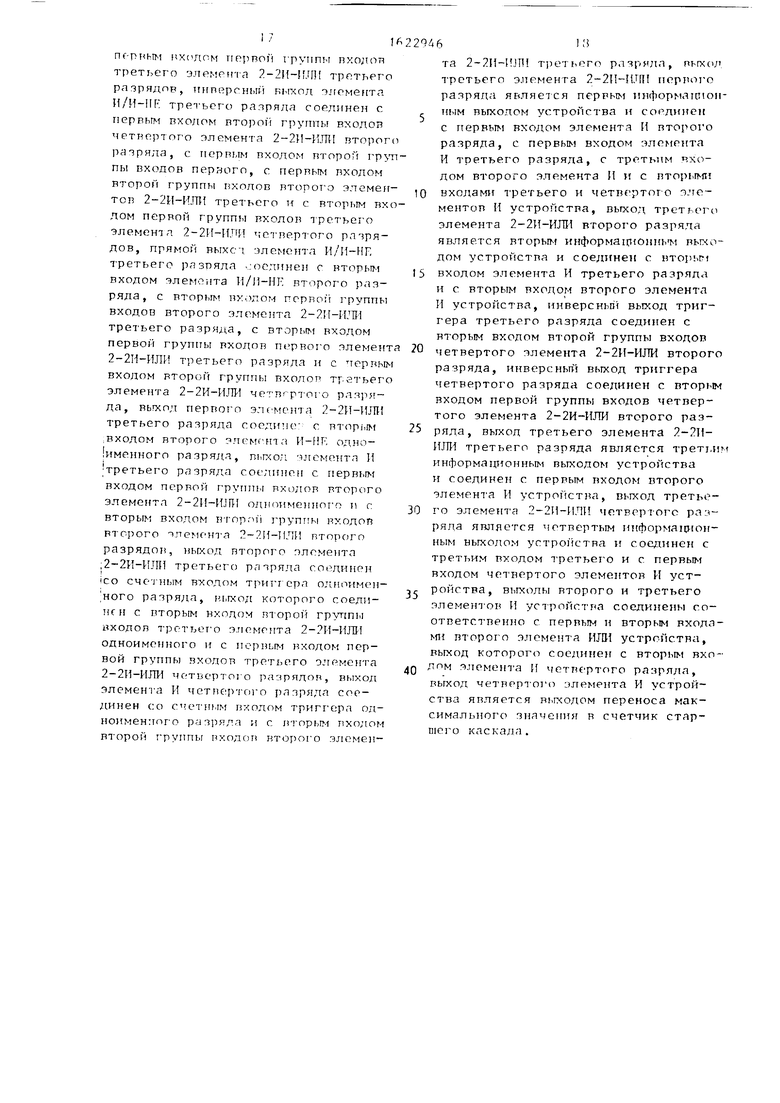

На Ьиг 1 представлена структурная охгма предлагаемого двоично- лосятичного счетчика; на фиг„ 2 - временная диаграмма его работы (I - исходное состояние выходов в IIVTC; 2 - предварительная установка на входах П.2, D.3, П.4-7)„

Двоично-десятичный счетчик содержит (фиг, 1) первый элемент НЕ 1 устройства, первый элемент ИЛИ 2 устройства, основные разряды 3-6, резервный разряд 7, второй элемент НЕ Я, первый 9, второй 10, третий 1 элементы И, второй элемент ИЛИ 12 устройства, четвертый элемент И 13 устройства, элементы И/И-НЕ 14.1-14 и 14.4 разрядов, триггеры 15Ь1 15. разрядов, первые 16.1-1б„3 и 16.4 элементы 2-2И-ИЛИ разрядов, элементы И 17 1-17.5 разрядов, вторые цементы 2-2И-ИЛИ 18. 1-18 „3 разрядов iu-рные элементы И-НЕ 19 разрядов, вторые элементы И-НЕ 20.1-20.5 разрядов, третьи элементы 2-2И-ИЛИ .4 разрядов, четвертый элемен 2-2И-Иг1И 22.1 первого разряда.

Контрольный вход 23 устройства соединен с входом элемента НЕ 1, выход которого соединен с первыми входами элементов И-НЕ 19,1-19.5 и 20,1 0,5. Входы 24,1-24,4 разрешения работы разрядов соединены соответствен но с первыми входами элементов И/И- 1Е 14.4, 14 1-14 3. Вход 2.5 установки в О vi i piific тна соединен с входо

,

20

25

30

35

JQ 15

50

55

элемента ИЛИ 2, выход которого соединен с R-входами триггеров 15.1-15.5 разрядов,, Информационный вход 26 „ 1 предустанова первого разряда 3 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 16.4 и с первым входом первой группы входов элемента 2-2И-ИЛИ 16.1, Информационный вход 26.2 предустанова второго разряда 4 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 16.1 и с первым входом первой группы входов элемента 2-2И-ИЛИ 16.2. Информационный вход 26,3 предустанова третьего разряда 5 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 16.2 и с первым входом первой группы входов элемента 2-2И-ИЛИ Информационный вход предустанова четвертого разряда соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 16.3 и с вторым входом элемента И-НЕ . Син- хровход 27 устройства соединен с входом элемента НЕ 8, выход которого соединен с инверсными входами элементов И 17.1-17.4, Входы 28 и 29 определения режимов работы устройства соединены соответственно с первым входом элемента И 9, с вторым входом элемента И 9 и с третьим входом элемента И 13.

Инверсный выход элемента И/И-НЕ 14.4 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 16„4, с первым входом элемента И и с вторым входом первой группы входов элемента 2-И-ИЛИ 21.1 о Прямой выход элемента И/И-НЕ соедик.ч с первым входом первой группы входов элемента 2-2И-ИЛИ 16,4 и с первым входом второй группы входов элемента 2-2И-ИЛИ 21,1 о

Инверсный выход элемента И/И-НЕ 14„1 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 16.1, с первым входом второй группы входов элемента 2-2И-ИЛИ 18.1 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 21„2. Прямой выход элемента И/И-НЕ 14 о 1 соединен с вторым входом элемента И/И-НЕ 14.4 резервного разряда 7, с вторым входом первой группы входов элемента 2-2И-ИЛИ 16.1, с вторым входом первой группы входов элемента 2-2И-ИЛИ 18„1 и с первым входом второй группы входов элемента 2-2И-ИЛИ 21„2 о

Инверсный выход элемента И/И-НЕ соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 16.2, с первым входом второй группы входов элемента 2-2И-ИЛИ 18„2 и с вторым входом первой группы входов илемента 2-2И-ИЛИ 2103. Прямой выход элемента И/И-НЕ 14.2 соединен с вторым входом

20 18„3. Выход элемента И 17.4 соеди с вторым входом второй группы вхо элемента 2-2И-ШШ 18„3 и со счетн входом триггера 15.4„ Выходы элем тов 2-2И-ИЛИ 18.1-18.3 соединены

30

3S

40

элемента И/И-НЕ 14.1, с вторым входом 25 ответственно со счетными входами первой группы входов элемента 2-2И-ИЛИ 16.2, с вторым входом первой группы входов элемента 2-2И-ИЛИ 1802 и с первым входом второй группы входов элемента 2-2И-ИЛИ 21.3.

Прямой выход элемента И/И-НЕ 14.3 соединен с вторым входом элемента И/И-НЕ 14.2, с вторым входом первой труп- пы входов элемента 2-2И-ИЛИ 16.3, с вторым входом первой группы входов элемента 2-2И-ИЛИ 18,3 и с первым входом второй группы входов элемента 2-2И-ИЛИ 21.4„ Инверсный выход элемента И/И-НЕ 14„3 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 22,, 2, с первым входом второй группы входов элемента 2-2И-ИЛИ 16.3, с первым входом второй группы входов элемента 2-2И-ИЛИ 18.3 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 211.4.

Выход элемента 2-2И-ИЛИ 1604 резервного разряда 7 соединен с вторым входом элемента И-НЕ 20. 5. Выход элемента 2-2И-ИЛИ 16.1 соединен с вторым входом элемента И-НЕ 20„1д Выход элемента 2-2И-ИЛИ 22.1 соединен с вторым входом элемента И 17.2, Выход элемента 2-2И-ИЛИ 16.2 соединен с вторым входом элемента И-НЕ 20.2. Выход элемента 2-2И-ИЛИ 16.3 соединен с вторым входом элемента И-НЕ 20,3„ Выход элемента И 9 сое45

триггеров 1501-15.3.

Выходы элементов И-НЕ 19.1-19. соединены с 1-входами соответству щих им триггеров 15.4-15.5 Выход элементов И-НЕ 20.1-20,5 соединен соответственно с вторыми входами элементов И-НЕ 19.1-19,5 и с К-в дами соответствующих им триггеров 15 J-15.5.

Прямой выход триггера 15.5 сое динен с первым входом первой груп входов элемента 2-2И-ИЛИ 21.1. Пр мой выход триггера 15„1 соединен вторым входом второй группы входо элемента 2-2И-ИЛИ 21„1 и с первым входом первой группы входов элеме та 2-2И-ИЛИ 21.2. Прямой выход тр гера 15.2 соединен с вторым входо второй группы входов элемента 2-2И 21.2 и с первым входом первой гру входов элемента 2-2И-ИЛИ .

Прямой выход триггера 15.3 соед нен с вторым входом второй группы 50 входов элемента 2-2И-ИЛИ 21„3 и с первым входом первой группы входов элемента 2-2И-ИЛИ 21„4„ Инверсный выход триггера 15.3 соединен с вто рым входом второй группы входов эл мента 2-2И-ИЛИ 22.2.

Прямой выход триггера 1-5.4 соед нен с вторым входом второй группы входов элемента 2-2И-ИЛИ 21.4. Инв сный выход триггера 15.4 соединен

55

динен с первым входом элемента

И Т7.1, с третьим входом элемента И 17.2, с третьим входом элемента И 17.3, с четвертым входом элемента И 10 и с первым входом элемента И 11„

Выход элемента И 17„1 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 18„1 и с вторым входом элемента И 17.5, выход которого соединен со счетным входом триггера 1505„ Выход элемента И 17.2 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 18.1 и с первым входом первой группы входов

элемента 2-2И-ИЛИ 18 „2„ Выход элемента И 17„3 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 18 о 2 и с первым входом первой группы входов элемента 2-2И-ИЛИ

18„3. Выход элемента И 17.4 соединен с вторым входом второй группы входов элемента 2-2И-ШШ 18„3 и со счетным входом триггера 15.4„ Выходы элементов 2-2И-ИЛИ 18.1-18.3 соединены соответственно со счетными входами

ответственно со счетными входами

триггеров 1501-15.3.

Выходы элементов И-НЕ 19.1-19.5 соединены с 1-входами соответствующих им триггеров 15.4-15.5 Выходы элементов И-НЕ 20.1-20,5 соединены соответственно с вторыми входами элементов И-НЕ 19.1-19,5 и с К-вхо- дами соответствующих им триггеров 15 J-15.5.

Прямой выход триггера 15.5 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 21.1. Прямой выход триггера 15„1 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 21„1 и с первым входом первой группы входов элемента 2-2И-ИЛИ 21.2. Прямой выход триггера 15.2 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 21.2 и с первым входом первой группы входов элемента 2-2И-ИЛИ .

Прямой выход триггера 15.3 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 21„3 и с первым входом первой группы входов элемента 2-2И-ИЛИ 21„4„ Инверсный выход триггера 15.3 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 22.2.

Прямой выход триггера 1-5.4 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 21.4. Инверсный выход триггера 15.4 соединен с

вторым входом первой группы входов элемента 2-2И-ИЛИ 22,1,

Выход элемента 2-2И-ИЛИ 21„1 яв- ляотгя информационным выходом 30.1

первого разряда 3 устройства и соединен с первыми входами элементов И 17.2 и 17L3, с третьим входом элемента И 10, с вторым входом элемента И 11 и с вторым входом элемента И 13.

Выход элемента 2-2И-ИЛИ 21 С2 является информационным выходом 3002 второго разряда 4 устройства и соединен с вторым входом элемента И 17.3 и с вторым входом элемента И 10„

Выход элемента 2-2И-ИЛИ 21.3 является информационным выходом 30„3 третьего разряда 5 устройства и соединен с первым входом элемента И 10.

Выход элемента 2-2И-ИЛИ 21„4 явля- ется информационным выходом 30„4 четвертого разряда 6 устройства и соединен с третьим входом элемента И 11 и с первым входом элемента И 13.

Выходы элементов И 10 и 11 соеди- некы соответственно с первым и вторым входами элемента ИЛИ 12, выход которого соединен с вторым входом элемента И 17.60 Выход элемента И 13 является выходом переноса значения в . старший разряд счетчика устройства„

Рассмотрим функциональное назначение элементов логической структуры предлагаемого двоично-десятичного счетчика,

Элемент НЕ 1 осуществляет инверсию сигнала на контрольном входе 23 разрешения предустанова устройства и открывает или закрывает элементы И-НЕ 19Л-19.5 и 20„1-20..5„

Элемент ИЛИ 2 принимает сигнал на входе 25 устройства и согласует его со стандартным значением логического О или логической 1 внутри интегральной микросхемы

Разряды 3-6 являются основными разрядами двоично-десятичного счетчика, реализующими его основное функциональное назначение в устройствах промышленной автоматики и вычислительной техники.

Разряд 7 является резервным разрядом двоично-десятичного счетчика и предназначен для восстановления его работоспособности при отказе одного из основных разрядов 3-6,

Элемент НЕ 8 осуществляет инвер- тирование сигнала на синхровходе 27 устройства и преобразует его реаль

К)

15

20

25 30

эс

д()

д5

50

5

ное значение в номинальные значения логической 1 или логического О внутри интегральной микросхемы.

Элементы И 9-11, 13 и ИЛИ 12 реализуют схему управления режимами работы двоично-десятичного счетчика.

Элементы И/И-НЕ 14.1-1403 и 14.4 осуществляют выработку сигналов настроечной функции, управляющей работоспособной структурой двоично-десятичного счетчика, в зависимости от исправного (неисправного) состояния его разрядов 3-6.

Триггеры 15,1-15,, 5 предназначены для хранения числа накопленных импульсов, поступивших на синхровход 27 устройства при разрешении их счета

Элементы 2-2И-ИЛИ 16„1-16.3 и 16„4 осуществляют коммутацию сигналов с информационных входов 26.1- 26 „4 предустанова устройства на I- и К-входы триггеров 15„1-15.5, в зависимости от исправного (неисправного) состояния соответствующих основных разрядов 3-6 о

Элементы И 17„1-17.5 совместно с элементами 2-2И-ИЛИ 18.1-18.3 осуществляют коммутацию синхросигналов, поступающих на синхровход 27 устройства, и изменений на прямых выходах триггеров 15ь1-15„5 на счетные входы триггеров последующего исправного разряда о

Элементы И-НЕ 19.1-19.5 и 20.1- 20.5 осуществляют подачу разнополяр- ных сигналов на I- и К-входы триггеров 15.1-15.50

Элементы 2-2И-ИЛИ 21.1-21.4 осуществляют коммутацию сигналов с триггеров 15с1-15.5 на выходы 30.1-30.4 устройства в зависимости от исправного (неисправного) состояния соответствующего разряда

Элемент 2-2И-ИЛИ 22.1 осуществляет установку устройства в О после значения 1001 и коммутирует этот сигнал установки в первый 3 или во второй 4 разряды в зависимости от их работоспособного состояния.

Вход 23 разрешения предустанова устройства предназначен для управления режимом установки его в предварительное состояние, отличное от нуля. При наличии на входе 23 сигнала низкого логического уровня устройство устанавливается в состояние, соотретствутотее состояниям сигналом на входах 26 0 1-26.4 устгойотва.

Входы 24 1-24 ч устройства предназначены для разрешения (запрета) работы соответствующего основного разряда о При разрешении работы разряда на соответствующем входе 26 присутствует сигнал высокого логического уровня„ В случае запрета работы разряда на соответствующий ему вход 26 подается сигнал нулевого логического уровня0

Вход 25 предназначен для установки устройства в нулевое состояние путем подачи на этот вход сигнала низкого логического уровня.

Входы 26.1-26,4 устройства являются информационными входами предварительной установки его в состояние, отличное от нулевого состояния,

Входы 28 и 29 в совокупно -ти с входом 23 являются входами, управляющими режимами работы устройства, Счет импульсов происходит при наличии на входах 23, 28 и 29 сиг налов высокого логического уровня. Наличие этих же сигналов на входах 23, 28 и 29 обеспечивает перенос импульсов в следующий каскад цвоично-десятично го счетчика через элемент I 13 „

Двоично-десятичный счетчик работает следующим образом.

Для установки двоично-десятичного счетчика в нулевое состояние на вход 25 подается сигнал низкого логического уровня, который через элемент ИЛИ 2 поступает на инверсные R-входы триггеров 15о1-15о5 и устанавливает их в нулевое состояние.

Для установки двоично-десятичного счетчика в состояние, отличное от нулевого, на вход 23 разрешения преду- станова подается сигнал логического нуля, а состояния сигналов на входах 28 и 29 могут быть любыми„ В этом случае элементы И-НЕ 19„1-19„5 и 20о1-2005 открываются сигналом с выхода элемента НЕ 1. Состояния сигналов с входов 26„1-2604 устройства через элементы 2-2И-ИЛИ 16.1-16.3 и 16.4, И-НЕ 19.1-19„6 и 20о1-20„5 подаются на I- и К-входы триггеров 15«, 1-15„5, которые принимают идентичные состояния с приходом положительного перепада тактового импульса на вход 27 синхронизации устройства.

10

20

25

224/4610

При исправном состоянии основных разрядов 3-6 устройства и режиме гчг- та на входах 2401-24,4 присутствуют сигналы логической единицы, В этом случае единичными разрешающими сигналами открыты следующие логические элементы устройства: первые группы входов элементов 2-2И-ИЛИ 16.1-16,3 и 16.4, вторые группы входов элементов 2-2И-ИЛИ 21,1-21„4, первые группы входов -элементов 2-2И-ИЛИ 18 1- 18.3 о Элемент И 17,5 закрыт нулевым логическим уровнем сигнала с инлрр- 15 сного выхода элемента И/И-НЕ 14040

Счет импульсов в устройстве производится по следующей логической ветви: со счетного входа 27 устройства через элемент НЕ 8, элемент И 17„1, первую группу входов элемента 2-2И-ШТИ 18.1 - на счетный вход триггера 15-1, через вторую группу входов элемента 2-2И-ИЛИ 21„1 - на информационный выход 30.1 устройства, с приходом второго импульса изменение выхода триггера 15„1 через вторую группу входов элемента 2-2И-ИЛИ 21.1, элемент И 17.2, первую группу входов элемента 2-2И-ИЛИ 18,2 - на счетный вход триггера и через вторую группу входов элемента 2-2И-ИЛИ 21„2 - на информационный выход 30„2 устройства, С приходом очередного импульса элементы И 17.2 и 1703 будут закрыты нулевым состоянием сигнала на прямом выходе триггера 15,1, и следовательно, в единичное состояние установится только триггер 15,1, так как элемент И 17.1 будет открыт. Четвертый импульс установит в единичное состояние триггер 15.3 и в нулевое состояние триггеры 1501 и 15020 Триггер 1504 будет установлен в единичное состояние при предыдущем единичном состоянии триггеров 1501, 15„2 и 15.3, так как только в этом случае откроется элемент И 17.4.

После состояния двоично-десятичного счетчика, равного 1001, открывается элемент И 13, который может передать по выходу 31 устройства единицу переноса в старший каскад многоразрядного двоично-десятичного счетчика С приходом очередного импульса двоично-десятичный счетчик устанавливается в состояние в 0000. Это обеспечивается тем, что элемент И 17.1 открыт для прохождения импуль- ,са на счетный вход триггера 15.1, элемент

30

35

40

45

50

55

И закрыт сигналом с вькода эЛе- мента 2-2И-ИЛИ 22,1, элемент И 17.3- закрыт нулевым сигналом с выхода триггера 15.4 через -элемент 2-2И-ИЛИ 21„2 и элемент И 17,4 открыт для прохождения синхроимпульса на счетный вход триггера 15,2.

Состояние входов и выходов устройства при счете от 0 до 9 показано на временной диаграмме работы устройства (фиг0 2)0

При неисправном состоянии одного из основных разрядов 3-6 на соответствующий управляющий вход 24„1-2404 устройства подается сигнал логического нуля0

Рассмотрим принцип сохранения работоспособности устройства на примерах, когда произошел отказ первого 3 и третьего 5 разрядов о

При отказе триггера 15.1 первого разряда на управляющий вход 24„1 подается нулевой потенциал и данный разряд исключается из режима функционирования предлагаемого двоично-десятичного счетчика с Это производится следующим образом.

Нулевой потенциал на входе 24.1 устройства приводит к смене сигналов на прямом и инверсном выходах элемента И/И-НЕ 14.4, что, в свою очередь, приводит к открытию второй и закрытию первой групп входов элемента 2-2И-ИЛИ 16.4, к открытию первой и закрытию второй групп входов элемента 2-2И-ИЛИ 21,1, а также к открытию элемента И 17 „5„ Таким образом, при установке устройства в состояние, отличное от нулевого, сигнал с входа 26,1 будет поступать через вторую группу входов элемента 2-2И-ИЛИ 16.4 на вход элемента И-НЕ 20.5, а значение состояния сигнала на выходе триггера 15,5 через первую группу входов элемента 2-2И-ИЛИ 21,1 - на информационный выход 30 „1 устройства. Выход триггера 15.1 в этом случае будет отключен от выхода 30„1 устройства закрытой второй группой входов элемента 2-2И-ИЛИ 21,1,

Подсчет импульсов в этом случае будет производиться по следующей логической ветви предлагаемого двоично-десятичного рчетчика: с синхро- входа 27 устройства через элемент НЕ 8, элементы И 1701 и 17.5 - на счетный вход триггера 15,5, значение состояний сигналов (и их изменения)

5

0

5

0

5

0

5

на выходе триггера 15.5 через первую группу входов элемента 2-2И-ИЛИ

и через элемент И 17.3, первую группу входов элемента 2-2И-ИЛИ 18.3 - на счетный вход триггера 15.3„ Состояние сигнала (и его изменения) на выходе триггера 15.3 через вторую группу входов элемента 2-2И-ИЛИ

При отказе триггера 15.3 на управляющий вход 24,3 устройства подается нулевой потенциал, который приводит к изменению состояний сигналов на прямых и инверсных выходах элементов И/И-НЕ 14,2, 14.1 и 14„4. Единичными потенциалами с их инверсных выходов открываются следующие логические элементы устройства: вторая группа входов элемента 2-2И-ИЛИ 16.4 (разрешается прохождение сигнала с входа 26,1 устройства на I- и К-ыходы триггера 15„5), элемент И 1705 (разрешается прохождение синхроимпульсов на счетный вход триггера 15„5), первая группа входов1 элемента 2-2И-ИЛИ 2101 (разрешается прохождение сигнала с выхода триггера 15,5 на информационный выход 3001 устройства), вторая группа входов элемента 2-2И-ИЛИ 1601 (разрешается прохождение сигнала с-входа

на вход С триггера 1 г 1), первая группа входов элемента 2-2И-ИЛИ 21 (разрешается прохождение сигнала с выхода триггера 15 1 па ишЪормацион- ный БЬГХОД 30 2 устройства), вторая группа входов -элемента 2-2И-ИЛИ 16.2 (разрешается прохождение сигнала с входа 26„3 устройства на I- и К-вхо- ды триггера 15.2), вторая группа входов элемента 2-2И-ИЛИ 18,2 (разрешается прохождение синхроимпульса с выхода элемента И 17,3 на счетный вход триггера 15С2), первая группа входов элемента 2-2И-ИЛИ 21„3 (разрешается прохождение сигнала с выхода триггера 15.2 на информационный выход 30.3 устройства) Состояние логических элементов четвертого разряда 6 остается прежним0 Таким образом, при подаче нулевого потенциал на вход 24„3 логическая структура двоично-десятичного счетчика перестраивается на работоспособную структуру вытесняя отказатоий триггер 15„3о

Замена отказавших триггеров 15.1 и 1504 второго и четвертого Разрядов производится аналогично рассмотренным примерам.

Таким образом, в двоично-десятичном счетчике осуществляется автоматическая реконфигурация его логической структуры при отказе одного из основных разрядов, что создает возможность обеспечения работоспособности этого устройства без замены, и, следовательно, повышается его эксплуатационная отказоустойчивость.

Формула изобретения

Двоично-десятичный счетчик, содержащий два элемента НЕ, два элемента ИЛИ, четыре элемента И и разряды, каждый из которых содержит триггер, два элемента И-НЕ, элемент И, вход разрешения предустанова устройства соединен с входом первого элемента НЕ устройства, выход которого соединен с первыми входами первого и второго элементов И-НЕ каждого разряда, вход установки в О .устройства соединен с входом первого элемента ИЛИ устройства, выход которого соединен с R-входом триггера каждого разряда, синхровход устройства соединен с входом второго элемента НЕ устройства, выход которого

5

0

5

с

0

5

0

5

с оел1Ч1 и инверстми входами Mt in он И K,I +jioi о разряда, riроиства соединен с первым входом первого элемента И устройства, второй вход которого соединен г Т-входом устройства, который дополнительно соединен с третьим входом четвертого элемента И устройства, выход первого элемента И-HF, разряда соединен с I-входом трнгг ера одноименного разряда, выход второго элемента И-НЕ каждого разряда соединен с вторым входом первого элемента И-НЕ и с К- входом триггера одноименного разряда, выход первого элемента И устройства соединен с первым входом третьего и с четвертым входом второго элементов И устройства, с прямым входом элемента И первого разряда, с третьим входом элемента И второго разряда, с третьим входом элемента И третьего разряда, отличающийся тем, что, с целью повышения эксплуатационной отказоустойчивости, в него введены дополнительный разряд, содержащий триггер, элемент И/И-НЕ, элемент 2-2И-ШШ, элемент И и два элемента И-НЕ, каждый, кроме резервного, разряд дополнительно содержит третий элемент 2-2И-ИЛИ, разряды, кроме резервного и четвертого, содержат элемент И/И- НЕ, первый и второй элементы 2-2И-ИЛИ, второй разряд дополнительно содержит четвертый элемент 2-2И-ИЛИ, причем вход разрешения работы первого разряда соединен с первым входом элемента И/И-НЕ резервного разряда, вход разрешения работы второго разряда соединен с первым входом элемента И/Н-НЕ первого разряда, вход разрешения работы третьего разряда соединен с первым входом элемента И/И-НЕ второго разряда, вход разрешения работы четвертого разряда соединен с первым входом элемента И/И-НЕ третьего разряда, информационный вход предустанова первого разряда соединен с первым входом первой группы входов первого элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов элемента 2-2И-ИЛИ резервного разрядов, информационный вход предустанова второго разряда соединен с первым входом первой группы входов первого элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов первого эле

мента 2-2И-ИЛИ первого разрядов, вхо предустанова третьего разряда соединен с первым входом первой группы входов первого элемента 7-2И-ШП1 одноименного и с вторым входом второй группы входов второго разрядов, вход предустанова четвертого разряда соединен с вторым входом второго элемента И-НЕ одноименного и с вторым входом второй группы входов первого элемента 2-2И-ИЛИ третьего разрядов, выход первого элемента НЕ устройства дополнительно соединен с первым входами первого и второго элементов И-НЕ резервного разряда, выход первого элемента ИЛИ устройства дополнительно соединен с R-входом триггера резервного разряда, инверсный выход элемента И/И-НЕ резервного разряда соединен с первым входом второй группы входов элемента 2-2И-И одноименного, с первым входом элемента И одноименного и с вторым входом первой группы входов третьего элемен та 2-2И-ИЛИ первого разрядов, прямой выход элемента И/И-НЕ резервного разряда соединен с первым входом первой группы входов элемента 2-2И-ИЛИ одноименно и с первым входом второй группы входов третьего элемента 2-2И-ИЛИ первого разрядов, выход элемента 2-2И-ИЛИ резервного разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход которого соединен с вторым входом первого элемента И-НЕ и с К-входом триггера одноименного разряда, выход первого элемента И-НЕ резервного разряда соединен с 1-вхо- дом триггера одноименного разряда, синхровход которого соединен с выходом элемента И одноименного разряда, прямой выход триггера резервного разряда соединен с первым входом первой группы входов третьего элемента 2-2И-ИЛИ первого разряда, инверсный выход элемента И/И-НЕ первого разряда соединен с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ одноименного и с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ второго разрядов, прямой выход элемента И/И-НЕ первого разряда соединен с вторым входом элемента И/И-НЕ резервного, с вторым входом первой группы входов первого, с вторым вхо

10

0

5

5

дом первой группы входов второго элементов 2-2И-ИЛИ одноименного и с первым входом пторой группы входов третьего элемента И-2И-ИЛИ второго | разрядов, выход первого элемента 2-2И-ИЛИ первого разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход элемента И первого разряда соединен с вторым входом элемента И резервного разряда и с первым входом первой группы входов второго элемента 2-2И-ИЛИ первого разряда, выход которого соединен со счетным входом триггера одноименного разряда, выход триггера первого разряда соединен с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов третьего элемента 2-2И- ИЛИ второго разрядов, вход разрешения работы четвертого разряда дополнительно соединен с первым входом первой группы входов четвертого элемента 2-2И-ИЛИ второго разряда, выход которого соединен с вторым входом элемента И одноименного разряда, выход которого соединен с первым входом первой группы входов второго элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ первого разрядов, инверсный выход элемента И/И-НЕ второго разряда соединен с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ одноименного и с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разрядов, прямой выход элемента И/И-НЕ второго разряда соединен с вторым входом элемента И/И-НЕ первого разряда, с вторым входом первой группы входов первого, с вторым входом первой группы входов второго элементов 2-2И-ИЛИ второго разрядов и с первым входом второй группы входов третьего элемента 2-2И-ИЛИ третьего разряда, выход первого элемента 2-2И-ИЛИ второго разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход второго элемента 2-2И-ИЛИ второго разряда соединен со счетным входом триггера одноименного разряда, выход которого соединен с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного и с

I /J

первым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разрядов, инверсный выход -элемента И/И-ПК третьего разряда соединен с первым входом второй группы входов четвертого элемента 2-2И-ИЛИ второг разряда, с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ третьего и с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ четвертого раэря- дов, прямой выхсл -элемента И/И-НГ, третьего разряда , оединен с вторым входом элемента И/И-НЕ второго разряда, с вторым входом первой группы входов второго элемента 2-2И-ИЛИ третьего разряда, с вторым входом первой группы входов первого .элемент 2-2И-ИЛИ третьего разряда и с первым входом второй группы ВХОДОР третьего элемента 2-2И-ИЛИ четп-ртого рязря- да, выход первого элемента 2-2И-ШШ третьего разряда соодипо г втором входом второго элемента И-Н17, одно- , именного разряда, выход элемента И Третьего разряда соединен с первым входом первой группы входов второго элемента 2-2Н-ИШ1 одноименного п г вторым входом второй группы входов второго элемента 2-2И-ИЛИ второго разрядов, выход второго элемента .2-2И-ИЛИ третьего разряда соединен ico счетным входом триггера одноимен- |ного разряда, выход которого соединен с вторым входом торой группы входов третьего элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ четьерто о разрядов, выход элемента И четвертого разряда соединен со счетным входом триггера одноименного разряда и с вторым входом второй группы входов второго элемен10

15

20

2Q46К

та 2-2И-НЛИ третьего разряда, пьгхол третьего элемента 2-2И-1ШИ первого разряда является первым информационным выходом устройства и соединен с первым входом элемента И второго разряда, с первым входом элемента И третьего разряда, с третьим входом второго элемента И и с вторыми входами третьего и четвертого элементов II устройства, выход третьего элемента 2-2И-ИЛИ второго разряда является вторым информационным выходом устройства и соединен с вторым входом элемента И третьего разряда и с вторым входом второго элемента И устройства, инверсный выход триггера третьего разряда соединен с вторым входом второй группы входов четвертого элемента 2-2И-ИЛИ второго разряда, инверсный выход триггера четвертого разряда соединен с вторым входом первой группы входов четвертого элемента 2-2И-ИЛИ второго раэ- 25 ряда, выход третьего элемента 2-2И- ИЛИ третьего разряда является третьим информационным выходом устройства и соединен с первым входом второго элемента И устройства, выход третьего элемента 2-2И-ИЛН четвертого разряда является четвертым информационным выходом устройства и соединен с третьим входом третьего и с первым входом четвертого элементов И устройства, выходы второго и третьего элементов И устройства соединены соответственно с первым и вторым входами второго элемента ИЛИ устройства, выход которого соединен с вторым входом элемента И четвертого разряда, выход четвертого элемента И устройства является выходом переноса максимального значения в счетчик старшего каскада.

30

5

0

LJ

1

1Jn nJn U -rLJn n n n r

i i

JiT

i i

rn

I

I I

о

JL

СИ

i

i s

8 9 о Г I

Счет

Ссг. 2

3T

Запрет с чета

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Применение интегральных микросхем в электронной вычислительной технике Справочник./Под ред„ Б,Н, Файзулаеяа, Б.В | |||

| Тарабрина, - М.: Радио и связь, 1987, с, 38, рис 3.29. | |||

Авторы

Даты

1991-01-23—Публикация

1989-02-03—Подача