Изобретение относится к импульсной и вы1ислительной технике, в частности к счет- чикэм, и может быть применено в устройствах промышленной автоматики и вычислительной техники с повышенной отказоустойчивостью.

j Целью изобретения является повышение оперативной достоверности функционирования и сокращение времени вое ры

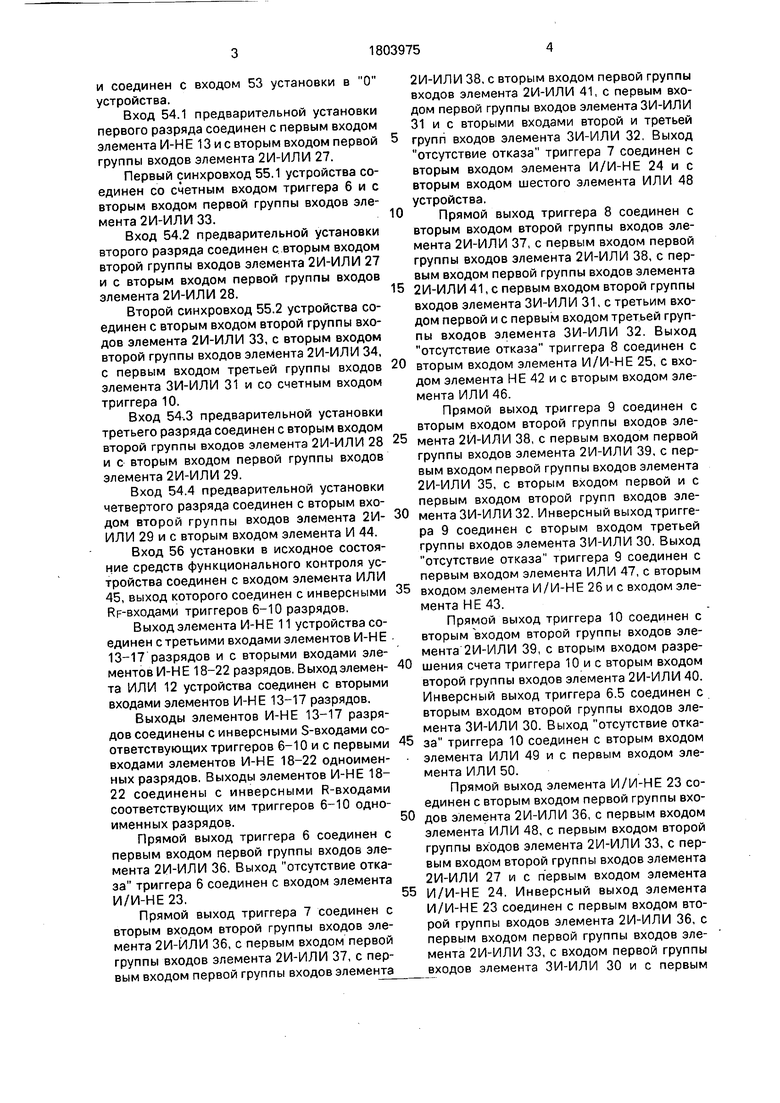

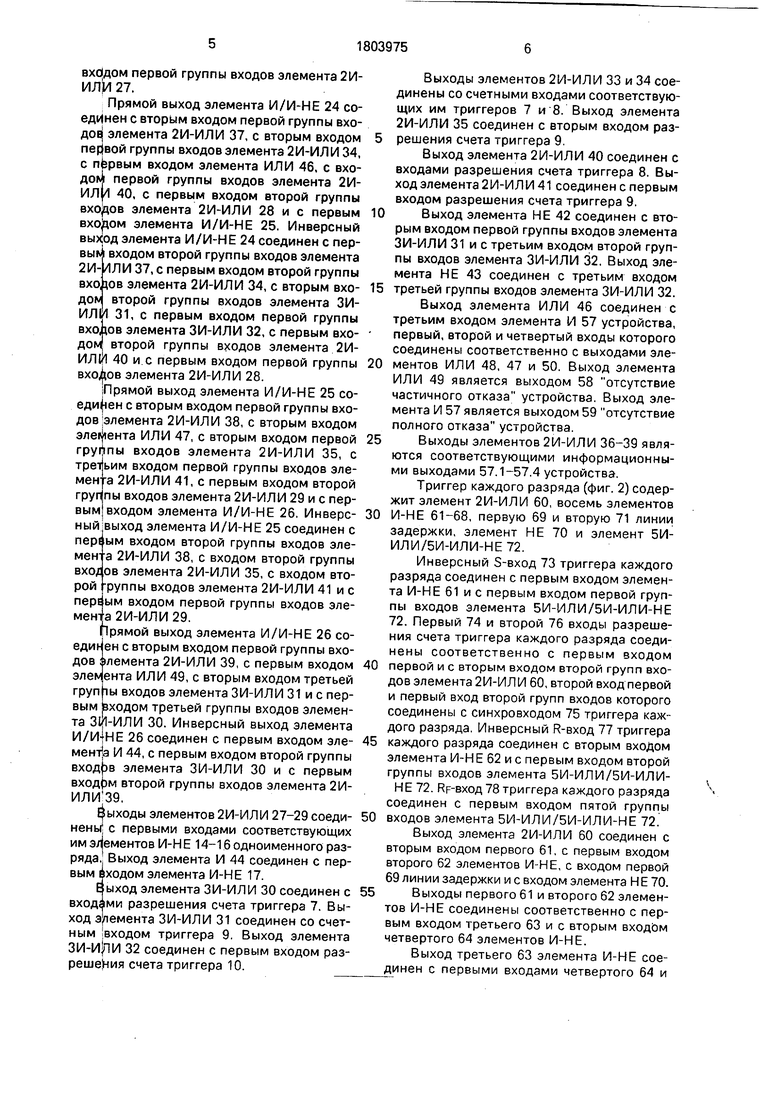

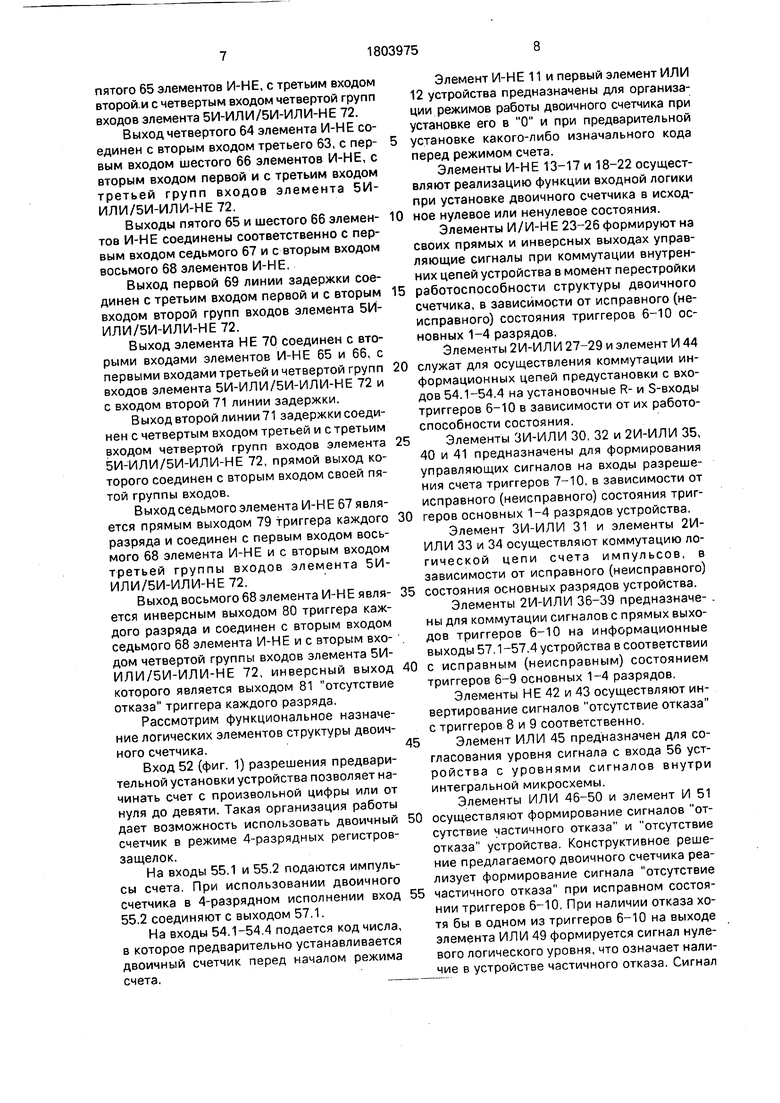

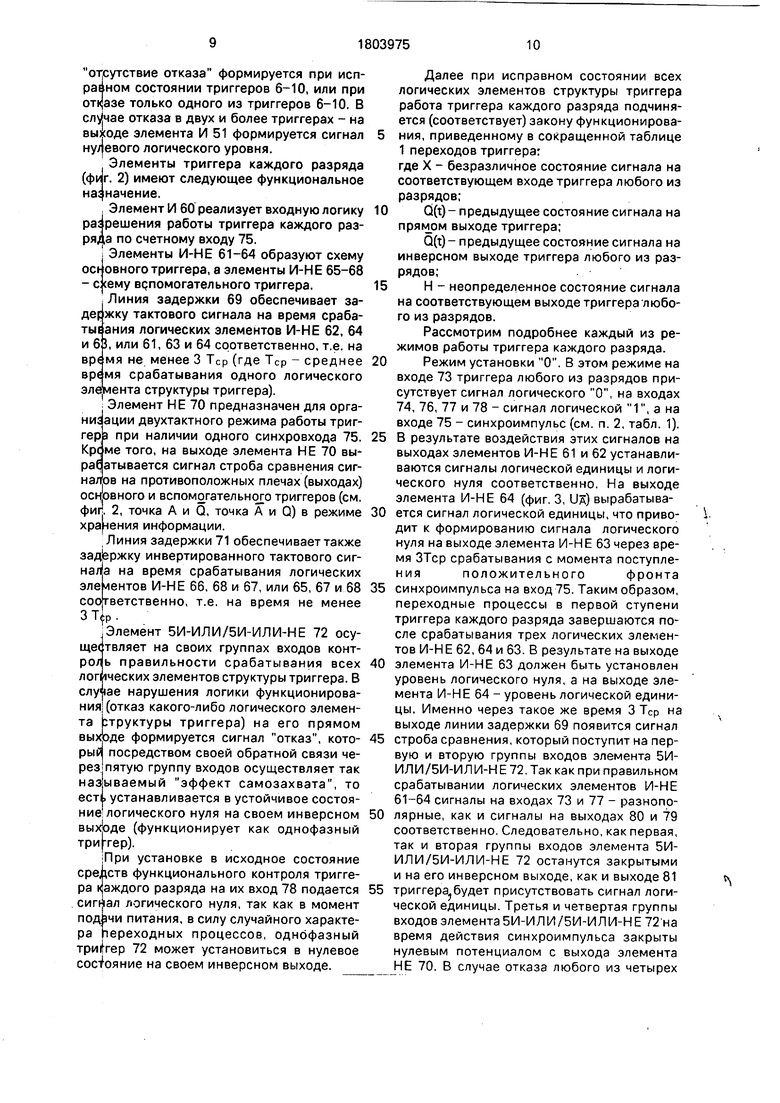

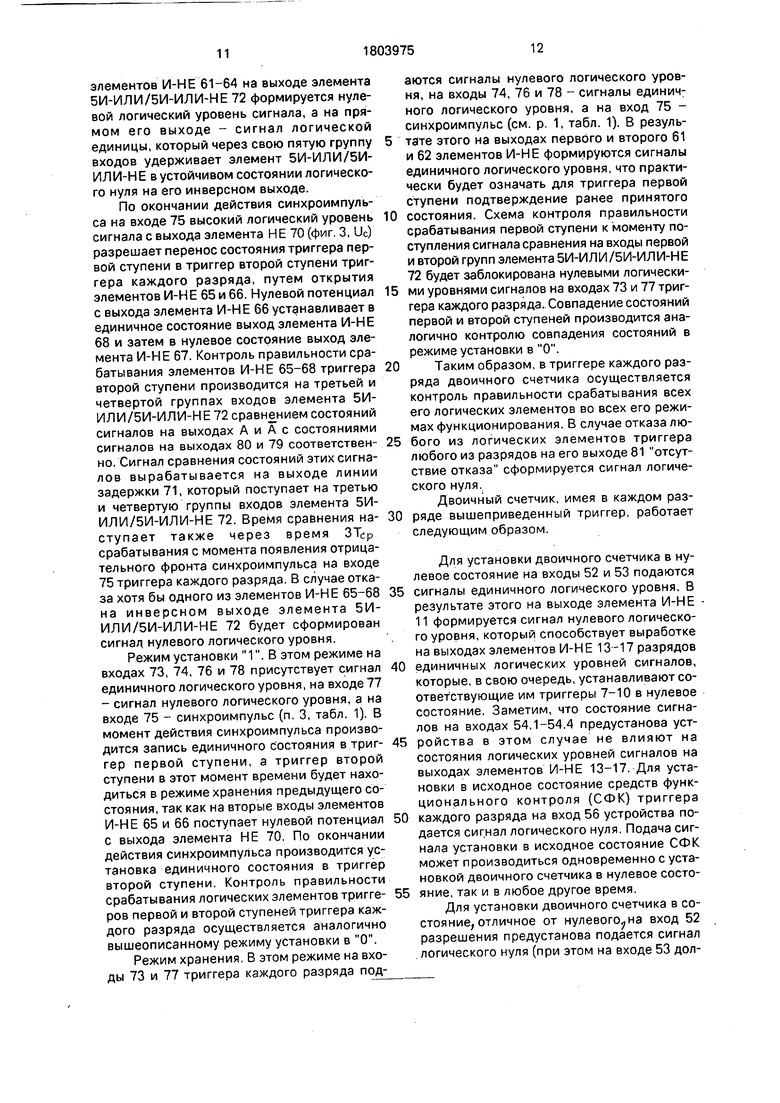

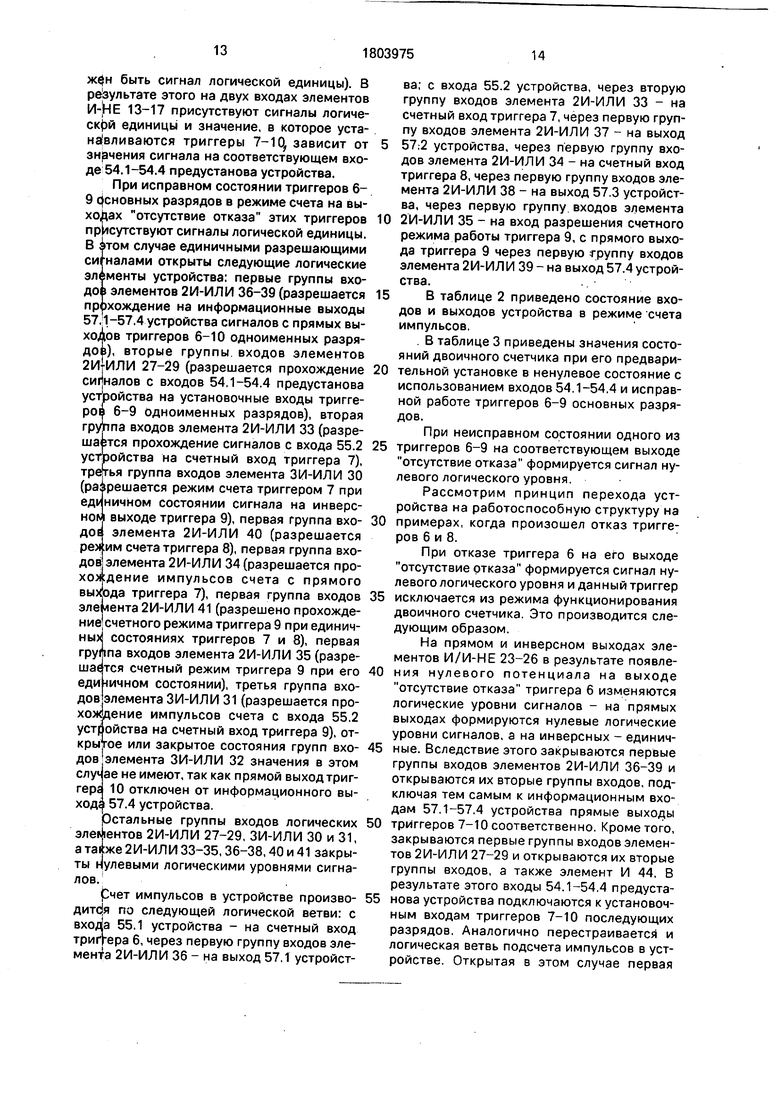

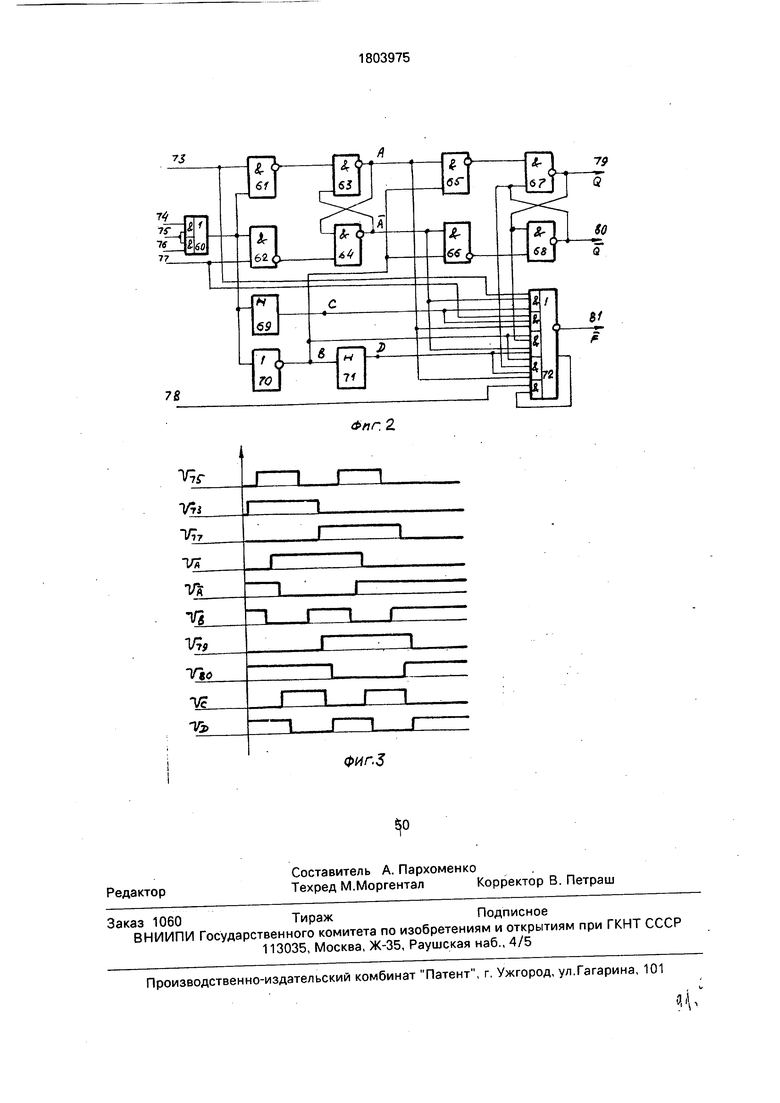

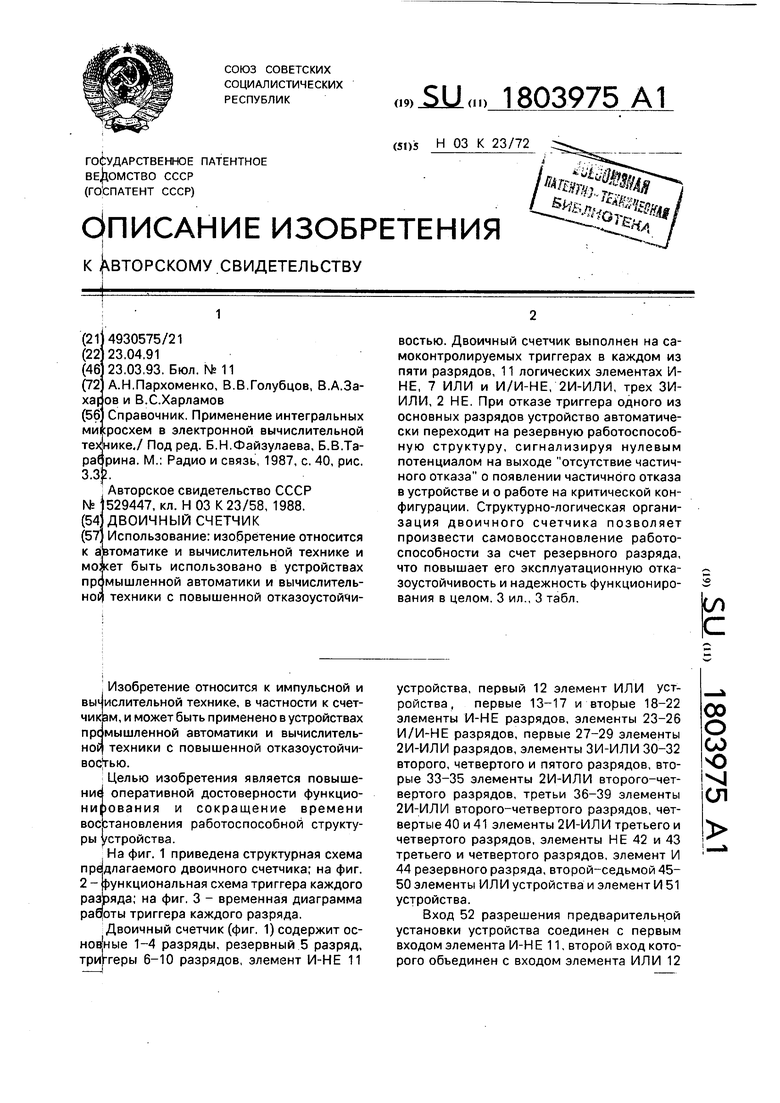

На фиг. 1 приведена структурная схема предлагаемого двоичного счетчика; на фиг. 2 - функциональная схема триггера каждого разряда; на фиг, 3 - временная диаграмма работы триггера каждого разряда.

Двоичный счетчик (фиг, 1) содержит основные 1-4 разряды, резервный 5 разряд, триггеры 6-10 разрядов, элемент И-НЕ 11

становления работоспособной структу- (Гстройства.

устройства, первый 12 элемент ИЛИ устройства, первые 13-17 и вторые 18-22 элементы И-НЕ разрядов, элементы 23-26 И/И-НЕ разрядов, первые 27-29 элементы 2И-ИЛИ разрядов, элементы ЗИ-ИЛИ 30-32 второго, четвертого и пятого разрядов, вторые 33-35 элементы 2И-ИЛИ второго-чет- вертого разрядов, третьи 36-39 элементы 2И-ИЛИ второго-четвертого разрядов, четвертые 40 и 41 элементы 2И-ИЛИ третьего и четвертого разрядов, элементы НЕ 42 и 43 третьего и четвертого разрядов, элемент И 44 резервного разряда, второй-седьмой 45- 50 элементы ИЛИ устройства и элемент И 51 устройства.

Вход 52 разрешения предварительной установки устройства соединен с первым входом элемента И-НЕ 11, второй вход которого объединен с входом элемента ИЛИ 12

со

о

со о

а

и соединен с входом 53 установки в О устройства.

Вход 54.1 предварительной установки первого разряда соединен с первым входом элемента И-Н Е 13 и с вторым входом первой группы входов элемента 2И-ИЛИ 27.

Первый синхровход 55.1 устройства соединен со счетным входом триггера бис вторым входом первой группы входов элемента 2И-ИЛИ 33.

Вход 54.2 предварительной установки второго разряда соединен с вторым входом второй группы входов элемента 2И-ИЛИ 27 и с вторым входом первой группы входов элемента 2И-ИЛИ 28.

Второй синхровход 55.2 устройства соединен с вторым входом второй группы входов элемента 2И-ИЛИ 33, с вторым входом второй группы входов элемента 2И-ИЛИ 34, с первым входом третьей группы входов элемента ЗИ-ИЛИ 31 и со счетным входом триггера 10.

Вход 54.3 предварительной установки третьего разряда соединен с вторым входом второй группы входов элемента 2И-ИЛИ 28 и с вторым входом первой группы входов элемента 2И-ИЛИ 29.

Вход 54.4 предварительной установки четвертого разряда соединен с вторым входом второй группы входов элемента 2И- ИЛИ 29 и с вторым входом элемента И 44.

Вход 56 установки в исходное состояние средств функционального контроля устройства соединен с входом элемента ИЛИ 45, выход которого соединен с инверсными Rp-входами триггеров 6-10 разрядов.

Выход элемента И-НЕ 11 устройства соединен с третьими входами элементов И-НЕ 13-17 разрядов и с вторыми входами элементов И-НЕ 18-22 разрядов. Выходэлемен- та ИЛИ 12 устройства соединен с вторыми входами элементов И-НЕ 13-17 разрядов.

Выходы элементов И-НЕ 13-17 разрядов соединены с инверсными S-входами соответствующих триггеров 6-10 и с первыми входами элементов И-НЕ 18-22 одноименных разрядов. Выходы элементов И-НЕ 18- 22 соединены с инверсными R-входами соответствующих им триггеров 6-10 одно

именных разрядов.

Прямой выход триггера 6 соединен с первым входом первой группы входов элемента 2И-ИЛИ 36. Выход отсутствие отказа триггера 6 соединен с входом элемента И/И-НЕ23.

Прямой выход триггера 7 соединен с вторым входом второй группы входов элемента 2И-ЙЛИ 36, с первым входом первой группы входов элемента 2И-ИЛИ 37, с первым входом первой группы входов элемента

5

0

5

0

5

0

5

0

5

2И-ИЛИ 38, с вторым входом первой группы входов элемента 2И-ИЛИ 41, с первым входом первой группы входов элемента ЗИ-ИЛИ 31 и с вторыми входами второй и третьей групп входов элемента ЗИ-ИЛИ 32, Выход отсутствие отказа триггера 7 соединен с вторым входом элемента И/И-НЕ 24 и с вторым входом шестого элемента ИЛИ 48 устройства.

Прямой выход триггера 8 соединен с вторым входом второй группы входов элемента 2И-ИЛИ 37, с первым входом первой группы входов элемента 2И-ИЛИ 38, с первым входом первой группы входов элемента 2И-ИЛИ 41, с первым входом второй группы входов элемента ЗИ-ИЛИ 31, с третьим входом первой и с первым входом третьей группы входов элемента ЗИ-ИЛИ 32. Выход отсутствие отказа триггера 8 соединен с вторым входом элемента И/И-НЕ 25, с входом элемента НЕ 42 и с вторым входом элемента ИЛИ 46.

Прямой выход триггера 9 соединен с вторым входом второй группы входов элемента 2И-ИЛИ 38, с первым входом первой группы входов элемента 2И-ИЛИ 39, с первым входом первой группы входов элемента 2И-ИЛИ 35, с вторым входом первой и с первым входом второй групп входов элемента ЗИ-ИЛИ 32. Инверсный выход триггера 9 соединен с вторым входом третьей группы входов элемента ЗИ-ИЛИ 30. Выход отсутствие отказа триггера 9 соединен с первым входом элемента ИЛИ 47, с вторым входом элемента И/И-НЕ 26 и с входом элемента НЕ 43.

Прямой выход триггера 10 соединен с вторым Ъходом второй группы входов элемента 2И-ИЛ И 39, с вторым входом разрешения счета триггера 10 и с вторым входом второй группы входов элемента 2И-ИЛИ 40. Инверсный выход триггера 6.5 соединен с вторым входом второй группы входов элемента ЗИ-ИЛИ 30. Выход отсутствие отказа триггера 10 соединен с вторым входом элемента ИЛИ 49 и с первым входом элемента ИЛИ 50.

Прямой выход элемента И/И-НЕ 23 соединен с вторым входом первой группы входов элемента 2И-ИЛИ 36, с первым входом элемента ИЛИ 48, с первым входом второй группы входов элемента 2И-ИЛИ 33, с первым входом второй группы входов элемента 2И-ИЛИ 27 и с первым входом элемента И/И-НЕ 24. Инверсный выход элемента И/И-НЕ 23 соединен с первым входом второй группы входов элемента 2И-ИЛИ 36, с первым входом первой группы входов элемента 2И-ИЛИ 33, с входом первой группы входов элемента ЗИ-ИЛИ 30 и с первым

входом первой группы входов элемента 2И- ИЛИ 27.

Прямой выход элемента И/И-НЕ 24 соединен с вторым входом первой группы входов элемента 2И-ИЛИ 37, с вторым входом первой группы входов элемента 2И-ИЛ И 34, с первым входом элемента ИЛИ 46, с вхо- доМ первой группы входов элемента 2И- ЛЛу 40, с первым входом второй группы входов элемента 2И-ИЛИ 28 и с первым входом элемента И/И-НЕ 25. Инверсный выход элемента И/И-НЕ 24 соединен с пер- выл входом второй группы входов элемента 2И- 1ЛИ 37, с первым входом второй группы вхо, цов элемента 2И-ИЛЙ 34, с вторым вхо- до1« второй группы входов элемента ЗИ- ИЛИ 31, с первым входом первой группы вхо, 1ов элемента ЗИ-ИЛИ 32, с первым вхо- дом второй группы входов элемента 2И- ИЛИ 40 и с первым входом первой группы входов элемента 2И-ИЛИ 28.

Прямой выход элемента И/И-НЕ 25 со- с вторым входом первой группы входов {элемента 2И-ИЛИ 38, с вторым входом элемента ИЛИ 47, с вторым входом первой группы входов элемента 2И-ИЛИ 35, с третьим входом первой группы входов эле- мен-га 2И-ИЛИ 41, с первым входом второй группы входов элемента 2И-ИЛИ 29 и с первым входом элемента И/И-НЕ 26. Инверс- ный выход элемента И/И-НЕ 25 соединен с пер ым входом второй группы входов эле- мен- а 2И-ИЛИ 38, с входом второй группы вхо;ов элемента 2И-ИЛИ 35, с входом второй руппы входов элемента 2И-ИЛИ 41 и с перЕым входом первой группы входов элемента 2 И-ИЛ И 29.

Прямой выход элемента И/И-НЕ 26 со- един ен с вторым входом первой группы входов элемента 2И-ИЛИ 39, с первым входом элемента ИЛИ 49, с вторым входом третьей труп ты входов элемента ЗИ-ИЛИ 31 и с первым зходом третьей группы входов элемента ЗИ-ИЛИ 30. Инверсный выход элемента И/и{НЕ 26 соединен с первым входом эле- мент|а И 44, с первым входом второй группы входЬв элемента ЗИ-ИЛИ 30 и с первым входрм второй группы входов элемента 2И- ,

выходы элементов 2И-ИЛИ 27-29 соеди- ненц с первыми входами соответствующих им элементов И-НЕ 14-16 одноименного разряда. Выход элемента И 44 соединен с первым уходом элемента И-НЕ 17.

В, ыход элемента ЗИ-ИЛИ 30 соединен с входами разрешения счета триггера 7. Выход элемента ЗИ-ИЛИ 31 соединен со счетным {входом триггера 9. Выход элемента ЗИ-И|ПИ 32 соединен с первым входом раз- решеНия счета триггера 10.

Выходы элементов 2И-ИЛИ 33 и 34 соединены со счетными входами соответствующих им триггеров 7 и 8. Выход элемента 2И-ИЛИ 35 соединен с вторым входом разрешения счета триггера 9.

Выход элемента 2И-ИЛИ 40 соединен с входами разрешения счета триггера 8. Выход элемента 2И-ИЛИ 41 соединен с первым входом разрешения счета триггера 9.

Выход элемента НЕ 42 соединен с вторым входом первой группы входов элемента ЗИ-ИЛИ 31 и с третьим входом второй группы входов элемента ЗИ-ИЛИ 32. Выход элемента НЕ 43 соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ 32.

Выход элемента ИЛИ 46 соединен с третьим входом элемента И 57 устройства, первый, второй и четвертый входы которого соединены соответственно с выходами элементов ИЛИ 48, 47 и 50. Выход элемента ИЛИ 49 является выходом 58 отсутствие частичного отказа устройства. Выход элемента И 57 является выходом 59 отсутствие полного отказа устройства.

Выходы элементов 2И-ИЛИ 36-39 являются соответствующими информационными выходами 57.1-57.4 устройства.

Триггер каждого разряда (фиг. 2) содержит элемент 2И-ИЛИ 60, восемь элементов И-НЕ 61-68, первую 69 и вторую 71 линии задержки, элемент НЕ 70 и элемент 5И- ИЛИ/5И-ИЛИ-НЕ72.

Инверсный S-вход 73 триггера каждого разряда соединен с первым входом элемента И-НЕ 61 и с первым входом первой группы входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72. Первый 74 и второй 76 входы разрешения счета триггера каждого разряда соединены соответственно с первым входом первой и с вторым входом второй групп входов элемента 2И-ИЛ И 60, второй вход первой и первый вход второй групп входов которого соединены с синхровходом 75 триггера каждого разряда. Инверсный R-вход 77 триггера каждого разряда соединен с вторым входом элемента И-НЕ 62 и с первым входом второй группы входов элемента 5И-ИЛИ/5И-ИЛИ- НЕ 72. Rp-вход 78 триггера каждого разряда соединен с первым входом пятой группы входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72.

Выход элемента 2И-ИЛИ 60 соединен с вторым входом первого 61, с первым входом второго 62 элементов И-НЕ, с входом первой 69 линии задержки и с входом элемента НЕ 70.

Выходы первого 61 и второго 62 элементов И-НЕ соединены соответственно с первым входом третьего 63 и с вторым входим четвертого 64 элементов И-НЕ.

Выход третьего 63 элемента И-НЕ соединен с первыми входами четвертого 64 и

пятого 65 элементов И-НЕ, с третьим входом второй.и с четвертым входом четвертой групп входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72.

Выход четвертого 64 элемента И-НЕ соединен с вторым входом третьего 63, с первым входом шестого 66 элементов И-НЕ, с вторым входом первой и с третьим входом третьей групп входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ72.

Выходы пятого 65 и шестого 66 элементов И-НЕ соединены соответственно с первым входом седьмого 67 и с вторым входом восьмого 68 элементов И-НЕ.

Выход первой 69 линии задержки соединен с третьим входом первой и с вторым входом второй групп входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ72.

Выход элемента НЕ 70 соединен с вторыми входами элементов И-НЕ 65 и 66, с первыми входами третьей и четвертой групп входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72 и с входом второй 71 линии задержки.

Выход второй линии 71 задержки соединен с четвертым входом третьей и с третьим входом четвертой групп входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72, прямой выход которого соединен с вторым входом своей пятой группы входов.

Выход седьмого элемента И-НЕ 67 является прямым выходом 79 триггера каждого разряда и соединен с первым входом восьмого 68 элемента И-НЕ и с вторым входом третьей группы входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ72.

Выход восьмого 68 элемента И-НЕ является инверсным выходом 80 триггера каждого разряда и соединен с вторым входом седьмого 68 элемента И-НЕ и с вторым входом четвертой группы входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ 72, инверсный выход которого является выходом 81 отсутствие отказа триггера каждого разряда.

Рассмотрим функциональное назначение логических элементов структуры двоичного счетчика.

Вход 52 (фиг. 1) разрешения предварительной установки устройства позволяет начинать счет с произвольной цифры или от нуля до девяти. Такая организация работы дает возможность использовать двоичный счетчик в режиме 4-разрядных регистров- защелок.

На входы 55.1 и 55.2 подаются импульсы счета. При использовании двоичного счетчика в 4-разрядном исполнении вход 55.2 соединяют с выходом 57.1.

На входы 54.1-54.4 подается код числа, в которое предварительно устанавливается двоичный счетчик перед началом режима счета,

Элемент И-НЕ 11 и первый элемент ИЛИ 12 устройства предназначены для организации режимов работы двоичного счетчика при установке его в О и при предварительной

установке какого-либо изначального кода перед режимом счета.

Элементы И-НЕ 13-17 и 18-22 осуществляют реализацию функции входной логики при установке двоичного счетчика в исход0 ное нулевое или ненулевое состояния.

Элементы И/И-НЕ 23-26 формируют на своих прямых и инверсных выходах управляющие сигналы при коммутации внутренних цепей устройства в момент перестройки

5 работоспособности структуры двоичного счетчика, в зависимости от исправного (неисправного) состояния триггеров 6-10 основных 1-4 разрядов.

Элементы 2И-ИЛ И 27-29 и элемент И 44

0 служат для осуществления коммутации информационных цепей предустановки с входов 54.1-54.4 на установочные R- и S-входы триггеров 6-10 в зависимости от их работоспособности состояния.

5 Элементы ЗИ-ИЛИ 30, 32 и 2И-ИЛИ 35, 40 и 41 предназначены для формирования управляющих сигналов на входы разрешения счета триггеров 7-10, в зависимости от исправного (неисправного) состояния триг0 геров основных 1-4 разрядов устройства.

Элемент ЗИ-ИЛИ 31 и элементы 2И- ИЛИ 33 и 34 осуществляют коммутацию логической цепи счета импульсов, в зависимости от исправного(неисправного)

5 состояния основных разрядов устройства.

Элементы 2И-ИЛИ 36-39 предназначены для коммутации сигналов с прямых выходов триггеров 6-10 на информационные выходы 57.1-57.4 устройства в соответствии

0 с исправным (неисправным) состоянием триггеров 6-9 основных 1-4 разрядов.

Элементы НЕ 42 и 43 осуществляют инвертирование сигналов отсутствие отказа с триггеров 8 и 9 соответственно.

5 Элемент ИЛИ 45 предназначен для согласования уровня сигнала с входа 56 устройства с уровнями сигналов внутри интегральной микросхемы.

Элементы ИЛИ 46-50 и элемент И 51

0 осуществляют формирование сигналов отсутствие частичного отказа и отсутствие отказа устройства. Конструктивное решение предлагаемого двоичного счетчика реализует формирование сигнала отсутствие

5 частичного отказа при исправном состоянии триггеров 6-10. При наличии отказа хотя бы в одном из триггеров 6-10 на выходе элемента ИЛИ 49 формируется сигнал нулевого логического уровня, что означает наличие в устройстве частичного отказа. Сигнал

отсутствие отказа формируется при исправном состоянии триггеров 6-10, или при отказе только одного из триггеров 6-10. В случае отказа в двух и более триггерах - на выходе элемента И 51 формируется сигнал нулевого логического уровня.

Элементы триггера каждого разряда (фиг. 2) имеют следующее функциональное назначение.

, Элемент И 60 реализует входную логику разрешения работы триггера каждого разряда по счетному входу 75.

| Элементы И-НЕ 61-64 образуют схему основного триггера, а элементы И-НЕ 65-68 - схему вспомогательного триггера.

Линия задержки 69 обеспечивает задержку тактового сигнала на время сраба- тысания логических элементов И-НЕ 62, 64

и 6 вр

3, или 61, 63 и 64 соответственно, т.е. на мя не менее 3 ТСр (где ТСр - среднее

время срабатывания одного логического элемента структуры триггера).

; Элемент НЕ 70 предназначен для организации двухтактного режима работы триггер з при наличии одного синхровхода 75, Креме того, на выходе элемента НЕ 70 вырабатывается сигнал строба сравнения сигналов на противоположных плечах (выходах) основного и вспом2гательного триггеров (см. фиг|, 2, точка А и Q, точка А и Q) в режиме хранения информации.

Линия задержки 71 обеспечивает также задЬржку инвертированного тактового сигнала на время срабатывания логических элементов И-НЕ 66, 68 и 67, или 65, 67 и 68 соответственно, т.е. на время не менее 3 .

Элемент 5И-ИЛИ/5И-ИЛИ-НЕ 72 осуществляет на своих группах входов контроль правильности срабатывания всех лоп веских элементов структуры триггера. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера) на его прямом выходе формируется сигнал отказ, который посредством своей обратной связи через пятую группу входов осуществляет так называемый эффект самозахвата, то ест1, устанавливается в устойчивое состояние логического нуля на своем инверсном выхЬде (функционирует как однофазный триггер).

|При установке в исходное состояние среЬств функционального контроля триггера каждого разряда на их вход 78 подается сигнал логического нуля, так как в момент подэчи питания, в силу случайного характетереходных процессов, однофазный

ра

ТРИ1

rep 72 может установиться в нулевое

состояние на своем инверсном выходе.

0

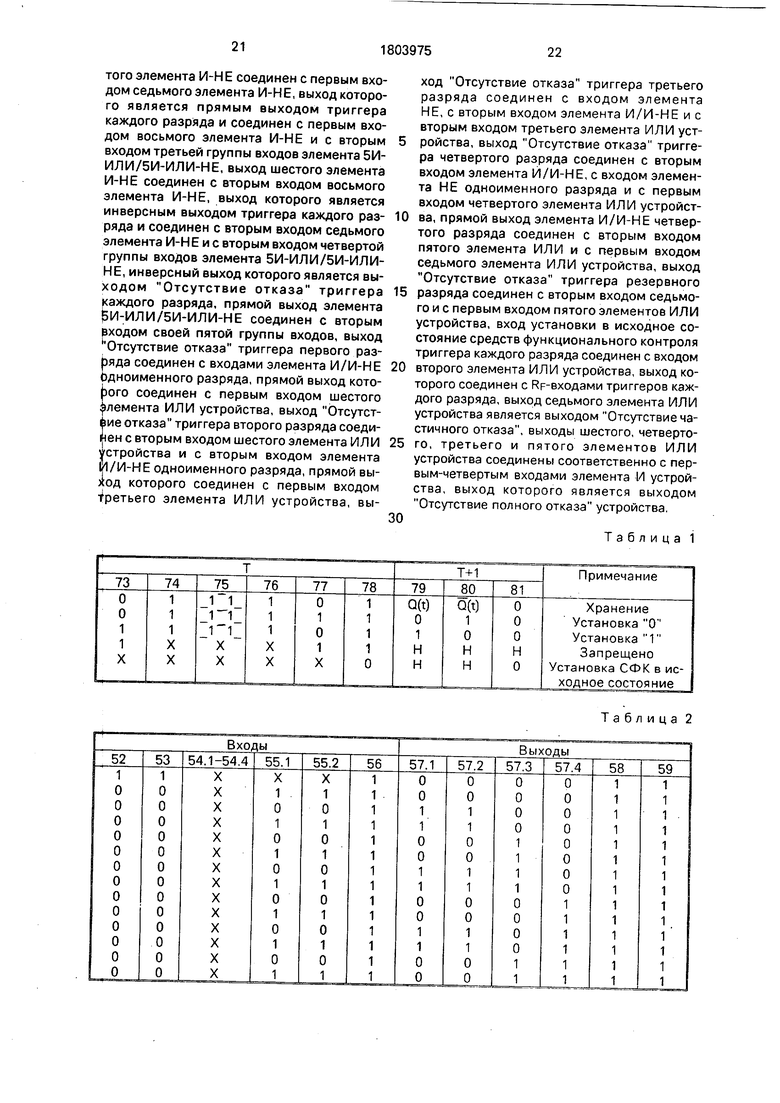

Далее при исправном состоянии всех логических элементов структуры триггера работа триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в сокращенной таблице 1 переходов триггера:

где X - безразличное состояние сигнала на соответствующем входе триггера любого из разрядов;

0 d(t)-предыдущее состояние сигнала на прямом выходе триггера;

Q(t)- предыдущее состояние сигнала на инверсном выходе триггера любого из разрядов;

5 Н - неопределенное состояние сигнала на соответствующем выходе триггера любого из разрядов.

Рассмотрим подробнее каждый из режимов работы триггера каждого разряда.

Режим установки О. В этом режиме на входе 73 триггера любого из разрядов присутствует сигнал логического О, на входах 74, 76, 77 и 78 - сигнал логической 1, а на входе 75 - синхроимпульс (см. п. 2, табл. 1).

5 В результате воздействия этих сигналов на выходах элементов И-НЕ 61 и 62 устанавливаются сигналы логической единицы и логического нуля соответственно. На выходе элемента И-НЕ 64 (фиг. 3, US) вырабатыва0 ется сигнал логической единицы, что приводит к формированию сигнала логического нуля на выходе элемента И-НЕ 63 через время ЗТср срабатывания с момента поступленияположительного фронта

5 синхроимпульса на вход 75. Таким образом, переходные процессы в первой ступени триггера каждого разряда завершаются после срабатывания трех логических элементов И-НЕ 62, 64 и 63. В результате на выходе

0 элемента И-НЕ 63 должен быть установлен уровень логического нуля, а на выходе элемента И-НЕ 64 - уровень логической единицы. Именно через такое же время 3 ТСр на выходе линии задержки 69 появится сигнал

5 строба сравнения, который поступит на первую и вторую группы входов элемента 5И- ИЛИ/5И-ИЛ И-НЕ 72. Так как при правильном срабатывании логических элементов И-НЕ 61-64 сигналы на входах 73 и 77 - разнопр0 лярные, как и сигналы на выходах 80 и 79 соответственно. Следовательно, как первая, так и вторая группы входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ 72 останутся закрытыми и на его инверсном выходе, как и выходе 81

5 триггера.будет присутствовать сигнал логической единицы. Третья и четвертая группы входов элемента 5И-И Л И /5И-И Л И-Н Е 72 на время действия синхроимпульса закрыты нулевым потенциалом с выхода элемента НЕ 70. В случае отказа любого из четырех

элементов И-НЕ 61-64 на выходе элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72 формируется нулевой логический уровень сигнала, а на прямом его выходе - сигнал логической единицы, который через свою пятую группу входов удерживает элемент 5И-ИЛИ/5И- ИЛИ-НЕ в устойчивом состоянии логического нуля на его инверсном выходе.

По окончании действия синхроимпульса на входе 75 высокий логический уровень сигнала с выхода элемента НЕ 70 (фиг. 3,1)с) разрешает перенос состояния триггера первой ступени в триггер второй ступени триггера каждого разряда, путем открытия элементов И-НЕ 65 и 66. Нулевой потенциал с выхода элемента И-НЕ 66 устанавливает в единичное состояние выход элемента И-НЕ 68 и затем в нулевое состояние выход элемента И-НЕ 67. Контроль правильности срабатывания элементов И-НЕ 65-68 триггера второй ступени производится на третьей и четвертой группах входов элемента 5И- ИЛИ/5И-ИЛ1/1-НЕ 72 сравнением состояний сигналов на выходах А и А с состояниями сигналов на выходах 80 и 79 соответственно. Сигнал сравнения состояний этих сигналов вырабатывается на выходе линии задержки 71, который поступает на третью и четвертую группы входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ 72. Время сраЁнения наступает также через время ЗТср срабатывания с момента появления отрицательного фронта синхроимпульса на входе 75 триггера каждого разряда. В случае отказа хотя бы одного из элементов И-НЕ 65-68 на инверсном выходе элемента 5И- ИЛИ/5И-ИЛИ-НЕ 72 будет сформирован сигнал нулевого логического уровня.

Режим установки 1. В этом режиме на входах 73, 74, 76 и 78 присутствует сигнал единичного логического уровня, на входе 77 - сигнал нулевого логического уровня, а на входе 75 - синхроимпульс (п. 3, табл. 1). В момент действия синхроимпульса производится запись единичного состояния в триггер первой ступени, а триггер второй ступени в этот момент времени будет находиться в режиме хранения предыдущего состояния, так как на вторые входы элементов И-НЕ 65 и 66 поступает нулевой потенциал с выхода элемента НЕ 70. По окончании действия синхроимпульса производится установка единичного состояния в триггер второй ступени. Контроль правильности срабатывания логических элементов триггеров первой и второй ступеней триггера каждого разряда осуществляется аналогично вышеописанному режиму установки в О.

Режим хранения. В этом режиме на входы 73 и 77 триггера каждого разряда подаются сигналы нулевого логического уровня, на входы 74, 76 и 78 - сигналы единичного логического уровня, а на вход 75 - синхроимпульс (см. р. 1, табл. 1). В результате этого на выходах первого и второго 61 и 62 элементов И-НЕ формируются сигналы единичного логического уровня, что практически будет означать для триггера первой ступени подтверждение ранее принятого

состояния. Схема контроля правильности срабатывания первой ступени к моменту поступления сигнала сравнения на входы первой и второй групп элемента 5И-ИЛИ/5И-ИЛИ-НЕ 72 будет заблокирована нулевыми логическими уровнями сигналов на входах 73 и 77 триггера каждого разряда.. Совпадение состояний первой и второй ступеней производится аналогично контролю совпадения состояний в режиме установки в О.

Таким образом, в триггере каждого разряда двоичного счетчика осуществляется контроль правильности срабатывания всех его логических элементов во всех его режимах функционирования. В случае отказа любого из логических элементов триггера любого из разрядов на его выходе 81 отсутствие отказа сформируется сигнал логического нуля.

Двоичный счетчик, имея в каждом разряде вышеприведенный триггер, работает следующим образом.

Для установки двоичного счетчика в нулевое состояние на входы 52 и 53 подаются

сигналы единичного логического уровня. В результате этого на выходе элемента И-НЕ 11 формируется сигнал нулевого логического уровня, который способствует выработке на выходах элементов И-НЕ 13-17 разрядов

единичных логических уровней сигналов, которые, в свою очередь, устанавливают соответствующие им триггеры 7-10 в нулевое состояние. Заметим, что состояние сигналов на входах 54,1-54.4 предустанова устройства в этом случае не влияют на состояния логических уровней сигналов на выходах элементов И-НЕ 13-17. Для установки в исходное состояние средств функционального контроля (СФК) триггера

каждого разряда на вход 56 устройства подается сигнал логического нуля. Подача сигнала установки в исходное состояние СФК может производиться одновременно с установкой двоичного счетчика в нулевое состояние, так и в любое другое время.

Для установки двоичного счетчика в состояние, отличное от нулевого,,на вход 52 разрешения предустанова подается сигнал . логического нуля (при этом на входе 53 дол

ж0н быть сигнал логической единицы). В результате этого на двух входах элементов И-JHE 13-17 присутствуют сигналы логиче- скрй единицы и значение, в которое устанавливаются триггеры 7-10, зависит от значения сигнала на соответствующем входе 54.1-54.4 предустанова устройства.

При исправном состоянии триггеров 6- 9 Основных разрядов в режиме счета на выходах отсутствие отказа этих триггеров присутствуют сигналы логической единицы. В атом случае единичными разрешающими сигналами открыты следующие логические элементы устройства: первые группы входов элементов 2И-ИЛИ 36-39 (разрешается прохождение на информационные выходы 57.|1-57.4 устройства сигналов с прямых вы- хоАов триггеров 6-10 одноименных разрядов), вторые группы.входов элементов 27-29 (разрешается прохождение сигналов с входов 54.1-54.4 предустанова устройства на установочные входы тригге- poi 6-9 одноименных разрядов), вторая группа входов элемента 2И-ИЛИ 33 (разрешается прохождение сигналов с входа 55.2 устройства на счетный вход триггера 7), треггья группа входов элемента ЗИ-ИЛИ 30 (разрешается режим счета триггером 7 при единичном состоянии сигнала на инверсном выходе триггера 9), первая группа вхо- ДОЕ элемента 2И-ИЛИ 40 (разрешается рем им счета триггера 8), первая группа входов; элемента 2И-ИЛИ 34 (разрешается про

хох

дение импульсов счета с прямого

дов

элемента ЗИ-ИЛИ 32 значения в этом

выхода триггера 7), первая группа входов эле лента 2И-ИЛИ 41 (разрешено прохождение счетного режима триггера 9 при единичных состояниях триггеров 7 и 8), первая группа входов элемента 2И-ИЛИ 35 (разрешается счетный режим триггера 9 при его единичном состоянии), третья группа входов элемента ЗИ-ИЛИ 31 (разрешается прохождение импульсов счета с входа 55.2 уст{; ойства на счетный вход триггера 9), от- крыгое или закрытое состояния групп вхо

случае не имеют, так как прямой выход триггере 10 отключен от информационного выход 57.4 устройства.

Остальные группы входов логических элементов 2И-ИЛИ 27-29, ЗИ-ИЛИ 30 и 31, а 2И-ИЛИ 33-35, 36-38,40 и 41 закрыты нулевыми логическими уровнями сигналов.

рчет импульсов в устройстве произво- дитф по следующей логической ветви: с входа 55.1 устройства - на счетный вход триггера 6, через первую группу входов элемента 2И-ИЛИ 36 - на выход 57.1 устройст0

5

0

5

0

5

0

5

0

5

ва; с входа 55.2 устройства, через вторую группу входов элемента 2И-ИЛИ 33 - на счетный вход триггера 7, через первую группу входов элемента 2И-ИЛИ 37 - на выход 57:2 устройства, через первую группу входов элемента 2И-ИЛИ 34 - на счетный вход триггера 8, через первую группу входов элемента 2И-ИЛИ 38 - на выход 57.3 устройства, через первую группу входов элемента 2И-ИЛИ 35 - на вход разрешения счетного режима работы триггера 9, с прямого выхода триггера 9 через первую труппу входов элемента 2И-ИЛ И 39 - на выход 57.4 устройства.

В таблице 2 приведено состояние входов и выходов устройства в режиме счета импульсов.

. В таблице 3 приведены значения состояний двоичного счетчика при его предварительной установке в ненулевое состояние с использованием входов 54.1-54,4 и исправной работе триггеров 6-9 основных разрядов.

При неисправном состоянии одного из триггеров 6-9 на соответствующем выходе отсутствие отказа формируется сигнал нулевого логического уровня.

Рассмотрим принцип перехода устройства на работоспособную структуру на примерах, когда произошел отказ триггеров 6 и 8.

При отказе триггера 6 на его выходе отсутствие отказа формируется сигнал нулевого логического уровня и данный триггер исключается из режима функционирования двоичного счетчика. Это производится следующим образом.

На прямом и инверсном выходах элементов И/И-НЕ 23-26 в результате появления нулевого потенциала на выходе отсутствие отказа триггера 6 изменяются логические уровни сигналов - на прямых выходах формируются нулевые логические уровни сигналов, а на инверсных - единичные. Вследствие этого закрываются первые группы входов элементов 2И-ИЛИ 36-39 и открываются их вторые группы входов, подключая тем самым к информационным входам 57.1-57.4 устройства прямые выходы триггеров 7-10 соответственно. Кроме того, закрываются первые группы входов элементов 2И-ИЛИ 27-29 и открываются их вторые группы входов, а также элемент И 44. В результате этого входы 54.1-54.4 предустанова устройства подключаются к установочным входам триггеров 7-10 последующих разрядов. Аналогично перестраивается и логическая ветвь подсчета импульсов в устройстве. Открытая в этом случае первая

группа входов элемента 2И-ИЛИ 33 позволяет поступать синхроимпульсам с входа 55.1 устройства на счетный вход триггера 7, с прямого выхода триггера 7 информация поступает через вторую группу входов эле- мента 2И-ИЛИ 36 на выход 57.1 устройства. С входа 55.2 через открытую в этом случае вторую группу входов элемента 2И-ИЛИ 34 - на счетный вход триггера 8, с прямого выхода триггера 8 состояние сигнала (и его изменения) через вторую группу входов элемента 2И-ЙЛИ 37 поступает на выход 57.2 устройства, и через вторую группу входов элемента ЗИ-ИЛИ 31 - на счетный вход триггера 9. С прямого выхода триггера 9 состоя- ние сигнала (и его изменения) через вторую группу входов элемента 2И-ИЛИ 38 поступает на выход 57.3 устройства и через первую группу входов элемента ЗИ-ИЛИ 32 - на разрешающий вход режима счета триггера 10. С прямого выхода триггера 10 состояние сигнала (и его изменения) через вторую группу входов элемента 2И-ИЛИ 39 поступает на выход 57.4 устройства. Необходимо отметить, что первые и вторые входы разре- шения режима счета триггеров 9 и 10 соединены по принципу селектора, т.е. по схеме ИЛИ между собой и по схеме И индивидуально со счетным входом.

Алгоритм работы двоичного счетчика в этом случае полностью подчиняется закону, описанному таблицами состояний входов и выходов, представленными в табл. 2 и 3.

При отказе триггера 8 на его выходе отсутствие отказа формируется нулевой сигнал и данный триггер исключается из режима функционирования двоичного счетчика. Сигнал, поступая с выхода отсутствие отказа триггера 8 на вход элемента И/И- НЕ 25, приводит к тому, что на его прямом и инверсном выходах, а также на аналогичных выходах элемента И/И-НЕ 26 изменяют свои логические значения на инверсные. Следовательно, первый и второй разряды в этом случае будут функционировать знало- гично случаю исправности всех основных разрядов, а третий и четвертый разряды - случаю неисправности триггера 6. Таким образом, логическая структура двоичного счетчика перестраивается на работоспособ- ную структуру, вытесняя триггер 8. Прямые выходы триггеров 6 и 7 подключены на одноименные им выходы 57.1 и 57.2 устройства, а прямые выходы триггеров 9 и 10 подключены на выходы 57.3 и 57.4 соответ- ственно.

Замена отказавших второго и четвертого триггеров производится аналогично вышерассмотренным примерам.

Таким образом, в предлагаемом двоичном счетчике осуществляется автоматическая реконфигурация его логической структуры при отказе одного из основных разрядов, что создает возможность обеспечения работоспособности этого устройства с возникшим частичным отказом и, следовательно, повышается эксплуатационная отказоустойчивость двоичного счетчика в целом.

Формула изобретения Двоичный счетчик, содержащий элемент И-НЕ, первый элемент ИЛИ, основные и резервный разряды, первый разряд содержит два элемента И-НЕ, элемент И/И-НЕ, элемент 2И-ИЛ И и триггер, второй разряд - три элемента 2И-ИЛИ, два элемента И-НЕ, элемент И/И-НЕ, элемент ЗИ-ИЛИ и триггер, третий разряд - четыре элемента 2И- ИЛИ, два элемента И-НЕ, элемент И/И-НЕ, элемент НЕ и триггер, четвертый разряд - четыре элемента 2И-ИЛИ, два элемента И- НЕ, элемент И/И-НЕ, элемент ЗИ-ИЛИ и триггер, резервный разряд содержит два элемента И-НЕ, элемент ЗИ-ИЛИ и триггер, вход разрешения предварительной установки устройства соединен с первым входом элемента И-НЕ устройства, второй вход которого объединен с входом первого элемента ИЛИ и с входом установки в О устройства, вход предварительной установки первого разряда соединен с первым входом первого элемента И-НЕ одноименного разряда и с вторым входом первой группы входов первого элемента 2И-ИЛИ второго разряда, первый синхровход устройства соединен со счетным входом триггера первого разряда и с вторым входом первой группы входов второго элемента 2И-ИЛИ второго разряда, вход предварительной установки второго разряда соединен с вторым входом второй группы входов первого элемента 2И- ИЛИ одноименного разряда и с вторым входом первой группы входов первого элемента 2И-ИЛИ третьего разряда, второй синхровход устройства соединен с вторым входом второй группы входов вторых элементов 2И-ИЛИ второго и третьего разрядов, с первым входом третьей группы входов элемента ЗИ-ИЛИ четвертого и со счетным входом триггера резервного разрядов, вход предварительной установки третьего разряда соединен с вторым входом второй группы входов первого элемента 2И- ИЛИ одноименного и с вторым входом первой группы входов первого элемента 2И-ИЛИ четвертого разрядов, вход предварительной установки четвертого разряда соединен с вторым входом второй группы входов первого элемента 2И-ИЛИ одноименного и с вторым входом элемента И резервного разрядов, выход элемента И-НЕ устройства соединен с третьими входами первых элементов И-НЕ и с вторыми входами вторых Элементов И-НЕ каждого, включая и резервный, разряда, выход первого элемента ИЛИ устройства соединен с вторыми входами первых элементов И-НЕ каждого, включая и резервный, разряда, выход первого Элемента И-НЕ каждого разряда соединен с первым входом второго элемента И-НЕ и с Инверсным S-входом триггера одноименного разряда, выход второго элемента И-НЕ каждого разряда соединен с инверсным R- входом триггера одноименного разряда, г|рямой выход элемента И/И-НЕ первого разряда соединен с вторым входом первой группы входов элемента 2И-ИЛИ одноименного разряда, с первым входом второй группы входов второго и первого элементов 2И- ИЛИ и с первым входом элемента И/И- Ь|Е второго разряда, инверсный выход эле- м|ента И/И-НЕ первого разряда соединен с гёервым входом второй группы входов эле- Цента 2И-ИЛИ одноименного разряда, с первым входом первой группы входов пер- в )го и второго элементов 2И-ИЛИ и с входом первой группы входов элемента 3 4-ИЛИ второго разряда, прямой выход триггера первого разряда соединен с пер- в им входом первой группы входов элемента 2 4-ИЛИ одноименного разряда, выход первого элемента 2И-ИЛИ второго разряда соединен с первым входом первого элемента Hj-HE одноименного разряда, выход эле- мЫта ЗИ-ИЛИ второго разряда соединен с входами разрешения счета триггера одно- и(йенного разряда, выход второго элемента 2И-ИЛИ второго разряда соединен со счет- ннм входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов элемента 2И-ИЛИ первого разряда, с первым входом первой группы входов третьего эле- 2И-ИЛИ, с первым входом первой группы входов второго элемента 2И-ИЛИ третьего разряда, с вторым входом первой группы входов четвертого элемента 2И- ИДШ, с первым входом первой группы вхо- до|в элемента ЗИ-ИЛИ четвертого разряда и с торыми входами второй и третьей групп вхрдов элемента ЗИ-ИЛИ резервного разряда прямой выход элемента И/И-НЕ второго разряда соединен с вторым входом первой группы входов третьего элемента 2И-ИЛИ одноименного разряда, с вторым входом пе эвой группы входов второго элемента 2ИИЛИ, с входом первой группы входов четвертого элемента 2И-ИЛИ, с первым входом второй группы входов первого элемента 2И- ИЛИ и с первым входом элемента И/И-НЕ

третьего разряда, инверсный выход элемента И/И-НЕ второго разряда соединен с первым входом второй группы входов третьего элемента 2И-ИЛИ одноименного разряда, с первым входом первой группы входов первого элемента 2И-ИЛИ, с первым входом второй группы входов четвертого элемента 2И-ИЛИ, с первым входом второй группы входов второго элемента 2И-ИЛИ третьего разряда, с вторым входом второй группы

входов элемента ЗИ-ИЛИ четвертого и с первым входом первой группы входов элемента ЗИ-ИЛИ резервного разряда, выход первого элемента 2И-ИЛИ третьего разряда соединен с первым входом первого элемента И-НЕ одноименного разряда, выход четвертого элемента 2И-ИЛИ третьего разряда соединен с входами разрешения счета триггера одноименного разряда, выход второго элемента 2И-ИЛИ третьего разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ второго разряда, с первым входом первой группы

входов третьего элемента 2И-ИЛИ третьего разряда, с первым входом первой группы входов четвертого элемента 2И-ИЛИ, с первым входом второй группы входов элемента ЗИ-ИЛИ четвертого разряда, с третьим входом первой и с первым входом третьей групп входов элемента ЗИ-ИЛИ резервного разряда, прямой выход элемента И/И-НЕ третьего разряда соединен с вторым входом первой группы входов третьего элемента

2И-ИЛИ одноименного разряда, с вторым входом первой группы входов второго элемента 2И-ИЛИ, с вторым входом первой группы входов четвертого элемента 2И- ИЛИ, с первым входом второй группы входов первого элемента 2И-ИЛИ и с первым входом элемента И/И-НЕ четвертого разряда, инверсный выход элемента И/И-НЕ третьего разряда соединен с первым входом второй группы входов третьего элемента 2И-ИЛИ одноименного разряда, с входом второй группы входов второго элемента 2И- ИЛИ, с входом второй группы входов четвертого элемента 2И-ИЛИ и с первым входом первой группы входов первого элемента 2И-ИЛИ четвертого разряда, выход элемента НЕ третьего разряда соединен с вторым входом первой группы входов элемента ЗИ-ИЛИ четвертого разряда и с третьим входом второй группы входов элемента

ЗИ-ИЛИ резервного разряда, выход первого элемента 2И-ИЛИ четвертого разряда соединен с первым входом первого элемента И-НЕ одноименного разряда, выход четвертого элемента 2И-ИЛИ четвертого разряда соединен с первым входом разрешения счета триггера одноименного разряда, второй вход разрешения счета которого соединен с выходом второго элемента 2И-ИЛИ одноименного разряда, выход элемента ЗИ-ИЛИ четвертого разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ третьего разряда, с первым входом первой группы входов третьего элемента 2И-ИЛИ четвертого разряда, с первым входом первой группы входов второго элемента 2И-ИЛИ четвертого разряда, с вторым входом первой и с первым входом второй групп входов элемента ЗИ-ИЛИ резервного разряда, инверсный выход триггера четвертого разряда соединен с вторым входом третьей группы входов элемента ЗИ- ИЛИ второго разряда, прямой выход эле- мента И/И-НЕ четвертого разряда соединен с первым входом третьей группы входов элемента ЗИ-ИЛИ второго разряда, с вторым входом первой группы входов третьего элемента 2И-ИЛИ четвертого раз- ряда, с вторым входом третьей группы входов элемента ЗИ-ИЛИ четвертого разряда, инверсный выход элемента И/И-НЕ четвертого разряда соединен с первым входом второй группы входов элемента ЗИ-ИЛИ второго разряда, с первым входом второй группы входов третьего элемента 2И-ИЛИ четвертого разряда и с первым входом элемента И резервного разряда, выход элемента НЕ четвертого разряда соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ резервного разряда, выход элемента И резервного разряда соединен с первым входом первого элемента И-НЕ одноименного разряда, выход эле- мента ЗИ-ИЛИ резервного разряда соединен с первым входом разрешения счета триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2И-ИЛИ четвертого разряда, со своим вторым входом разрешения счета и с вторым входом второй группы входов четвертого элемента 2И-ИЛИ третьего разряда, инверсный выход триггера резервного разряда соединен с вторым входом второй группы входов элемента ЗИ-ИЛИ второго разряда, выходы третьих элементов 2И-ИЛИ перво- го-четвёртого разрядов являются соответствующими информационными выходами устройства, отличающийся тем, что, с целью повышения эксплуатационной отказоустойчивости, он дополнительно содержит шесть элементов ИЛИ и элемент И устройства, а каждый разряд, включая и резервный, содержит триггер, включающий в свою структуру элемент 2И-ИЛИ, восемь элементов И-НЕ, две линии задержки, элемент НЕ и элемент 5И-ИЛИ/5И-ИЛИ-НЕ, причем инверсный S-вход триггера каждого разряда соединен с первым входом первого элемента И-НЕ и с первым входом первой группы входов элемента 5И-ИЛИ/5И-ИЛИ- НЕ, первый и второй входы разрешения счета триггера каждого разряда соединены соответственно с первым входом первой и с вторым входом второй групп входов элемента 2И-ИЛИ, второй вход первой и первый вход второй групп входов элемента 2И-ИЛИ объединены и соединены со счетным входом триггера каждого разряда, инверсный R-вход триггера каждого разряда соединен с вторым входом второго элемента И-НЕ и с первым входом второй группы входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ, Rp-входустановки в исходное состояние средств функционального контроля триггера каждого разряда соединен с первым входом пятой группы входов элемента 5И-ИЛИ/5И-ИЛИ- НЕ, выход элемента 2И-ИЛИ соединен с вторым входом первого, первым входом второго элемента И-НЕ, входом первой линии задержки и входом элемента НЕ, выход которого соединен с входом второй линии задержки, с первыми входами третьей и четвертой групп входов элемента 5И-ИЛИ/5И- ИЛИ-НЕ и с вторыми входами пятого и шестого элементов И-НЕ, выход первой линии задержки соединен.с третьим входом первой и с вторым входом второй групп входов элемента 5И-ИЛИ/5И-ИЛИ-НЕ, выход второй линии задержки соединен с третьим входом четвертой и с четвертым входом третьей групп входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ, выход первого элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, выход которого соединен с третьим входом второй, с четвертым входом четвертой групп входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ, с первым входом пятого и с первым входом четвертого элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого соединен с вторым входом первой, с третьим входом третьей групп входов элемента 5И-ИЛИ/5И-ИЛИ- НЕ, с первым входом шестого и с вторым входом третьего элементов И-НЕ, выход пятого элемента И-НЕ соединен с первым входом седьмого элемента И-НЕ, выход которого является прямым выходом триггера каждого разряда и соединен с первым входом восьмого элемента И-НЕ и с вторым входом третьей группы входов элемента 5И- ИЛИ/5И-ИЛИ-НЕ, выход шестого элемента И-НЕ соединен с вторым входом восьмого элемента И-НЕ, выход которого является инверсным выходом триггера каждого разряда и соединен с вторым входом седьмого элемента И-НЕ и с вторым входом четвертой группы входов элемента 5И-ИЛИ/5И-ИЛИ- НЕ, инверсный выход которого является выходом Отсутствие отказа триггера каждого разряда, прямой выход элемента 5И-ИЛИ/5И-ИЛИ-НЕ соединен с вторым входом своей пятой группы входов, выход Отсутствие отказа триггера первого разряда соединен с входами элемента И/И-НЕ Одноименного разряда, прямой выход которого соединен с первым входом шестого флемента ИЛИ устройства, выход Отсутст- Јие отказа триггера второго разряда соеди- йен с вторым входом шестого элемента ИЛИ устройства и с вторым входом элемента И/И-НЕ одноименного разряда, прямой выход которого соединен с первым входом третьего элемента ИЛИ устройства, вы0

5

0

5

0

ход Отсутствие отказа триггера третьего разряда соединен с входом элемента НЕ, с вторым входом элемента И/И-НЕ и с вторым входом третьего элемента ИЛИ устройства, выход Отсутствие отказа триггера четвертого разряда соединен с вторым входом элемента Й/И-НЕ, с входом элемента НЕ одноименного разряда и с первым входом четвертого элемента ИЛИ устройства, прямой выход элемента И/И-НЕ четвертого разряда соединен с вторым входом пятого элемента ИЛИ и с первым входом седьмого элемента ИЛИ устройства, выход Отсутствие отказа триггера резервного разряда соединен с вторым входом седьмого и с первым входом пятого элементов ИЛИ устройства, вход установки в исходное состояние средств функционального контроля триггера каждого разряда соединен с входом второго элемента ИЛИ устройства, выход которого соединен с Rp-входами триггеров каждого разряда, выход седьмого элемента ИЛИ устройства является выходом Отсутствие частичного отказа, выходы шестого, четвертого, третьего и пятого элементов ИЛИ устройства соединены соответственно с первым-четвертым входами элемента И устройства, выход которого является выходом Отсутствие полного отказа устройства.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

Таблица 2

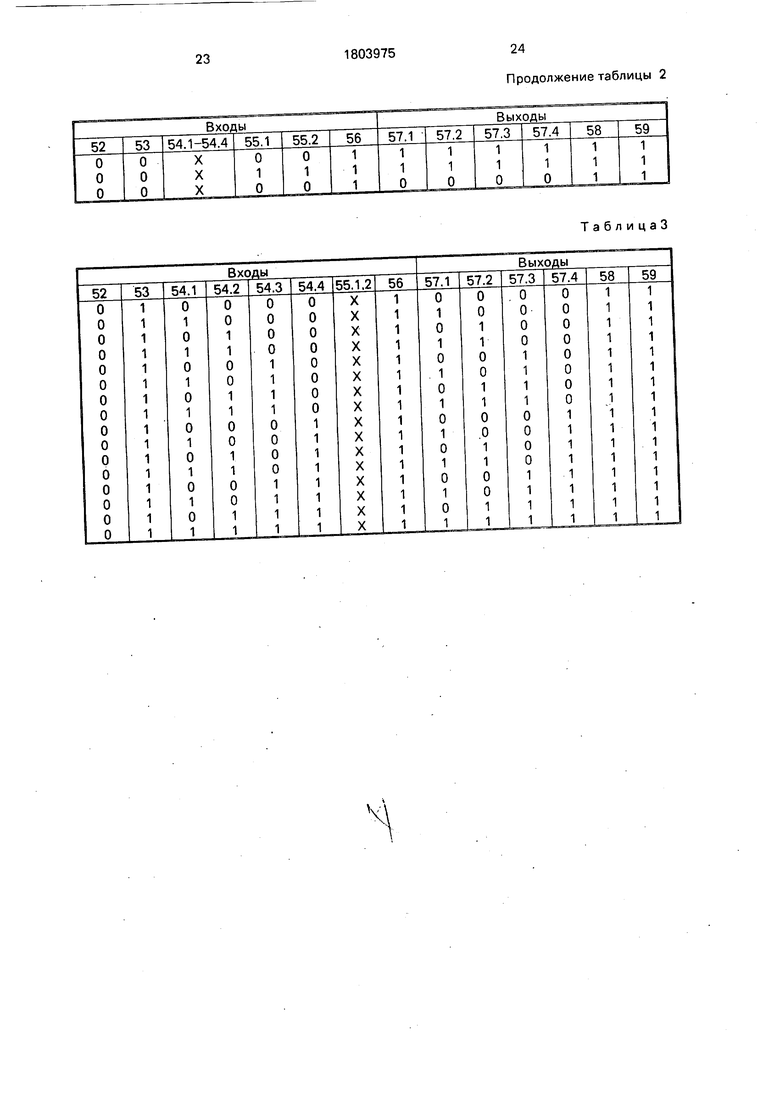

Продолжение таблицы 2

ТаблицаЗ

Авторы

Даты

1993-03-23—Публикация

1991-04-23—Подача