ел

00

00 Од

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения арифметических и логических операций в процессорах ЭВМ и устройствах автоматики.

Целью изобретения является повышение быстродействия устройства.

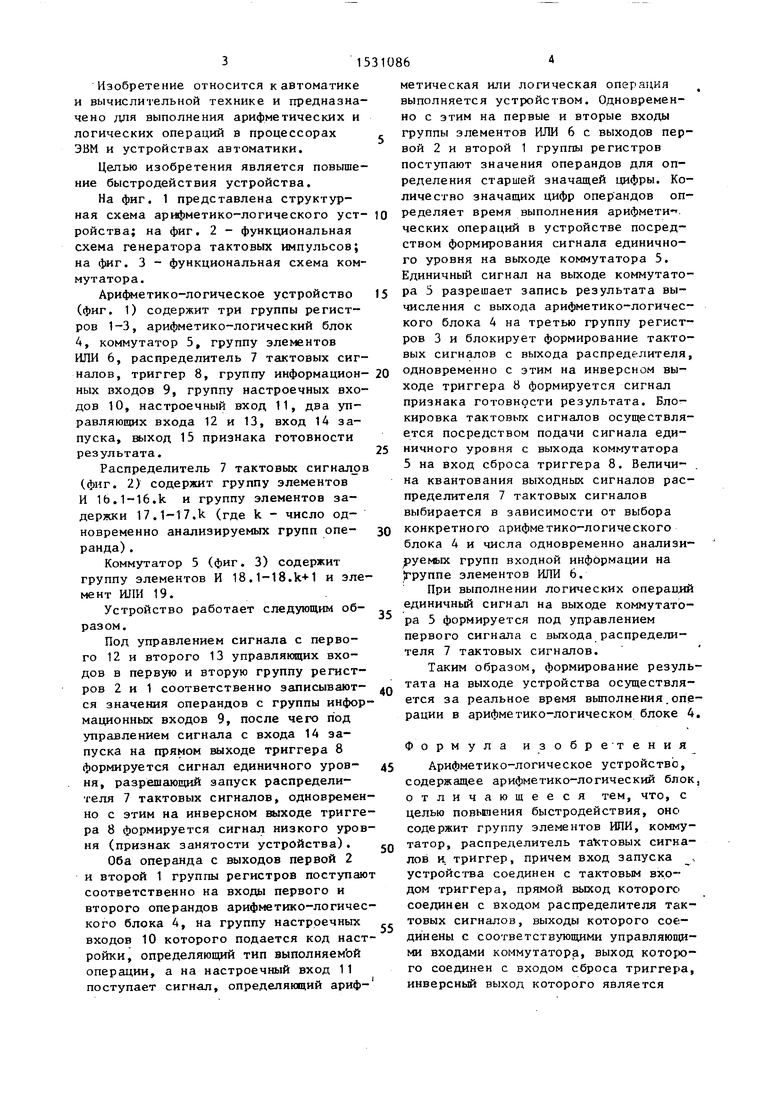

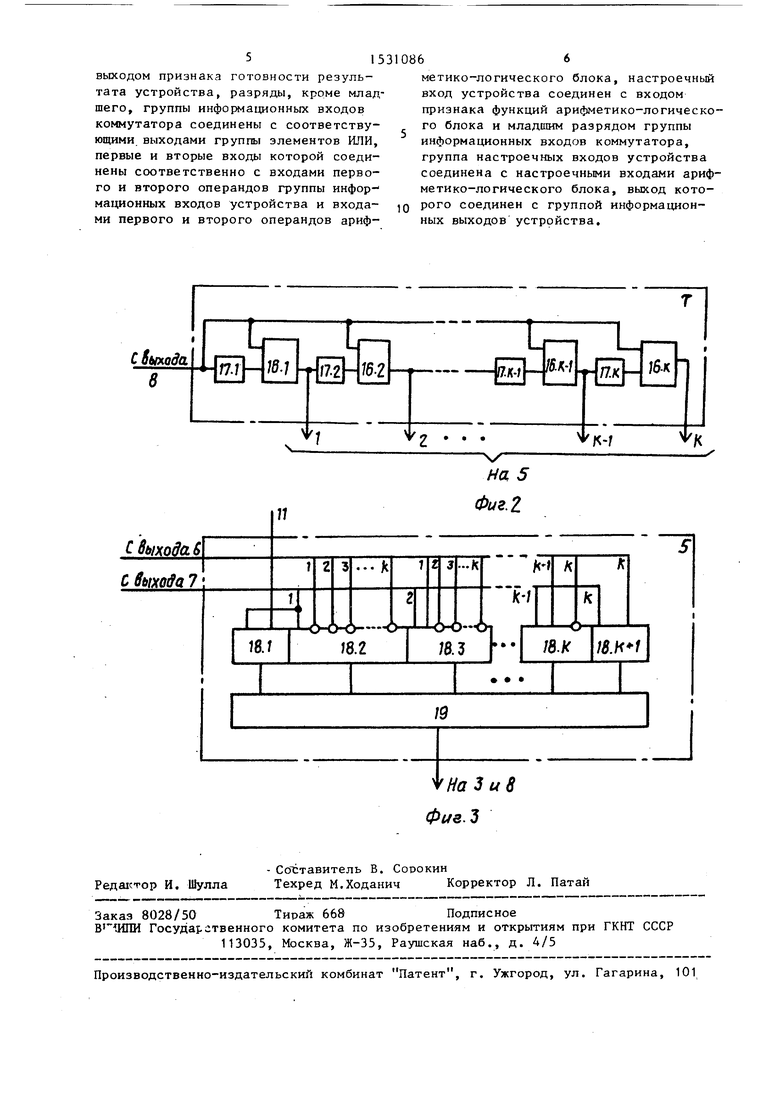

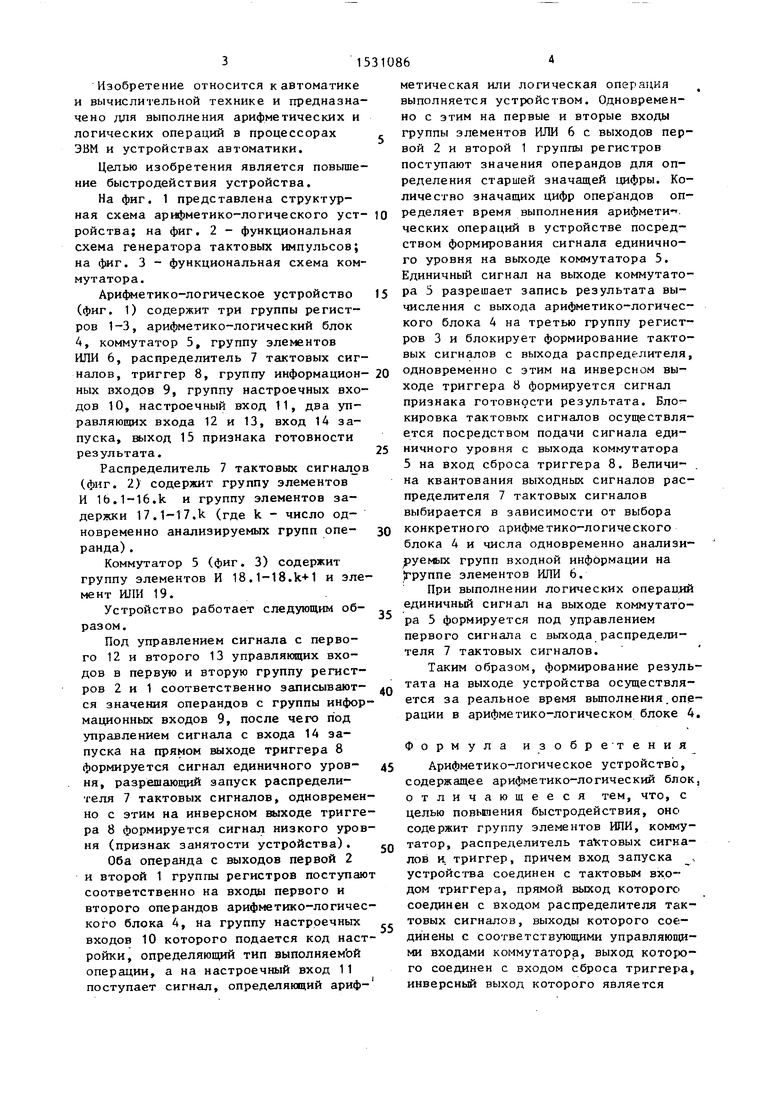

На фиг. 1 представлена структурная схема арифметико-логического уст- ройства; на фиг. 2 - функциональная схема генератора тактовых импульсов; на фиг. 3 - функциональная схема коммутатора.

Арифметико-логическое устройство (фиг. 1) содержит три группы регистров Т-З, арифметико-логический блок 4, коммутатор 5, группу элементов ИЛИ 6, распределитель 7 тактовых сигналов, триггер 8, группу информацион- ных входов 9, группу настроечных входов 10, настроечный вход 11, два управляющих входа 12 и 13, вход 14 запуска, выход 15 признака готовности результата.

Распределитель 7 тактовых сигналов (фиг. 2) содержит группу элементов И Ib.1-I6.k и группу элементов задержки 17.1-17.k (где k - число од новременно анализируемых групп one- ранда).

Коммутатор 5 (фиг. 3) содержит группу элементов И 18.1-18.k+1 и элемент ШШ 19.

Устройство работает следующим об- разом.

Под управлением сигнала с первого 12 и второго 13 управляющих входов в первую и вторую группу регистров 2 и 1 соответственно записывают- ся значения операндов с группы информационных входов 9, после чего под управлением сигнала с входа 14 запуска на прямом выходе триггера 8 формируется сигнал единичного уров- ня, разрешающий запуск распределителя 7 тактовых сигналов, одновременно с этим на инверсном выходе триггера 8 формируется сигнал низкого уровня (признак занятости устройства).

Оба операнда с выходов первой 2 и второй 1 группы регистров поступаю соответственно на входы первого и второго операндов арифметико-логического блока 4, на группу настроечных входов 10 которого подается код настройки, определяющий тип выполняем ой операции, а на настроечный вход 11 поступает сигнал, определяющий арифметическая или логическая операция выполняется устройством. Одновременно с этим на первые и вторые входы группы элементов ИЛИ 6 с выходов первой 2 и второй 1 группы регистров поступают значения операндов для определения старшей значащей цифры. Количество значащих цифр операндов определяет время выполнения арифмети. ческих операций в устройстве посредством формирования сигнала единичного уровня на выходе коммутатора 5. Единичный сигнал на выходе коммутатора 3 разрешает запись результата вычисления с выхода арифметико-логического блока 4 на третью группу регистров 3 и блокирует формирование тактовых сигналов с выхода распределителя, одновременно с этим на инверсном выходе триггера 8 формируется сигнал признака готовности результата. Блокировка тактовых сигналов осуществляется посредством подачи сигнала единичного уровня с выхода коммутатора 5 на вход сброса триггера 8. Величина квантования выходных сигналов распределителя 7 тактовых сигналов выбирается в зависимости от выбора конкретного арифметико-логического блока 4 и числа одновременно анализируемых групп входной информации на группе элементов ИЛИ 6.

При выполнении логических onepaujdi единичный сигнал на выходе коммутатора 5 формируется под управлением первого сигнала с выхода распределителя 7 тактовых сигналов.

Таким образом, формирование результата на выходе устройства осуществляется за реальное время вьтолнения.операции в арифметико-логическом блоке 4

Формула изобре тения

Арифметико-логическое устройство, содержащее арифметико-логический блок отличающееся тем, что, с целью повышения быстродействия, оно содержит группу элементов ИЛИ, коммутатор, распределитель таХтовых сигналов к, триггер, причем вход запуска устройства соединен с тактовым входом триггера, прямой выход которогс соединен с входом распределителя тактовых сигналов, выходы которого соединены с соответствующими управляюп1И- ми входами коммутатора, выход которю- го соединен с входом сброса триггера, инверсный выход которого является

выходом признака готовности результата устройства, разряды, кроме младшего, группы информационных входов коммутатора соединены с соответствующими выходами группы элементов ИЛИ, первые и вторые входы которой соединены соответственно с входами первого и второго операндов группы инфор-- мационных входов устройства и входами первого и второго операндов ариф-

метико-логического блока, настроечный вход устройства соединен с входом признака функций арифметико-логического блока и младшим разрядом группы информационных входов коммутатора, группа настроечных входов устройства соединена с настроечными входами арифметико-логического блока, выход которого соединен с группой информационных выходов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Вычислительное устройство | 1983 |

|

SU1170448A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения арифметических и логических операций. Цель изобретения - повышение быстродействия устройства. Последнее содержит три группы регистров 1-3, арифметико-логический блок 4, коммутатор 5, группу элементов ИЛИ 6, распределитель тактовых сигналов 7, триггер 8. Операнды через группу информационных входов записываются в первую и вторую группы регистров. Одновременно значения операндов поступают на группу элементов ИЛИ для выявления количества значащих цифр. Количество значащих цифр операндов определяет реальное время выполнения арифметических операций в устройстве. Логические операции выполняются за один такт работы устройства. 3 ил.

п

На, 5

Фиг.2.

А

| Ячейка однородной структуры | 1973 |

|

SU711563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дроздов Е.А., Пятибратов А.П | |||

| Электронные вычислительные машины Единой Системы.-М.: Машиностроение, 1981, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

Авторы

Даты

1989-12-23—Публикация

1987-09-08—Подача