Изобретение относится к вычислительной технике, в частности к one- . ративным запоминающим устройствам с самоконтролем, и может быть использовано при создании последних в интегральном исполнении.

Цель изобретения - упр ощение и повьш1ение быстродействия устройства,

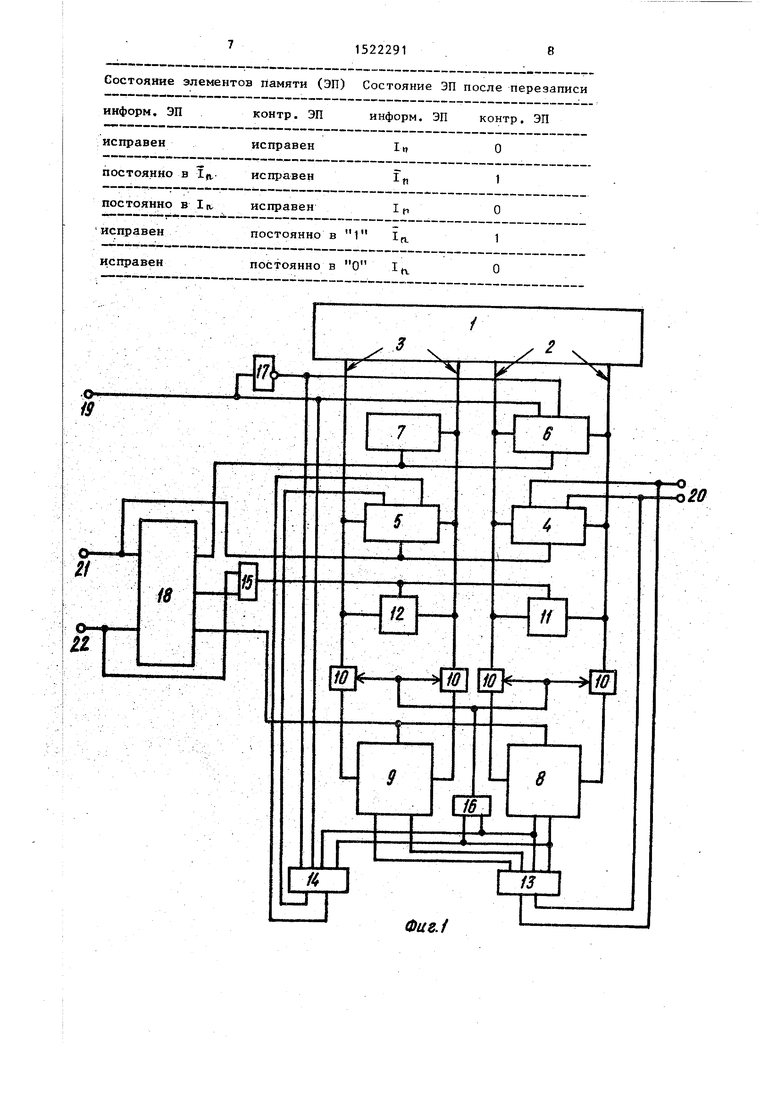

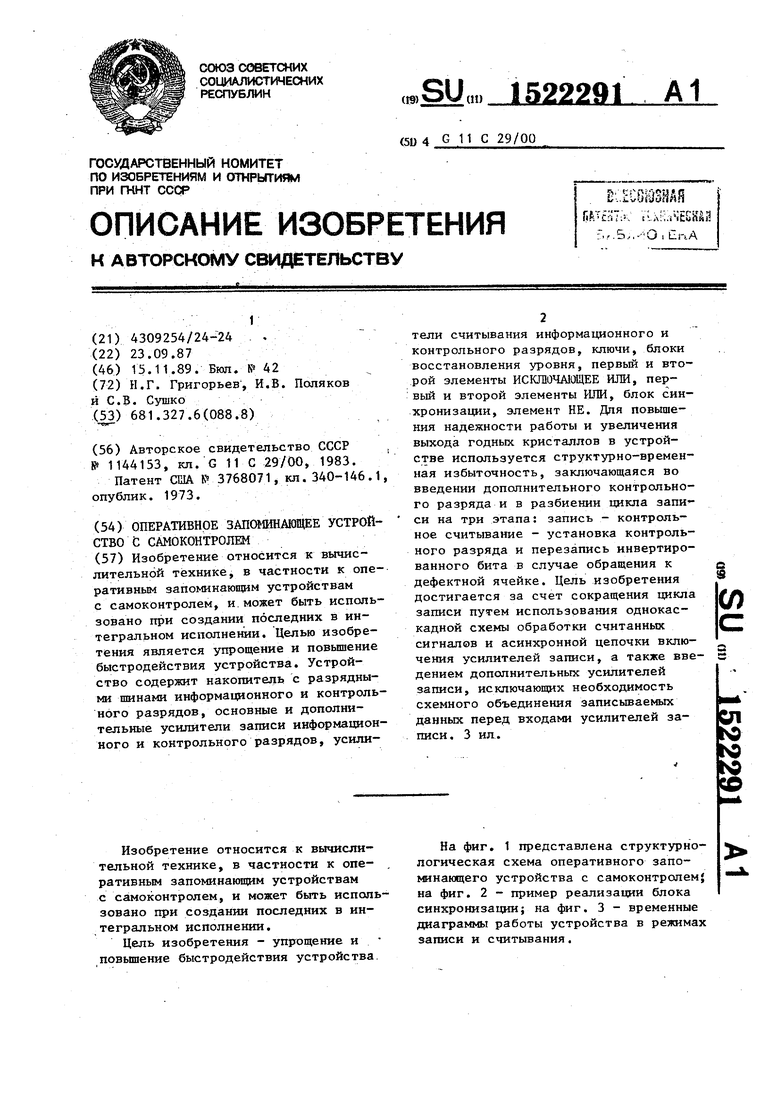

На фиг. 1 представлена структурно- логическая схема оперативного запоминающего устройства с самоконтролем$ на фиг. 2 - пример реализации блока синхронизации; на фиг. 3 - временные диаграммы работы устройства в резкимах записи и считывания.

Таблица состояний информационного и контрольного элементов памяти до и после операции перезаписи (режим внешней записи).

Устройство содержит накопитель 1, разрядные шины информационного 2 и контрольного 3 разрядов, основные усилители записи информационного 4 и контрольного 5 разрядов, дополнитель ные усилители записи .информационного 6 и контрольного 7 разрядов, усилители считывания информационного 8 и контрольного 9 разрядов, ключи 10, блоки восстановления уровня разряд- ных шин информациондого 11 и контрольного 12 разрядов, первый 13 и втрой 14 ; элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, пер вь1й 15 и второй 16 элементы ИЛИ, элемент НЕ 17, блок синхронизации 18, информационные вход 19 и парафазный выход 20, вход режима 21 и вход вы- бррки 22 устройства.

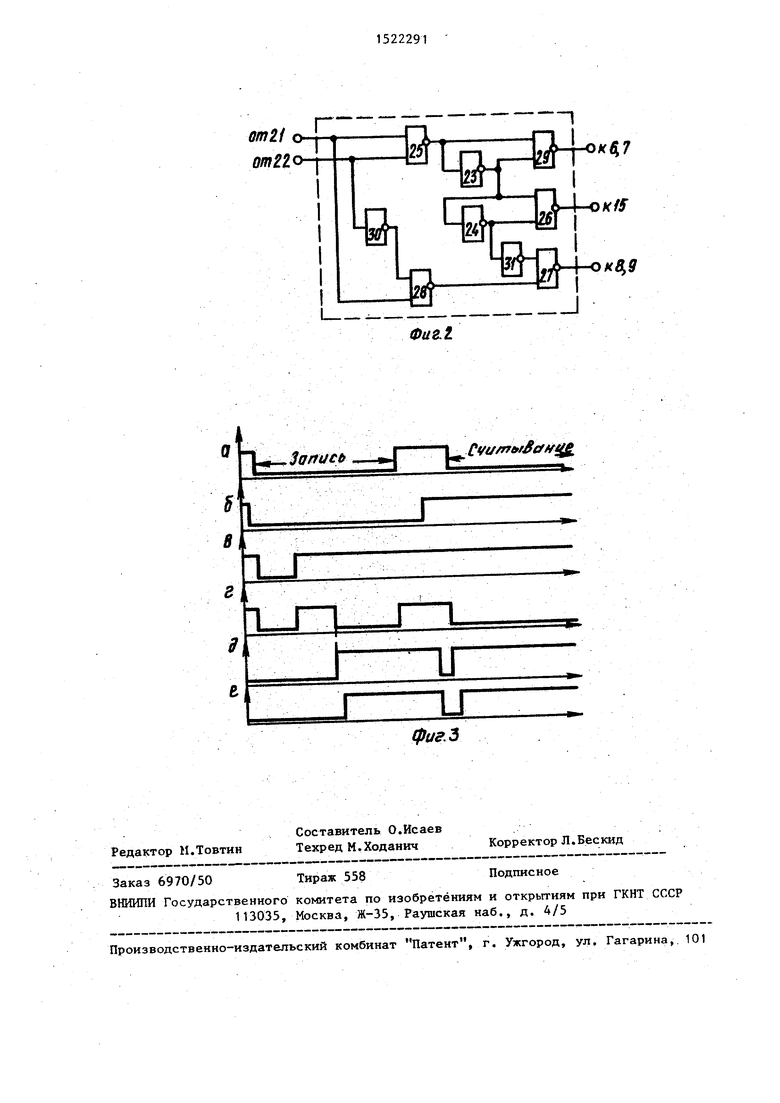

Блок синхронизации 18 содержит первый 23 и второй 24 элементы за- держки с инверсией, первьй 25 и второй 26 элементы ИЛИ-НЕ, первый 27, второй 28, третий 29 элементы И-НЕ, первый 30 и ;второй 31 элементы НЕ.

Устройство работает следующим образом..

На временной диаграмме фиг. 4 отображены сигналы на входе 21 ре- лдима (&), на входе 22. выборки устройства (р),. на выходе элемента И-НЕ 29 (В), на вькоде элемента ИЛИ 15 (г), на выходе элемента И-НЕ 27 (ч) и на выходе элемента ИЛИ 16 (е).

На этапе предварительной записи (состояние О на входе 21 устрой- ства) разрешена работа дополнитель- ньгх усилителей записи 6 и 7, на управляющие входы которьгх с выхода блока синх:ронизации поступает сигнал низкого уровня (фиг. 4 а), при- чем в информационный разряд записывается бит данных с входа 19 устройства, а в контрольный разряд - нулевой бит. При этом длительность эта- па предварительной записи определя- ется задержкой элемента 23 блока синхронизации 18. Далее в ОЗУ производится восстановление потенциалов разрядных щин 2 и 3 с помощью бло- , ков 11 и 12, что является обязатель- ной и стандартной процедурой для, например, КМОП ОЗУ, на базе которых предполагается практическая реализация предлагаемого устройства.

Q n

5

0

5

0 З Q

Длительность этапа восстановления уровней (фиг. 42) задается элементом задержки 24 блока синхронизации 18 . (состояние 1 на его первом выходе).

После этапа восстановления, который имеет также место в перерывах меж- дУ обращениями к ОЗУ, вьтолняется считывание ранее записанных данных, их сравнение с истинными значениями и повторная запись должным образом преобразованных данных. Преобразование считанной информации в предлагаемом устройстве осуществляется с помощью двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и 14, причем элемент 13 используется также и в режиме считывания для возможного инвертирования считанного информационного сигнала.

В таблице приведены примеры результатов преобразования данных для случаев записи в информационный разряд бита данных (напомним, что допускается наличие дефекта только в одном элементе.памяти пары, в информационном или в контрольном).

-.1 .-; ...... ;

По завершении преобразования считанных данных устройство переходит в режим повторной записи. Традиционным решением формирования сигнала на перезапись является использование в блоке синхронизации 18 третьего элемента задержки, задающего длительность этапа считывания. Однако в данном ОЗУ переход в режим перезаписи осуществляется автоматически, при срабатывании усилителя считывания 8 информационного разряда. Так, в отсутствие сигнала уровня 1 на управляющих входах усилителей считывания 8 и 9, на всех их парафазных выходах поддерживаются состояния О (это можно наблюдать в стандартных синхронных усилителях считывания на КМОП-транзисторах), а на парафазных выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 13 - состояния 1. Это обеспечивает удержание в закрытом состоянии основных усилителей записи 4 и 5. После срабатывания усилителя считывания 8 на одном из его входов установится сигнал уровня 1, который проходит на выход элемента ИЛИ 16 и обеспечивает отключение усилителей считывания 8 и 9 от разрядных шин 2 и 3 с помощью ключей 10. Далее, изменение состояния на выходах усилителей считывания 8 и 9 приводит к переключению элементов

515

ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и 14 и, следовательно, к включению усилителей запи- .си 4 и 5 на запись вновь сформированных данных (фиг. 4 е).

В режиме внешнего считывания цикл работы устройства по сравнению с режимом записи намного короче, поскольку он состоит только из считывания данных усилителями 8 и 9 и инвертиро- вания информационного бита, если контрольный бит равен 1. В режиме считьгоания сигнал с входа режима 21 устройства запрещает работу основных усилителей записи 4 и 5, Это предот- вращает возможность перезаписи истинного значения информационного бита, когда элемент памяти контрольного разряда постоянно находится в состоянии 1,.т.е. обеспечивает йнвёртирЬ- вание считанной информации,

Фо рмула из обр е- тения

- - - - . . / Оперативное запоминающее устройство с самоконтролем, содержащее накопитель, разрядные шины нуля и еди- ниць информационного и контрольного разрядов которого соединены с одно- именными разрядными выходами основных усилителей записи соответственно информационного и контрольного разрядов, усилители считывания информационного и кон тр ол ьн ог о ра.з.ря дов, пер - вый и второй элементй ИС КЛЮЧАЮЩЕЕ ШШ, первый и второй элементы ИЛИ, элемент НЕ, о т л и ч а и щ ее с я тем, что, с целью упрощения и повы

шения быстродействия устройства, в

него введены дополнительные усилите ли записи информационного и контроль кого разрядов, первый и второй блоки восстановления уровня, ключи по одному на каждую разрядную шину накопителя и блок синхронизации, причем управляющие входы оснавных усилителей записи информационного и контрольного разрядов являются входом режима устройства и соединены с первым входом блока синхронизации, второй вход которого является входом выборки устройства и подключен к первому входу первого элемента ИЛИ, выход которого соединен с управляющими вхо

Q )5 20

.25

35

40

45

50

55

1. .

дами первого и второго блоков во сстановления уровня, разрядные шины нуля и единицы которых подключены к разрядным шинам нуля и единицы соответственно информационного и контрольного разрядов накопителя и к информационным входам соответ,ствующих ключей, второй вход первого элемента ИЛИ со.единен с первым выходом блока синхронизации, второй выход которого подключен к управляющим входам дополнительных усилителей записи информационного и контрольного разрядов, третий выход блока син5фони- зации соединен с управляющими входами усилителей считывания информационного и контрольного разрядов разрядные тайны нуля и. единицы которых подключены к выходам соответствующих КЛЮЧЕЙ, парафазные вьпсоды усилителя считывания информационного разряда соединены с парафазными входами первой группы первого и второго элементов ИСКШОЧАЮЩЕЕ ИЛИ и с входами второго эле;мента ИЛИ, выход которого подключен к управляющим входам ключей, парафазные вьпсоды усилителя считывания контрольного разряда соединены с парафазными входами второй группы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, парафазные выходы которого являются па- paфaзны и информационными выходами устройства и подключены к парафазным информационным входам основного усилителя записи информационного разряда, парафазные информационные входы основного усилителя записи контрольного разряда соединены с парафазными выходами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, парафазные входы второй группы которого подключены к парафаз- HbW информационным входам дополнительного усилителя записи информационного разряда и соответственно к входу и выходу элемента НЕ, вход которого является информационным входом устройства, разрядные вшны нуля и единицы дополнительного усилителя записи информационного разряда соединены с одноименными разрядными шинами накопителя; разрядная птна нуля дополнительного усилителя записи контрольного разряда подключена к одноименной разрядной шине накопителя.

Состояние элементов памяти (ЭП) Состояние ЭП после перезаписи информ. ЭП контр. ЭП информ. ЭП контр. ЭП

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Логическое запоминающее устройство | 1978 |

|

SU752479A1 |

| Постоянное запоминающее устройство на элементах памяти с 2 @ логическими состояниями | 1983 |

|

SU1552228A1 |

| ДЕТЕКТОР ИЗЛУЧЕНИЯ | 1991 |

|

RU2006878C1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

Изобретение относится к вычислительной технике, в частности к оперативным запоминающим устройствам с самоконтролем, и может быть использовано при создании последних в интегральном исполнении. Целью изобретения является упрощение и повышение быстродействия устройства. Устройство содержит накопитель с разрядными шинами информационного и контрольного разрядов, основные и дополнительные усилители записи информационного и контрольного разрядов, усилители считывания информационного и контрольного разрядов, ключи, блоки восстановления уровня, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы ИЛИ, блок синхронизации, элемент НЕ. Для повышения надежности работы и увеличения выхода годных кристаллов в устройстве используется структурно-временная избыточность, заключающаяся во введении дополнительного контрольного разряда и в разбиении цикла записи на три этапа: запись - контрольное считывание - установка контрольного разряда и перезапись инвертированного бита в случае обращения к дефектной ячейке. Цель изобретения достигается за счет сокращения цикла записи путем использования однокаскадной схемы обработки считанных сигналов и асинхронной цепочки включения усилителей записи, а также введением дополнительных усилителей записи, исключающих необходимость схемного объединения записываемых данных перед входами усилителей записи. 3 ил.

исправен

постоянно в Ift

исправен исправен

1« If.

О 1

om2f от 22

.3QffUCI

Фаг1

Cvt//rrMfe/ tff

| Авторское свидетельство СССР | |||

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1144153A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США р 3768071,кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1989-11-15—Публикация

1987-09-23—Подача