(Л

1, накопитель 2, второй регистр 3, парный триггер 4, первый элемент И 5, второй триггер 6, второй 7 н третий 8 элементы И, первьд 9 и второй 10 счетчики, элемент МЛН 11, третий триггер 12, коммутатор 13, сумматор- вычитатель 14, третий регистр 15, первьш 16, второй 17 и трегий 18 элеравл иие режимом осуществляется при помопд сигналов, подаваемых на первую 22 и вторую 23 шины управления. При подаче сигналов на обе шины на выходе элемента ИЛИ 11 независимо от состояния третьего триггера 12 имеется сигнал и, следовательно, третий регистр 15 находится в режиме обнуле

| название | год | авторы | номер документа |

|---|---|---|---|

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для коррекции временных искажений | 1985 |

|

SU1270797A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1984 |

|

SU1840542A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для вычисления функции | 1985 |

|

SU1280614A1 |

| Устройство для определения экстремальных значений | 1989 |

|

SU1615747A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

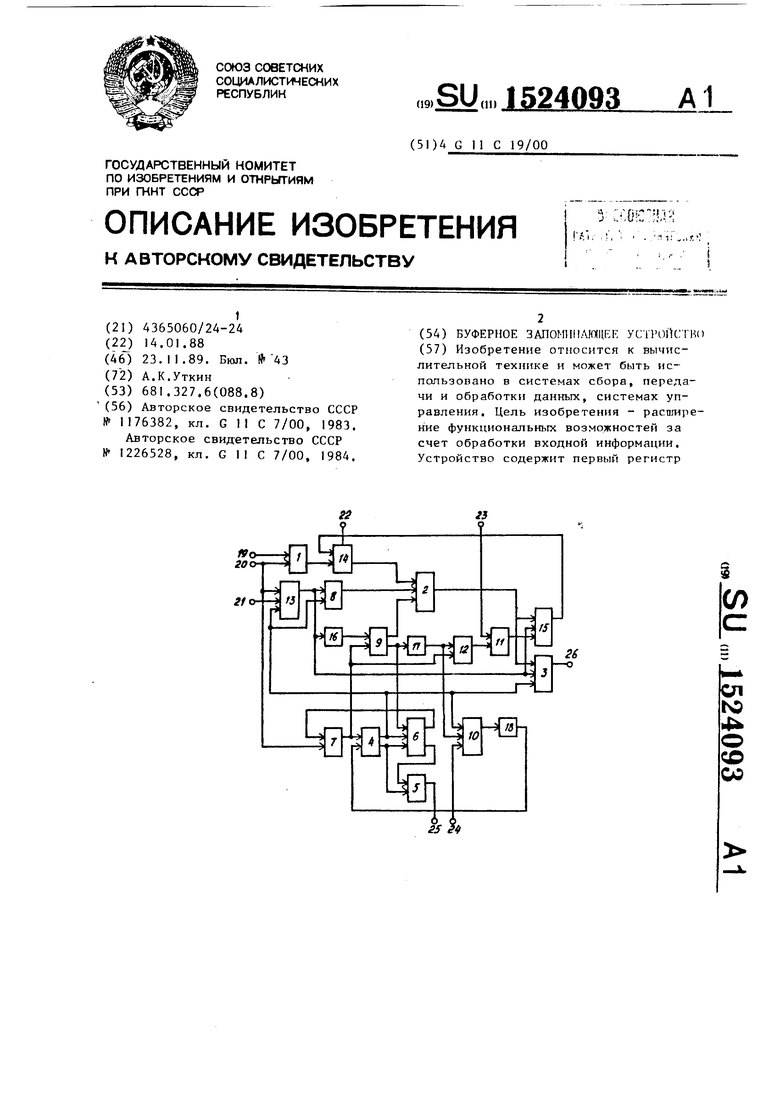

Изобретение относится к вычислительной технике и может быть использовано в системах сбора, передачи и обработки данных, системах управления. Цель изобретения - расширение функциональных возможностей за счет обработки входной информации. Устройство содержит первый регистр 1, накопитель 2, второй регистр 3, первый триггер 4, первый элемент И 5, второй триггер 6, второй 7 и третий 8 элемент И, первый 9 и второй 10 счетчики, элемент ИЛИ 11, третий триггер 12, коммутатор 13, сумматор-вычитатель 14, третий регистр 15, первый 16, второй 17 и третий 18 элементы НЕ, шину 19 входной информации, шину 20 записи, шину 21 чтения, первую 22 и вторую 23 шины управления, шину 24 кода числа циклов, шину выходной информации. Устройство может работать в режиме преобразования заносимой в накопитель информации или же в режиме без преобразования. Управление режимом осуществляется при помощи сигналов, подаваемых на первую 22 и вторую 23 шины управления. При подаче сигналов на обе шины на выходе элемента ИЛИ 11 независимо от состояния третьего триггера 12 имеется сигнал и, следовательно, третий регистр 15 находится в режиме обнуления, а сумматор-вычитатель 14 находится в режиме суммирования. При этом на выходах блока 14 и, следовательно, на информационных входах накопителя 2 будет информация. При отсутствии сигнала на шине 23 будет выполняться преобразование информации. 1 ил.

менты НЕ, шину 19 входной информации, Q я, а сумматор-вычитатель 14 нахо- шину 20 записи, шину 21 чтения, первую 22 и вторую 23 шины управления, шину 24 кода числа циклов, шину выходной информации. Устройство может работать в режиме преобразования за- 15 носимой в накопитель информации или же в режиме без преобразования. Упдится в режиме суммирования. При это на выходах блока 14 и, следовательно на информационных входах накопителя 2 будет информация. При отсутствии сигнала на шине 23 будет выполняться преобразование информации. 1 ил.

Изобрететге относится к вычислительной , в частности к запо- м1П1ающим устро1 ствам, и может быть использовано в системах сбора, передачи и обработки данных, системах управления .

Целью изобретения является расширение функциональных возможностей за счет обработки входной информации.

На чертеже представлена структурная схема буферного запоминающего устройства,

Устройство содержит первый регистр 1, накопитель 2, последовательно соединенный с ним второй регистр 3, первый триггер 4, соедииен1йр й с первым элементом И 5 и вторым триггером б, второй элемент И 7, выход которого соединен с входом установки в О первого триггера 4, третий элемент И 8, первый 9 и второй 10 счетчики, элемент ИЛИ 11, третий триггер 12, коммутатор 13. Кроме того, устройство содержит сумматор-вычитатель 14, вход1 1 первой и второй групп которого соединены соответственно с Выходами третьего 15 и первого 1 регистров, а выходы - с информационными входами накопителя 2, первый элемент НЕ 16, включенный между выходом коммутатора 13 и входом си1гхронизации первого счетчика 9, второй элемент НЕ 17, включенный ме;кду выходом переполнени первого счетчика 9 и входом синхронизации второго счетчика 10, третий элемент НЕ 8,-включенный между выходом переполнения второго счетчика 10 и входом установки в 1 первого

я, а сумматор-вычитатель 14 нахо-

дится в режиме суммирования. При этом на выходах блока 14 и, следовательно, на информационных входах накопителя 2 будет информация. При отсутствии сигнала на шине 23 будет выполняться преобразование информации. 1 ил.

5

0

5

0

5

0

5

триггера 4. Информационные входы 1У устройства соединены с информационными входами первого регистра 1, вход 20 записи служит для подачи импульсов записи, а вход 21 чтения - для подачи импульсов считывания. Первый 22 и второй 23 входы задания режима устройства соединены соответственно с управляющим входом сумматора-вы- читателя 14 и с первым входом элемента ИПИ 11, информационные выходы 26 устройства соединены с выходами второго регистра 3, входы 24 задания числа циклов устройства соединены с информационными входами второго счет- шка, выход 25 запрета записи устройства соединен с выходом первого элемента И 5.

Устройство работает следующим образом.

В исходном состоянии первый 4 и второй 6 триггеры находятся в единичном состоянии, а третий триггер 12 - в нулевом. При этом на управляющем вхоле комьгутатора 13, входе задания режима второго счетчика 10, входе установки в О второго регистра 3 и втором входе третьего элемента И 8, а значит, и на его выходе сигнал отсутствует, на выход коммутатора 13 разрешается прохождение сигнала с входа 21 чтения, второй счетчик 10 находится в режиме записи кода числа цикгов, представленного в виде двоич- ногс инверсного, второй регистр 3 на- хоД1:тся в режиме записи информации из ьсакопителя 2, а накопитель 2 постоянно находится в режиме считывания

5152409

информации из ячейки, адрес которой соответствует состоянию первот о счетчика 9. Поскольку накоиитель 2 находится в режиме считывания, то безразлично, какая информация на его информационных входах, а следовательно, на входах первой и второй групп сум- матора-вычитателя 14. Поскольку второй триггер 6 находится в единичном ю состоянии, то на первом входе второго элемента И-7 сигнал (Имеется, а на втором входе первогб элемента И 6 и, следовательно, выходе 25 запрета записи сигнал отсутствует.15

При появлении импульса записи на входе 20 записи на выходе второго элемента И 7 также появляется импульс, устанавливающий первый триг

гер А в нулевое состояние по входу установки в О, третий триггер 12 в единичное состояние по входу установки в 1, а первый счетч ик 9 - в нулевое состояние по входу начальной установки. При этом на инверсном выходе первого триггера 4 появляет:я сигнал, который разрешает прохождение через коммутатор 13 импульсов с входа 20 записи, открывает третий элемент И 8 по второму входу и устанавливает второй триггер 6 в нулевое состояние по входу установки в О, второй регистр 3 в режим обнуления, а второй счетчик 10 - в режим счета Появление сигнала на выходе третьего триггера 12 приводит к появлению СИ1- нала на выходе элемента ИЛИ 11 независимо от наличия сигнала на втором входе 23 задания режима устройства и следовательно, третий регистр 15 будет в режиме обнуления. Исчезновение сигнала на прямом выходе второго, триггера 6 приводит к исчезновению сигнала на первом входе, а значит, и на выходе второго элемента И 7. Длительность импульса на выходе данного элемента определяется, таким образом, суммар1й 1м временим задержки распространения сигнала самого элемента, первого 4 и второго 6 триггеров.

По переднему фронту импульса записи производится запись входной информации в первый регистр 1 и, следовательно, она появляется на входах второй группы сумматора-вычитателя 14, на входы первой группы которого поступает информация с выходов третьего регистра 15, находящегося в режиме обнуле1шя. Кроме того, импульс запи

5

0

0

5

0

5

0

5

си, поступающий через коммутатор К и открытьш третий элемент И 8 на nxtin записи-чтения накопителя 2, усчакав-- ливает накопитель в режим записи информации, поступающей с выходов сумматора-вычитателя 14, на время, равное длительности данного импульса. По окончании импульса записи сигнал на выходе коммутатора 13 исчезает и, следовательно, накопитель 2 устанавливается в режим считывания, а на выходе первого элемента НЕ 1 б формируется положительный перепад, по которому первый счетчик 9 увеличивает свое состояние на единицу.

Таким образом по импульсу записи производится запись входной информации в ячейку накопителя 2, адрес, которой соответствует состоянию первого счетчика 9, а по окончании данного импу.г1ьса - увеличение на единицу состояния первого счетчика 9 и, следовательно, адреса ячейки накопителя 2.

При поступлении следующего 1гмпуль- са записи весь процесс записи и изменения состояния первого счетчика 9 повторяется.

При поступелнии К-го импульса записи, причем К 2, где N - разрядность первого счетчика 9, происходит запись инфopмaц rи в последнюю ячейку накопителя 2, а на выходе переполнения первого счетчика 9 вырабатывается отрицательный импульс, свидетельствующий об окончании первого цикла записи в накопитель. При этом второй триггер 6 не меняет своего состояния, так как удерживается в нулевом состоянии сигналом с выхода первого триггера 4, а на выходе второго элемента НЕ 17 формируется положитель шли импульс, устанавливающий третий триг- нер 12 в нулевое состояние, и по переднему фронту которого второй счетчик 10 увеличивает свое состояние на единицу. Поскольку третий триггер 12 находится теперь в нулевом состоянии, то режим третьего регистра 15 определяется сигналом на втором входе 23 задания режима устройства. При отсутствии сигнала на нем и, следовательно, на выходе элемента ИЛИ 11 третий регистр 15 находится в режиме записи информации, поступающей с выходов накопителя 2, а при наличии сигнала в режиме обнуления. Причем запись производится по положительному перепаду.

7,1

Спрдующий цикл записи начинается при поступлении очередного импульса на вход 20 записи. Причем процесс записи информации в каждую ячейку накопителя 2 и изменения состояния пер вого счетчика 9 аналогичны процессу в предыдущем цикле.

После поступления на вход синхронизации второго счетчика 10 числа им иу.чьсоп, соответствующего инверсному коду числа циклов, на его выходе пе- реиолиепия формируется отрицательный имиульс, свидетельствующий о выполне ШП1 заданного числа циклов записи в накопитель и поступающий на вход третьего элемента НЕ 18. На выходе данного злемеита формируется положи- тельныГ имиульс, устанавливающий первый триггер 4 в единичное состояние по входу установки в 1. Нри этом исчезает сигнал па инверсном выходе дапиого триггера и, следовательно, разрешается прохождение через коммутатор 13 импульсов с входа 21 считывания, производится блокировка третьего элемента И 8 по второму входу и установка второго регистра 3 в режим записи 1И формацип из пакопителя 2, а второго счетчика 10 - в режим записи кода числа циклов. Появление сигнала на прямом выходе первого триггера 4 приводит к появлению сигнала на ин- формациоштом входе второго триггера 6 и иа В1 1ходе первого злемента И 5, так как второй триггер 6 по-прежнему паходится в кулевом состоянии.

Таким образом, после.окончания за числа циклов записи устройство переходит в режим выдачи содержимого накопителя 2 на информационные выходы 26 через второй регистр 3, а па вьп.оде 25 запрета записи появляется сигиал. Первый счетчик 9 при этом находится в нулевом состоянии, а им- пульс 1 записи не могут переключить первы тригг ер 4, поскольку второй элемент И 7 закрыт по первому входу.

При появлении импульса считывания на входе 21 чтения на выходе коммутатора 13 также появляется импульс, по переднему фронту которого происходит запись во второй регистр 3 и, следовательно, появление на информационных выходах 26 устройства содержимог ячейки 1акопителя 2 с адресом, соответствующим состоянию первого счетчика 9. По окончании импульса считывания на выходе первого злемента НЕ

10

0

5

4093

8

16 формируется положительный перепад, по которому первый счетчик 9 увеличивает свое состояние на единицу, что приводит к изменению адреса ячейки накопителя 2. Сам накопитель находится в режиме считывания, так как третий элемент И 8 закрыт по второму входу. При поступлении следующего импульса считывания процесс появления содержимого ячейки накопителя 2 и последующего изменения состояния пер- BOFC счетчика 9 повторяется.

По окончании последовательной вы- г дачи на информационные выходы 26 со0

5

0

5

0

5

держимого всех ячеек накопителя 2 на выходе переполнения первого счетчика 9 вырабатывается отрицательный импульс. По положительному перепаду данного импульса второй триггер 6 устанавливается в единичное состояние, так как на его информационном входе сигнал имеется, а на выходе установки Б О отсутствует. При этом на прямом выходе данного триггера появляется сигнал, открывающий второй элемент И 7, а на инверсном выходе сигнал исчезает, что приводит к исчезновению сигнала на выходе 25 запрета записи.

После однократной выдачи всего содержимого накопителя 2 на информационные выходы 26 возможна либо повторная выдача при поступлении импульсов считывания, либо переключение устройства в режим записи (который бьш описан) при поступлении импульсов записи.

Устройство может работать в режиме преобразования заносимой в накопитель 1П1формации или же в режиме без преобразования. Управление режимом ос ществляется при помощи сигналов, подаваемых на первый 22 и второй 23 входы задания режима устройства. При подаче сигналов на оба входа на элемента 1-ШИ 1 1 независимо от состояния третьего триггера 12 имеется сигнал, и следовательно, третий регистр 15 находится в режиме обнуления, а сумматор-вычитатель 14 находится в режиме суммирования. При этом на выходах сумматора-вычитателя 14 и на информационных входах накопителя 2 будет информация, поступающая с выходов первого регистра 1. При отсутствии сигнала на втором входе 23 задания режима будет выполняться преобразование информации. Причем при наличии сигнала на первом входе 22

задании режима будет производиться .суммирование входной информации с содержимым накопителя 2, а при отсутг ствии - вычитание.

Формула изобретения

Буферное запоминающее устройство, содержащее коммутатор, первый и второй регистры, первый, второй и третий триггеры, накопитель, первый, второй и третий элементы И, первый и второй счетчики, элемент ИЛИ, информационные входы первого регистра являются информационными входами устройства, вход синхронизации первого регистра является входом записи устройства, выходы накопителя соединены с информационными входами второго регистра, выходы которого являются информационными выходами устройства, выход второго элемента И соединен с входом установки в О первого триггера, прямой выход которого соединен с первым входом первого элемента И,

инверсный выход первого триггера соединен с входом установки в

О

второго триггера, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения обработки входной- информации, в него введены сумматор- вычитатель, третий регистр, первый, второй и третий элементы НЕ, входы первой группы сумматора-вычитателя соединены с выходами третьего регистра, информационные входы которого соединены с выходами накопителя, входы второй группы сумматора-вычитателя соединены с выходами первого регистра, управляющий вход сумматора-вычитателя является первым входом задания режима устройства, выходы сумматора-вычитателя соединены с информационными входами накопителя, адресные входы которого соединены с выходами первого счетчика, первый информационный вход коммутатора соединен

0

5

0

5

0

5

с входом синхронизации первого региг стра и вторым входом второго элемента И, второй информационный вход коммутатора является входом чтения устройства, выход коммутатора соединен с входом первого элемента НЕ, входами сш«ронизации второго и третьего регистров и первым входом третьего элемента И, выход которого соединен с входом записи-чтетгя накопителя, вход синхронизации первого счетчика соединен с выходом первого элемента НЕ, вход начальной установки первого счетчика соединен с выходом второго элемента И и входом установки в 1 третьегб триггера, выход переполнения первого счетчика соединен с входом второго элемента НЕ и входом синхронизации второго триггера, прямой выход которого соединен с первым входом второго элемента И, инверсный выход второго триггера соединен с вторым входом первого элемента И, выход второго элемента НЕ соединен с входом синхронизации второго счетчика и входом установки в О третьего триггера, выход которого соединен с вторым входом элемента ИЛИ, первый вход которог О является вторым входом задания режима устройства, выход элемента ИЛИ соединен с входом установки в О третьего регистра, инверсный выход первого триггера соединен с управляющим входом коммутатора, вторым входом третьего элемента, И, входом установки в О второго регистра и входом задания режима второго счетчика, информационные входы которого являются входами задания числа циклов, выход переполнения второго счетчика соединен с входом третьего элемента НЕ, выход которого соединен с входом установки в 1 первого триггера, прямой выход которого соединен с информационным входом второго триггера, выход первого элемента И является выходом запрета записи устройства.

| Буферное запоминающее устройство | 1983 |

|

SU1176382A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226528A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-11-23—Публикация

1988-01-14—Подача