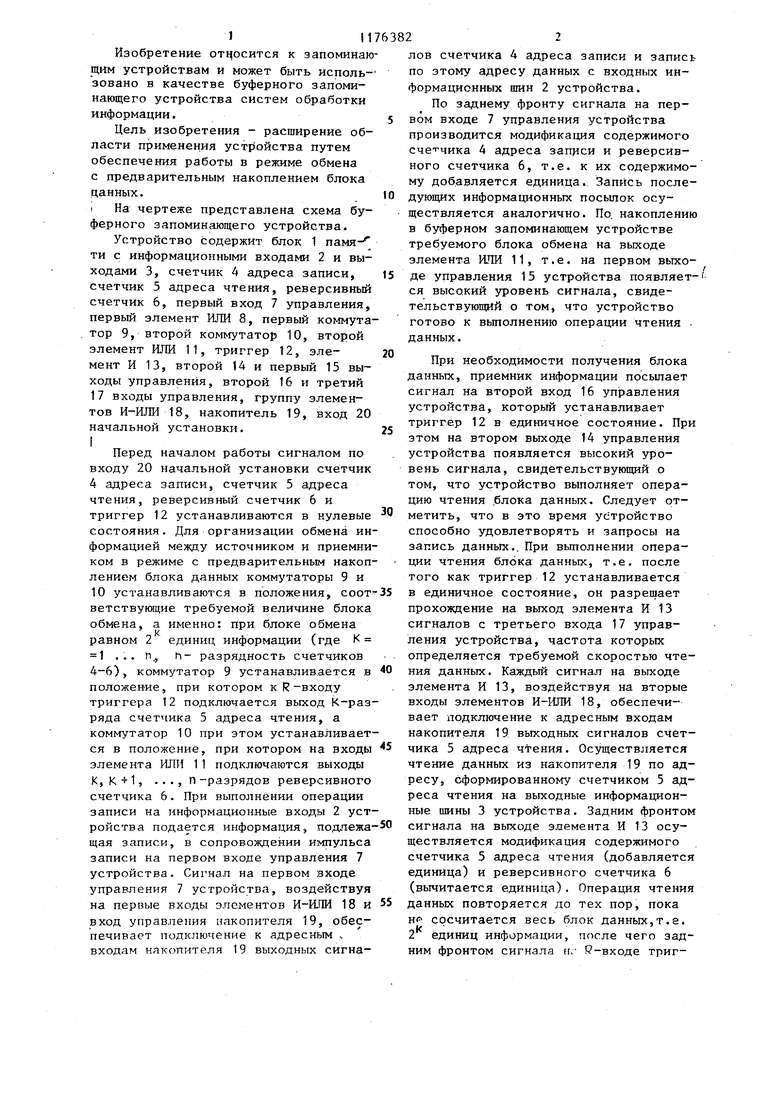

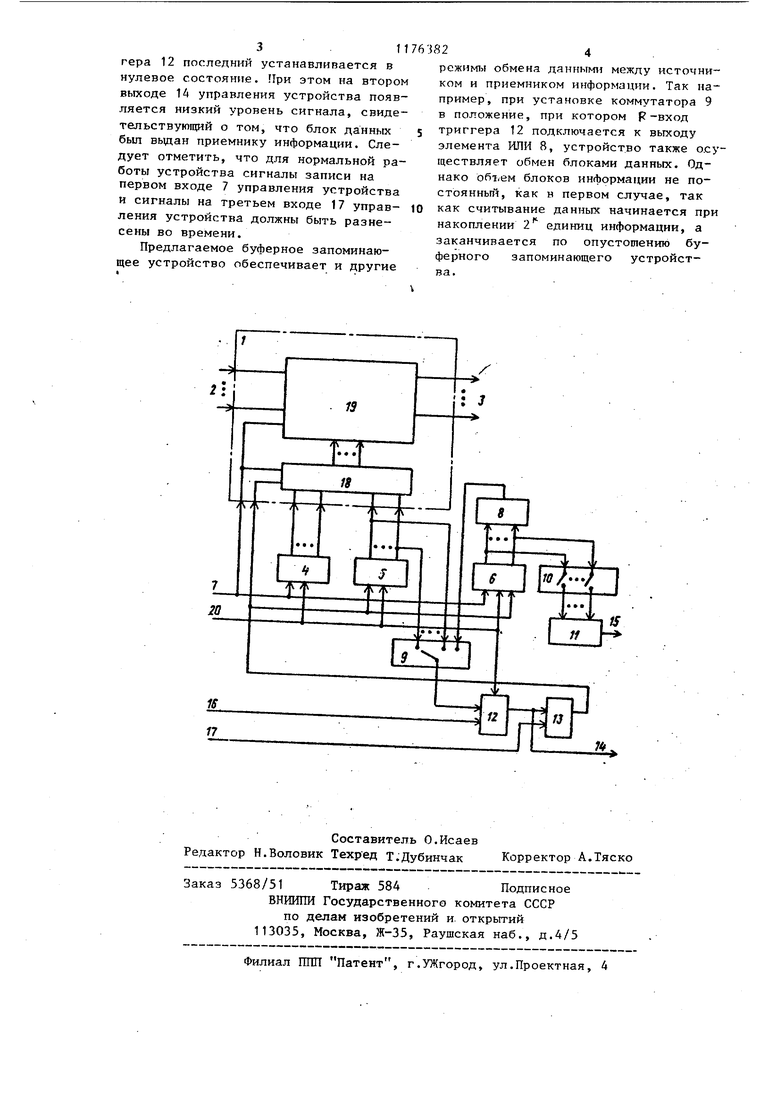

Изобретение отчосится к запоминаю щим устройствам и может быть использовано в качестве буферного запоминающего устройства систем обработки информации. Цель изобретения - расширение области применения устройства путем обеспечения работы в режиме обмена с предварительным накоплением блока данных. i На чертеже представлена схема буферного запоминающего устройства. Устройство содержит блок 1 памяти с информационными входами 2 и выходами 3, счетчик 4 адреса записи, счетчик 5 адреса чтения, реверсивный счетчик 6, первый вход 7 управления, первый элемент ИЛИ 8, первый коммута тор 9, второй коммутатор 10, второй элемент ИЛИ 11, триггер 12, элемент И 13, второй 14 и первый 15 выходы управления, второй 16 и третий 17 входы управления, группу элементов И-ИЛИ 18, накопитель 19, вход 20 начальной установки. Перед началом работы сигналом по входу 20 начальной установки счетчик 4 адреса записи, счетчик 5 адреса чтения, реверсивный счетчик 6 и триггер 12 устанавливаются в нулевые состояния. Для организации обмена ин формацией между источником и приемни ком в режиме с предварительным накоп лением блока данных коммутаторы 9 и 10 устанавливаются в положения, соот ветствующие требуемой величине блока обмена, а именно: при блоке обмена равном 2 единиц информации (где К 1 ... п., h- разрядность счетчиков 4-6), коммутатор 9 устанавливается в положен-ие, при котором к R-входу триггера 12 подключается выход К-раз ряда счетчика 5 адреса чтения, а коммутатор 10 при этом устанавливает ся в положение, при котором на входы элемента ИЛИ 11 подключаются выходы К, , ..., П-разрядов реверсивного счетчика 6. При выполнении операции записи на информационные входы 2 уст ройства подается информация, подлежа щая записи, в сопровождении ихчпульса записи на первом входе управления 7 устройства. Сигнал на первом входе управления 7 устройства, воздействуя на первые входы элементов И-И.ПИ 18 и вход управления накопителя 19, обеспечивает подключение к адресным . входам накопителя 19 выходных сигналов счетчика 4 адреса записи и запись по этому адресу данных с входных информационных шин 2 устройства. По заднему фронту сигнала на первом входе 7 управления устройства производится модификация содержимого счетчика 4 адреса записи и реверсивного счетчика 6, т.е. к их содержимому добавляется единица. Запись последуюирих информационных посьшок осуществляется аналогично. По. накоплению в буферном запоминающем устройстве требуемого блока обмена на выходе элемента ИЛИ 11, т.е. на первом выходе уцравления 15 устройства появляется высокий уровень сигнала, свидетельствующий о том, что устройство готово к выполнению операции чтения данных. При необходимости получения блока данных, приемник информации посылает сигнал на второй вход 16 управления устройства, который устанавливает триггер 12 в единичное состояние. При этом на втором выходе 14 управления устройства появляется высокий уровень сигнала, свидетельствующий о том, что устройство выполняет операцию чтения блока данных. Следует отметить, что в это время устройство способно удовлетворять и запросы на запись данных.. При вьтолнении операции чтения блока данных, т.е. после того как триггер 12 устанавливается в единичное состояние, он разрешает прохождение на выход элемента И 13 сигналов с третьего входа 17 управления устройства, частота которых определяется требуемой скоростью чтения данньпс. Каждый сигнал на выходе элемента И 13, воздействуя на вторые входы элементов И-ИЛИ 18, обеспечивает подключение к адресным входам накопителя 19 выходных сигналов счетчика 5 адреса чтения. Осуществляется чтение данных из накопителя 19 по адресу, сформированному счетчиком 5 адреса чтения на выходные информационные шины 3 устройства. Задним фронтом сигнала на выходе элемента И 13 осуществляется модификация содержимого счетчика 5 адреса чтения (добавляется единица) и реверсивного счетчика 6 (вычитается единица). Операция чтения данных повторяется до тех пор, пока HP сосчитается весь блок данных,т.е. 2 единиц информации, после чего задним фронтом сигнала кг Р-входе триг311гера 12 последний устанавливается в нулевое состояние. При этом на втором выходе 14 управления устройства появляется низкий уровень сигнала, свидетельствующий о том, что блок данных был вьщан приемнику информации. Следует отметить, что для нормальной работы устройства сигналы записи на первом входе 7 управления устройства и сигналы на третьем входе 17 управления устройства должны быть разнесены во времени. Предлагаемое буферное запоминающее устройство обеспечивает и другие 24 рсжим1 обмена данршми между источником и приемником информации. Так например, при установке коммутатора 9 в положение, при котором Р-вход триггера 12 подключается к выходу элемента ИЛИ 8, устройство также осуществляет обмен блоками данных. Однако объем блоков информации не постоянньпЧ, как в первом случае, так как считывание данных начинается при накоплении 2 единиц информации, а заканчивается по опустошению буферного запоминающего устройст

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

БУФЕРНОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее блок памяти, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, адресные входы первой и второй группы блока памяти соединены соответственно с выходами счетчика адреса записи и счетчика адреса чтения, первый вход управления блока памяти подключен к счетному входу счетчика адреса записи, входу прямого счета реверсивного счетчика и является первым входом управления устройства, второй вход управления блока памяти соединен с счетным входом счетчика адреса чтения и входом обратного счета реверсивного счетчика, выходь которого подключе1а1 к входам первого злемента ИЛИ, а вход начальной установки соединен с соответствующими входами счетчика адреса записи, счетчика адреса чтения и является входом начальной установки устройства, о т л и чающее с.я тем, что, с целью расширения области применения устройства путем обеспечения работы в режиме с предварительным накоплением блока Данных, в него введены первый и второй коммутаторы, второй злемент ИЛИ, триггер и элемент И,-причем соответствующие входы первого коммутатора подключены к выходам счетчика адреса чтения и выходу первого злемента ИЛИ, а выход первого коммутатора соединен с R-входом триггера, Б-ВХОД которого является вторым вхо(Л дом управления устройства, вход наС чальной установки соединен с соответствующим входом устройства, а выход подключен к первому входу злемента И и является вторым выходом управления устройства, второй вход элемента И является третьим входом управлений устройства, а выход соединен со вторым входом управления блока памяти, входы второго коммутатора подключены к выходам реверсивного счетчика, а выходы соединены с входами второго злемента ИЛИ, выход которого является первым выходом управления устройства.

| Буферное запоминающее устройство | 1979 |

|

SU822293A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1979 |

|

SU809358A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-08-30—Публикация

1983-06-10—Подача