Изобретение относится к запоми- .нающим устройствам и может быть .использовано в системах сбора и передачи информации автоматизированных систем управления различными технологическими процессами.

Цель изобретения - повышение надежности устройства.

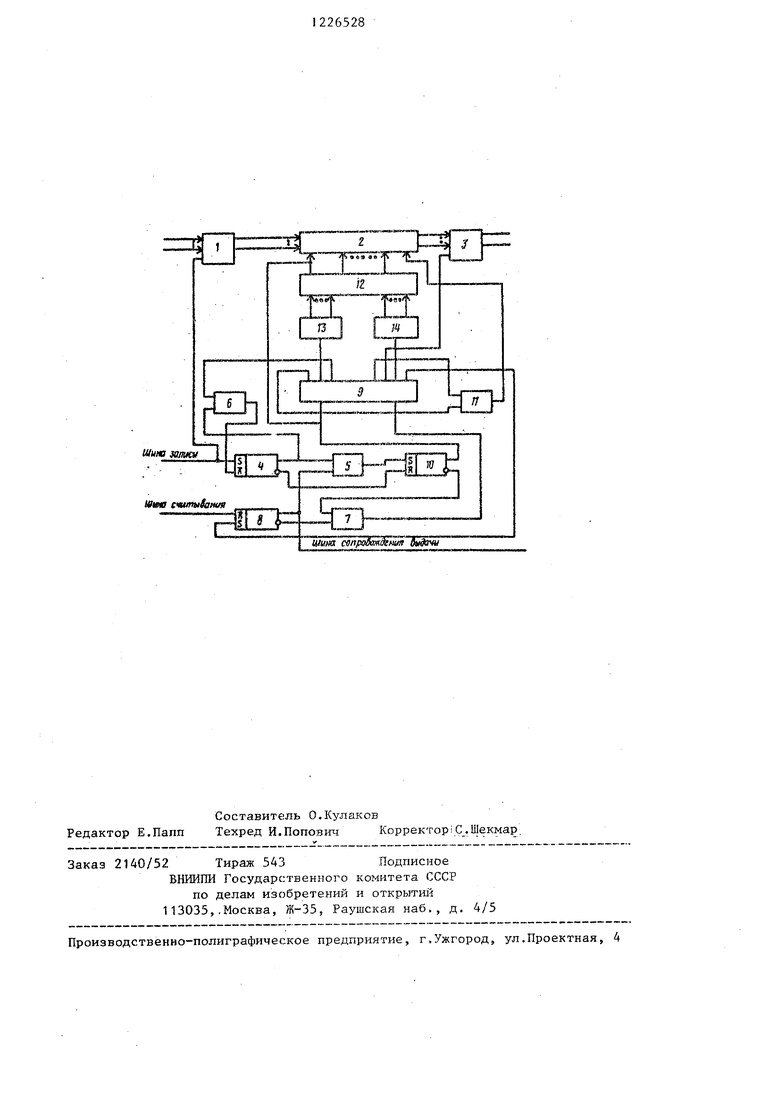

На чертеже представлена функциональная схема буферного запоминающего устройства.

Устройство содержит первый регистр 1, накопитель 2, второй регистр 3, первый RS-триггер 4, первый 5, второй 6, третий 7 элементы И, третий RS-триггер 8, многофазный генератор .9 одиночных импульсов, вто рой RS-триггер 10, элемент ИЛИ Л, коммутатор 12, первый счетчик 13, второй счетчик 14.

Устройство работает следуюищм образом.

В исходном состоянии счетчики адресов записи 13 и считывания 14, а также RS-триггеры 4 и 10 обнулены, а RS-триггер 8. находится в единичном состоянии. Накопитель 2 находится в режиме считывания.

При появлении импульса записи осуществляется запись входной информации во входной регистр 1 и взведение по В-входу RS-триггера 4 в единичное состояние. Так как RS-триггер 8 находится в единичном состоянии, то через первый элемент И 5 сигнал готовности к записи поступает на 8-вход RS-триггера 10 и взводит его, что приводит к переключению накопителя 2 из режима считывания в режим записи, переключению коммутатора 12 в режим коммутации адреса выходного кода счетчика 13 адреса записи на адресные входы накопителя 2 и к запуску многофазного генератора 9 одиночных, импульсов в режиме формирования тактовых импульсов записи,, которые появляются последовательно на первом, втором и третьем выходах для тактирования цикла записи очередного информационного слова из входного регистра 1 в накопитель 2. По первому тактовому импульсу осуществляется запись информации из входного регистра 1 в накопитель 2. По второму импульсу, поступающему q второго выхода многофазного генератора 9 одиноч- ньос импульсов, осуществляется наращи-- вание адреса записи на единицу.. Появление импульса на третьем выходе

12265282

многофазного генератора 9 одиночных 1-шпульсов приводит к наличию высоких уровней на обоих входах второго элемента И 6 и как результат - к обнулению RS TpHrrepa 4 по R-ЕХоду. При. этом появление высокого уровня сигнала на его инверсном выходе приводит к сбросу в нулевое состояние RS-триггера 10, а это переключает накопитель 2 в режим считывания, коммутатор 12 в режим коммутации выходов счетчика 14 адреса считывания на адресные входы накопителя 2 и выключению режима фор(ирования. тактовых импульсов t5 .цикла записи многофазного генератора 9 одиночных импульсов.

10

35

Появление импульса считывания на Е:-входе RS-триггера 8 перебрасывает

20 его в нулевое состояние, запрещая тем самым включение, режима записи до тех пор, пока не закончится цикл считывания информации из накопителя 2 в выходной регистр 3. При этом на

25 инверсном выходе RS-триггера В появляется единичный сигнал, который ввиду наличия единичного уровня на инверсном выходе RS-триггера 10 поступает через третий элемент И 7 на

30 второй управляющий вход многофазного генератора 9 одиночных импульсов, по которому разрешается формирование импульсов, тактирующих цикл считывания информации из накопителя 2 в выходной регистр 3. При этом в начале появляется импульс на четвертом выходе многофазного генератора 9 одиночных импульсов, поступающий через элемент ИЛИ 11 на второй управляющий вход накопителя 2. По этому импульсу осуществляется считывание информации из нулевой ячейки памяти накопителя 2. Затем при появлении импульса на П.ЯТОМ выходе многофазного генератора 9 одиночных импульсов осуществляется перезапись информации на выходе накопителя 2 в выходной регистр 3. Появление импульса на шестом выходе многофазного генератора 9 одиночных импульсов приводит к наращиванию адреса считывания на единицу, а последний импульс по S-входу взводит RS-триггер 8 в единичное состояние, что приводит к появлению сигнала сопровояадения вьщачи, выключению

55 многофазного генератора 9 одиночных импульсов и разрешению включения режима записи Н4 втором входе первого элемента И 5.

40

45

50

5

Появление импульса считывания на Е:-входе RS-триггера 8 перебрасывает

0 его в нулевое состояние, запрещая тем самым включение, режима записи до тех пор, пока не закончится цикл считывания информации из накопителя 2 в выходной регистр 3. При этом на

5 инверсном выходе RS-триггера В появляется единичный сигнал, который ввиду наличия единичного уровня на инверсном выходе RS-триггера 10 поступает через третий элемент И 7 на

0 второй управляющий вход многофазного генератора 9 одиночных импульсов, по которому разрешается формирование импульсов, тактирующих цикл считывания информации из накопителя 2 в выходной регистр 3. При этом в начале появляется импульс на четвертом выходе многофазного генератора 9 одиночных импульсов, поступающий через элемент ИЛИ 11 на второй управляющий вход накопителя 2. По этому импульсу осуществляется считывание информации из нулевой ячейки памяти накопителя 2. Затем при появлении импульса на П.ЯТОМ выходе многофазного генератора 9 одиночных импульсов осуществляется перезапись информации на выходе накопителя 2 в выходной регистр 3. Появление импульса на шестом выходе многофазного генератора 9 одиночных импульсов приводит к наращиванию адреса считывания на единицу, а последний импульс по S-входу взводит RS-триггер 8 в единичное состояние, что приводит к появлению сигнала сопровояадения вьщачи, выключению

5 многофазного генератора 9 одиночных импульсов и разрешению включения режима записи Н4 втором входе первого элемента И 5.

0

5

0

Б том случае, если импульс записи приходит во время, когда еще не закончен цикл считывания, по второму входу первого элемента И 5 блокируется включение режима записи RS-триг- гера 10.

Аналогично в случае .прихода импульса считывания во время, когда еще не закончен цикл записи в накопитель 2, осуществляется блокировка включения режима считывания по первому входу третьего элемента И 7 до момента окончания цикла записи.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель,, первый и второй регистры, первый и второй счетчики, первый, второй и третий триггеры, элементы И, причем информационные входы первого регистра являются информационными входами устройства, выходы первого регистра подключены к информационным входам накопителя, выходы которого соединены с информационными входами второго регистра, выходы которого являются информационными выходами устройства, первые входы первого и третьего триг геров являются управляющими входами устройства, отличающееся тем, что, с целью поныйения надежности устройства, в него введены многофазный генератор одиночных импульсов, коммутатор, элемент ИЛИ, причем первый вход первого триггера

10

15

20

25

30

35

соединен с управляющим входом первого регистра, инверсный выход первого триггера подключен к одному Ъходу второго триггера, другой вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым выхрдом первого трип е- ра и первым входом второго элемента

(И, выход которого подключен к второму вх оду первого триггера, прямой выход

второго триггера соединен с управляющим входом коммутатора и первыми управляющими входами накопителя и многофазного генератора одиночных импульсов, второй управляющий вход которого подключен к выходу третьего элемента И, первьш вход которого соединен с инверсным выходом второго триггера, а второй вход - с инверсным выходом третьего триггера, прямой выход которого подключен к второму входу первого элемента И и является контрольным выходом устройства, выходы многофазного генератора одиночных импульсов соединены соответственно с первым входом элемента ИЛИ, входом первого счетчика, вторым входом второго элемента И, вторым входом элемента ИЛИ, управляющим входом второго регистра, входом второго счетчика, вторым входом третьего триггера, выход элемента ИЛИ подключен к второму управляющему входу накопителя, адресные входы которого соединены с выходами коммутатора, входы первой и второй группы которого соединены соответственно с выходами первого и второго счетчиков.

4

lHuia затки

1вша cvumiSanta

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1524093A1 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для управления сортировкой штучных изделий | 1982 |

|

SU1375535A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам, и может быть использовано в системах сбора и передачи информации автоматизированных систем управления различными технологическими процессами. Цель изобретения состоит в повьшении надежности устройства. Устройство содержит регистры, накопитель, триггеры, элементы И, многофазньй генератор одиночных импульсов, элемент ИЛИ, коммутатор, счетчики. Устройство позволяет осуществлять блокировку режима считывания во время цикла записи и наоборот. 1 ил. с S

| Катодная лампа с внешним подогревом | 1923 |

|

SU493A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-02—Подача