1

(21)4461403/24-24

(22)06.06.88

(46) 07.03.90. Бюл. № 9

(72) Н.Н. Новиков, А.Р. Каплан

и Х.М. Рухая

(53) 681.325(088.8)

(56) Селлерс Ф. Методы обнаружения

ошибок в работе ЭЦВМ - М.: Мир, 1972,

с. 224, фиг. 12.2.а.

Кузьмин, Бурназан Р.Г., Ковер- гин А.А. Аппаратный контроль ЭЦВМ - М.: Энергия, 1974, с. 14, рис. 1.

Авторское свидетельство СССР № 1015385, кл. G 06 F 11/00, 1981.

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧЕТЧИКОВ

(57) Изобретение относится к вычислительной технике и может быть использовано для периодического контроля счетчиков импульсов, которые функционируют в разные моменты времени. Целью изобретения является повышение достоверности контроля. Цель достигается за счет переключения устройства с двухканального режима работы на од- ноканальный, последовательного опроса парафазных выходов первого и второго счетчиков и контроля записанной в них

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Преобразователь код-временной интервал | 1979 |

|

SU822348A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1211725A1 |

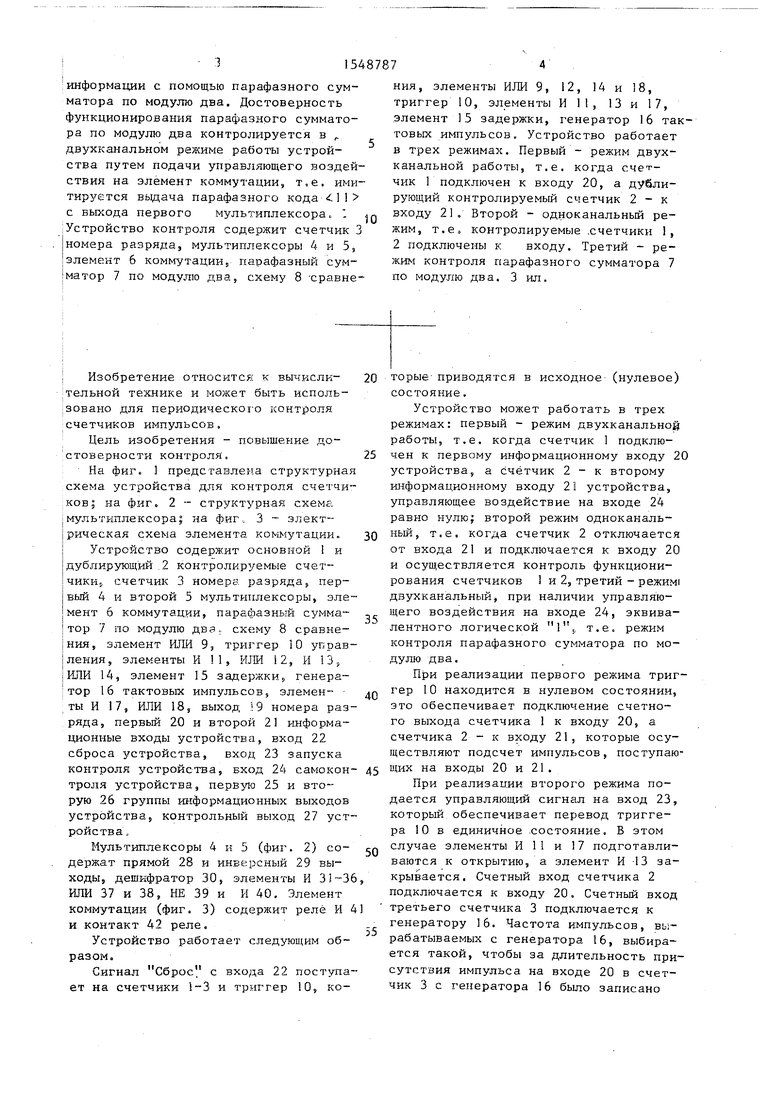

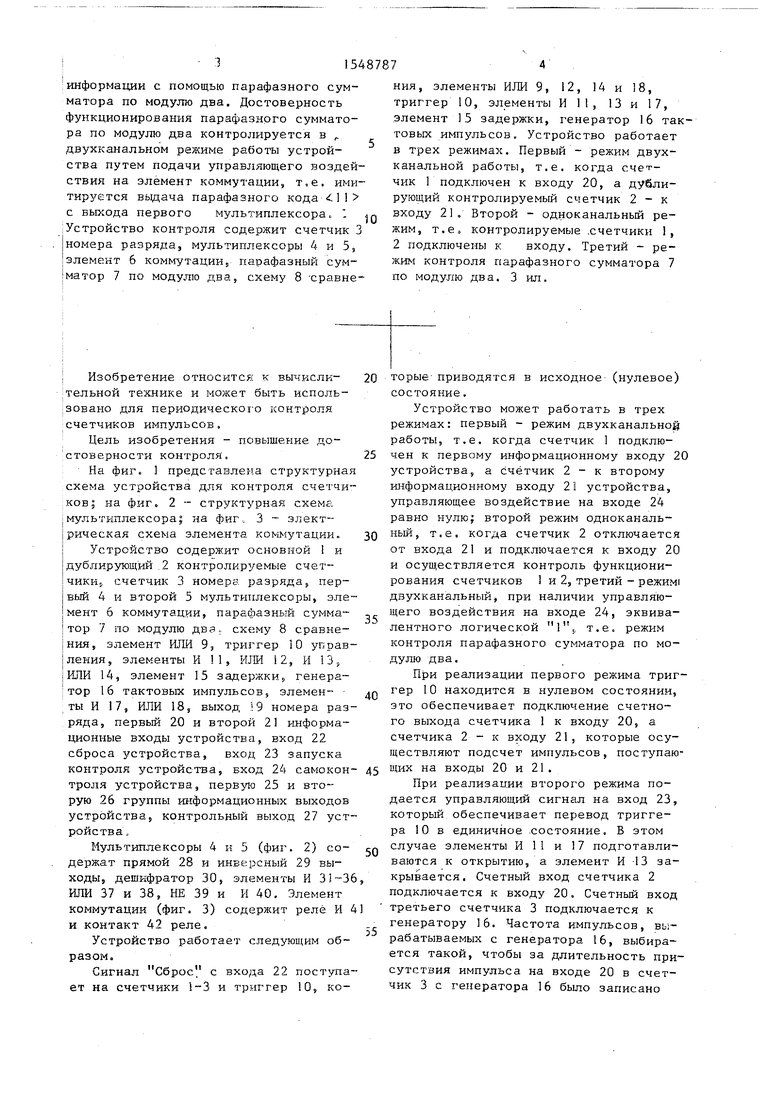

Изобретение относится к вычислительной технике и может быть использовано для периодического контроля счетчиков импульсов, которые функционируют в разные моменты времени. Целью изобретения является повышение достоверности контроля. Цель достигается за счет переключения устройства с двухканального режима работы на одноканальный, последовательного опроса парафазных выходов первого и второго счетчиков и контроля записанной в них информации с помощью парафазного сумматора по модулю два. Достоверность функционирования парафазного сумматора по модулю два контролируется в двухканальном режиме работы устройства путем подачи управляющего воздействия на элемент коммутации, т.е. имитируется выдача парафазного кода *9811*98 с выхода первого мультиплексора. Устройство контроля содержит счетчик 3 номера разряда, мультиплексоры 4, 5, элемент 6 коммутации, парафазный сумматор 7 по модулю два, схему 8 сравнения, элементы ИЛИ 9, 12, 14, 18, триггер 10, элементы И 11, 13, 17, элемент 15 задержки, генератор 16 тактовых импульсов. Устройство работает в трех режимах. Первый - режим двухканальной работы, т.е. когда счетчик 1 подключен к входу 20, а дублирующий контролируемый счетчик 2 - к входу 21. Второй - одноканальный режим, т.е. контролируемые счетчики 1, 2 подключены к входу. Третий - режим контроля парафазного сумматора 7 по модулю два. 3 ил.

Пере- стр.

-Л- го

Фиг.1

g

СП

4ь

(X) 1 00 J

информации с помощью парафаэного сумматора по модулю два. Достоверность Функционирования парафазного сумматора по модулю два контролируется в двухканальном режиме работы устройства путем подачи управляющего воздействия на элемент коммутации, т.е. имитируется выдача парафазного кода 1 с выхода первого мультиплексора, 1 Устройство контроля содержит счетчик 3 номера разряда, мультиплексоры 4 и 5, элемент 6 коммутации, парафазный сумматор 7 по модулю два, схему 8 сравнеИзобретение относите к вычисли- тельной технике и может быть использовано для периодическою контроля счетчиков импульсов.

Цель изобретения - повышение достоверности контроля.

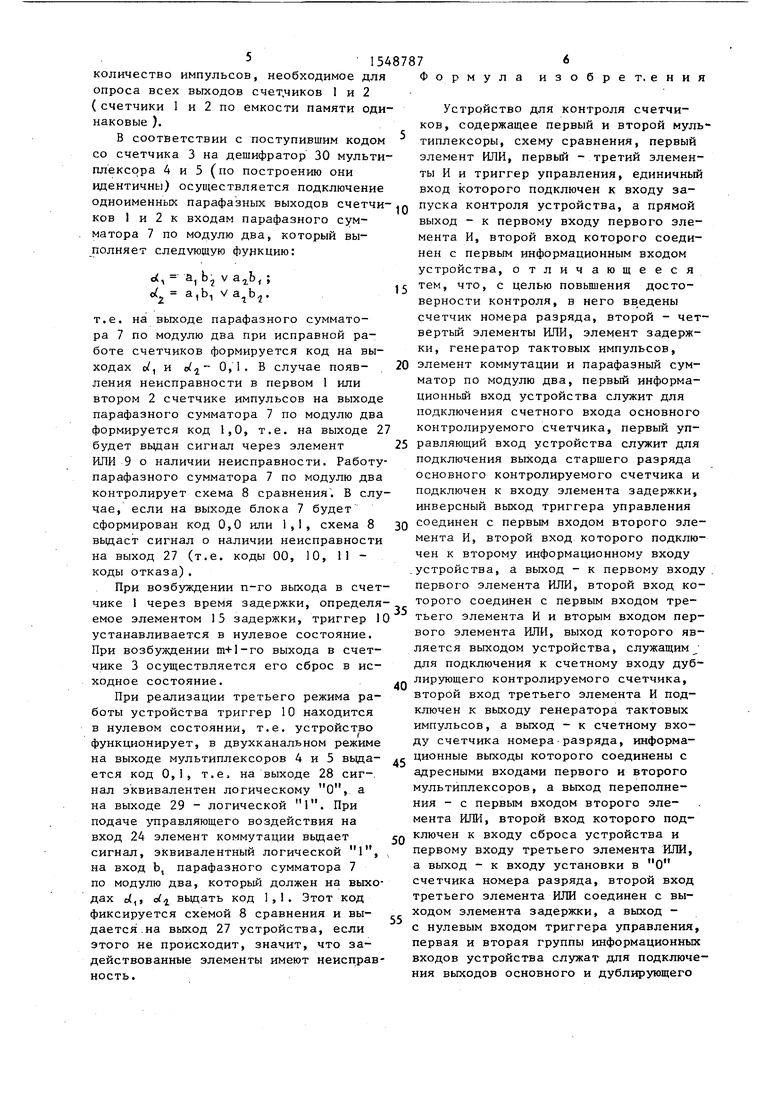

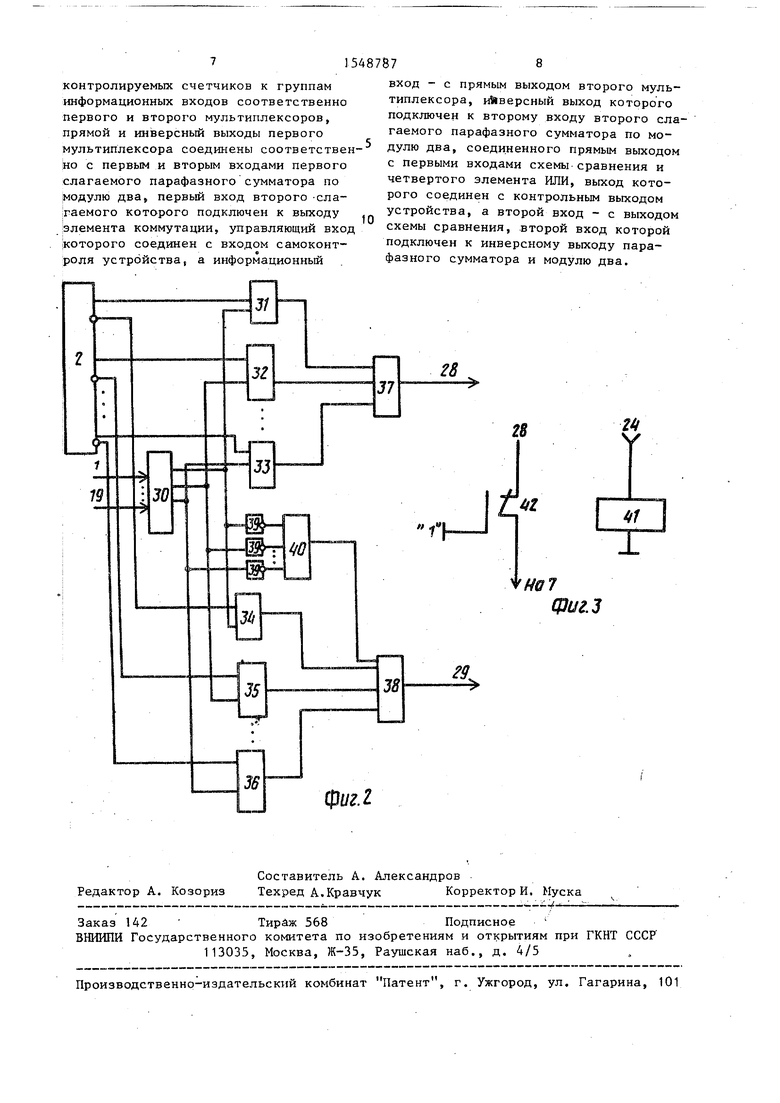

На фиг. 1 представлена структурная схема устройства для контроля счетчиков; на фиг. 2 - структурная схеме мультиплексора; на фиг 3 - электрическая схема элемента коммутации.

Устройство содержит основной 1 и дублирующий 2 контролируемые счетчику счетчик 3 номере разряда,, первый 4 и второй 5 мультиплексоры, элемент 6 коммутации, парафазный сумма- тор 7 по модулю двл, схему 8 сравнения, элемент ИЛИ 93 триггер 10 управления , элементы И 1 1, ИЛИ 12, И 1 3 s ИЛИ 14, элемент 15 задержки,, генератор 16 тактовых импульсов, элемен-- ты И 7, ИЛИ 18, выход 9 номера разряда, первый 20 и второй 21 информационные входы устройства, вход 22 сброса устройства, вход 23 запуска контроля устройства, вход 24 самокон- троля устройства, первую 25 и вторую 26 группы информационных выходов устройства, контрольный выход 27 устройства.

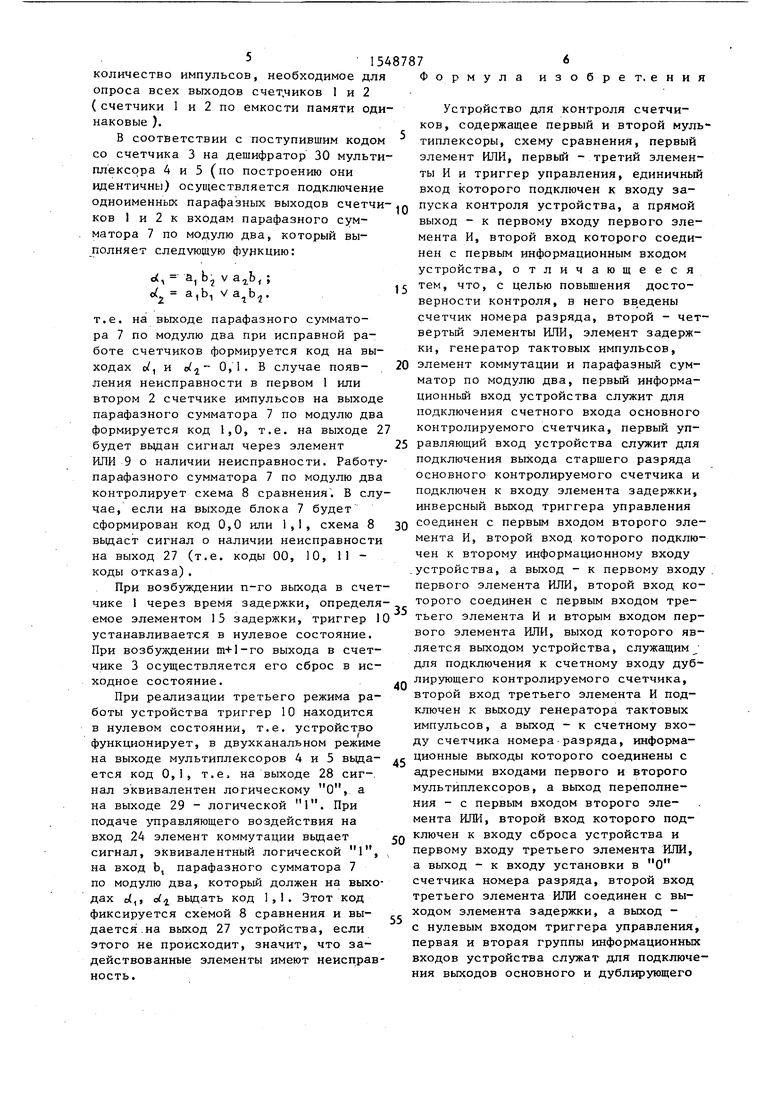

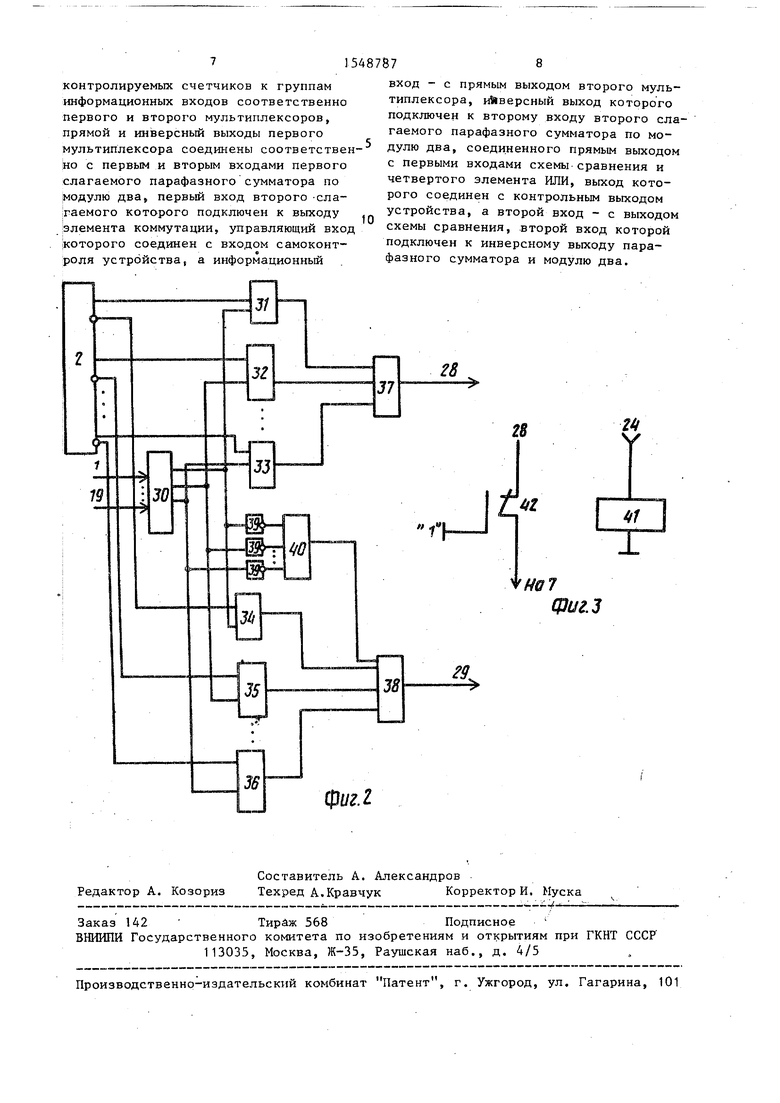

Мультиплексоры 4 и 5 (фиг. 2) со- держат прямой 28 и инверсный 29 выходы, дешифратор 30, элементы И 31-36 ИЛИ 37 и 38 НЕ 39 и И 40. Элемент коммутации (фиг. 3) содержит реле И 4 и контакт 42 реле.

Устройство работает следующим образом.

Сигнал Сброс с входа 22 поступает на счетчики 3 и триггер 10, ко

ния, элементы ИЛИ 9, 12, 14 и 18, триггер 10, элементы И 11, 13 и 17, элемент 15 задержки, генератор 16 татовых импульсов. Устройство работает в трех режимах. Первый - режим двух- канальной работы, т.е. когда счетчик 1 подключен к входу 20, а дублирующий контролируемый счетчик 2 - к входу 21. Второй - одноканальный режим, т.е контролируемые счетчики 1, 2 подключены у входу. Третий - режим контроля парафазного сумматора 7 по модулю дв а. 3 ил.

„ 5

о

5

торые приводятся в исходное (нулевое) состояние.

Устройство может работать в трех режимах: первый - режим двухканальной работы, т.е. когда счетчик 1 подключен к первому информационному входу 20 устройства, а счетчик 2 - к второму информационному входу 21 устройства, управляющее воздействие на входе 24 равно нулю; второй режим одноканальный, т.е. когда счетчик 2 отключается от входа 21 и подключается к входу 20 и осуществляется контроль функционирования счетчиков 1 и 2, третий - режим: двухканальный, при наличии управляющего воздействия на входе 24, эквивалентного логической 1, т.е. режим контроля парафазного сумматора по модулю два.

При реализации первого режима триггер 10 находится в нулевом состоянии, это обеспечивает подключение счетного выхода счетчика 1 к входу 20, а счетчика 2 - к входу 21, которые осуществляют подсчет импульсов, поступающих на входы 20 и 21.

При реализации второго режима подается управляющий сигнал на вход 23, который обеспечивает перевод триггера 1 0 в единичное состояние. В этом случае элементы И 11 и 17 подготавливаются к открытию, а элемент И 13 закрывается. Счетный вход счетчика 2 подключается к входу 20. Счетный вход третьего счетчика 3 подключается к генератору 16. Частота импульсов, вырабатываемых с генератора 16, выбирается такой, чтобы за длительность присутствия импульса на входе 20 в счетчик 3 с генератора 16 было записано

количество импульсов, необходимое для опроса всех выходов счет.чиков 1 и 2 ( счетчики 1 и 2 по емкости памяти одинаковые ).

В соответствии с поступившим кодом со счетчика 3 на дешифратор 30 мультиплексора 4 и 5 (по построению они идентичны) осуществляется подключение одноименных парафазных выходов счетчиков 1 и 2 к входам парафазного сумматора 7 по модулю два, который выполняет следующую функцию:

v a

о(, a, L

z а,Ц va7br

ги1

т.е.

на выходе парафазного сумматора 7 по модулю два при исправной работе счетчиков формируется код на выходах с/, и ,. В случае появления неисправности в первом 1 или втором 2 счетчике импульсов на выходе парафазного сумматора 7 по модулю два формируется код 1,0, т.е. на выходе 2 будет выдан сигнал через элемент

ИЛИ 9 о наличии неисправности. Работу парафазного сумматора 7 по модулю два контролирует схема 8 сравнения. В случае, если на выходе блока 7 будет сформирован код 0,0 или 1,1, схема 8 выдаст сигнал о наличии неисправности на выход 27 (т.е. коды 00, 10, 11 - коды отказа).

При возбуждении n-го выхода в счетчике 1 через время задержки, определяемое элементом 15 задержки, триггер 1 устанавливается в нулевое состояние. При возбуждении m+1-ro выхода в счетчике 3 осуществляется его сброс в исходное состояние.

При реализации третьего режима работы устройства триггер 10 находится в нулевом состоянии, т.е. устройство функционирует, в двухканальном режиме на выходе мультиплексоров 4 и 5 выдается код 0,1, т.е на выходе 28 сигнал эквивалентен логическому О, а на выходе 29 - логической 1. При подаче управляющего воздействия на вход 24 элемент коммутации выдает сигнал, эквивалентный логической 1, на вход Ь, парафазного сумматора 7 по модулю два, который должен на выходах о(,, о(4 выдать код 1,1. Этот код фиксируется схемой 8 сравнения и выдается на выход 27 устройства, если этого не происходит, значит, что задействованные элементы имеют неисправность.

ормула

6

зоб

ре т. е н и я

0

Устройство для контроля счетчиков, содержащее первый и второй мультиплексоры, схему сравнения, первый элемент ИЛИ, первый - третий элементы И и триггер управления, единичный вход которого подключен к входу запуска контроля устройства, а прямой выход - к первому входу первого элемента И, второй вход которого соединен с первым информационным входом устройства, отличающееся тем, что, с целью повышения достоверности контроля, в него введены счетчик номера разряда, второй - четвертый элементы ИЛИ, элемент задержки, генератор тактовых импульсов, элемент коммутации и парафазный сумматор по модулю два, первый информационный вход устройства служит для подключения счетного входа основного контролируемого счетчика, первый уп- 5 равляющий вход устройства служит для

5

0

5

0

0

5

0

5

подключения выхода старшего разряда основного контролируемого счетчика и подключен к входу элемента задержки, инверсный выход триггера управления соединен с первым входом второго элемента И, второй вход которого подключен к второму информационному входу устройства, а выход - к первому входу первого элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента И и вторым входом первого элемента ИЛИ, выход которого является выходом устройства, служащим для подключения к счетному входу дублирующего контролируемого счетчика, второй вход третьего элемента И подключен к выходу генератора тактовых импульсов, а выход - к счетному входу счетчика номера разряда, информационные выходы которого соединены с адресными входами первого и второго мультиплексоров, а выход переполнения - с первым входом второго элемента ИЛИ, второй вход которого подключен к входу сброса устройства и первому входу третьего элемента ИЛИ, а выход - к входу установки в О счетчика номера разряда, второй вход третьего элемента ИЛИ соединен с выходом элемента задержки, а выход - с нулевым входом триггера управления, первая и вторая группы информационных входов устройства служат для подключения выходов основного и дублирующего

контролируемых счетчиков к группам информационных входов соответственно первого и второго мультиплексоров, прямой и инверсный выходы первого мультиплексора соединены соответствен но с первым и вторым входами первого слагаемого парафазного сумматора по модулю два, первый вход второго -слагаемого которого подключен к выходу элемента коммутации, управляющий вход которого соединен с входом самоконтроля устройства, а информационный

зг

79

30

W

J//

35

вход - с прямым выходом второго мультиплексора, ийверсный выход которого подключен к второму входу второго слагаемого парафазного сумматора по модулю два, соединенного прямым выходом с первыми входами схемы сравнения и четвертого элемента ИЛИ, выход которого соединен с контрольным выходом устройства, а второй вход - с выходом схемы сравнения, второй вход которой подключен к инверсному выходу пара- фазного сумматора и модулю два.

37

28

28

V

-J

и

LJL

1

VHQ7

Фиг.З

38

га.

Авторы

Даты

1990-03-07—Публикация

1988-06-06—Подача