фиг. f

счет введения блока 5 постоянной памяти, коммутатора 2, блока 9 элементов ИЛИ и их функциональных связей с элементами устройства. В устройстве иэ входной выборки формируются дсмодулированные квадратурные составляющие в соответствии с выражениями. После фильтрации разностной составляющей и соответствии с

заданным выражением производятся перенос в исходнуйГ полосу частот путем домножения на соответствующие множители и их суммирование. Многоканальный фильтр позволяет оперативно перестраивать полосу чаьтот пропускания фильтра по М-каналам. Приведено выполнение блока синхронизации на логических элементах. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов | 1987 |

|

SU1525716A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| СПОСОБ МНОГОКАНАЛЬНОГО АДАПТИВНОГО ПРИЕМА РАДИОСИГНАЛОВ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2011 |

|

RU2477551C1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

Изобретение относится к радиотехнике и может быть использовано для цифровой обработки сигналов. Целью изобретения является повышение быстродействия. Многоканальный перестраиваемый фильтр содержит блок 1 оперативной памяти, коммутатор 2, накапливающие сумматоры 4 и 8, блоки 5 и 6 постоянной памяти, счетчик 7 каналов, блок 9 элементов ИЛИ, сумматор 10, счетчики 11 и 12, блок 13 синхронизации. Устройство реализует Q-канальный M-каскадный цифровой фильтр с бесконечной импульсной характеристикой (БИХ-фильтр). Повышение быстродействия достигается за счет введения блока 5 постоянной памяти, коммутатора 2, блока 9 элементов ИЛИ и их функциональных связей с элементами устройства. В устройстве из входной выборки формируются демодулированные квадратурные составляющие в соответствии с выражениями. После фильтрации разностной составляющей в соответствии с заданным выражением производятся перенос в исходную полосу частот путем домножения на соответствующие множители и их суммирование. Многоканальный фильтр позволяет оперативно перестраивать полосу частот пропускания фильтра по M-каналам. Приведено выполнение блока синхронизации на логических элементах. 3 ил.

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано для цифровой обработки сигналов.

Цель изобретения - повышение быстродействия.

Кроме того, предложенный многоканальный перестраиваемый цифровой фильтр позволяет перестраивать полосу частот пропускания фильтра.

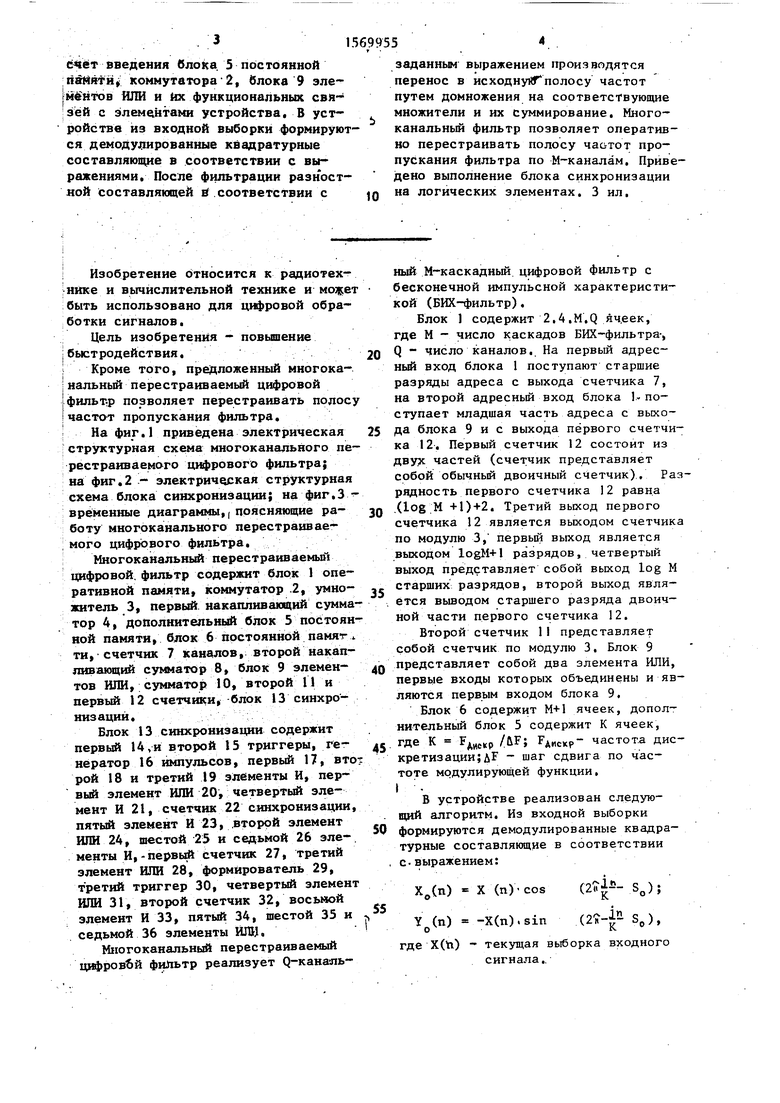

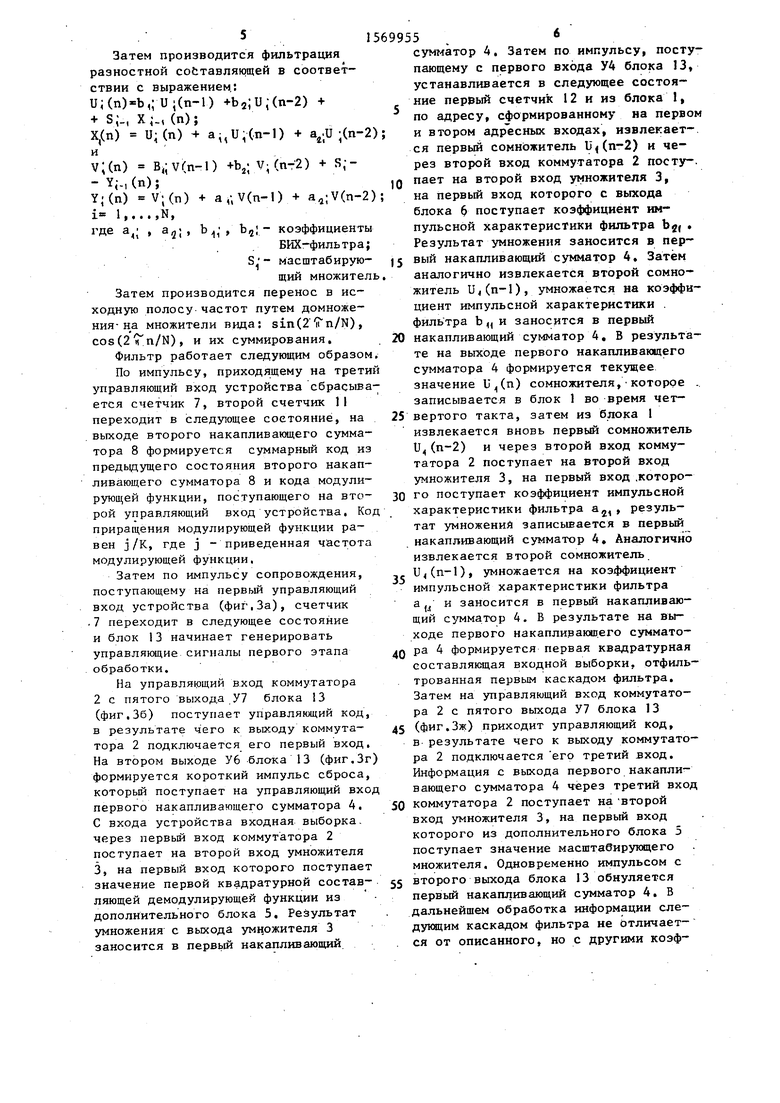

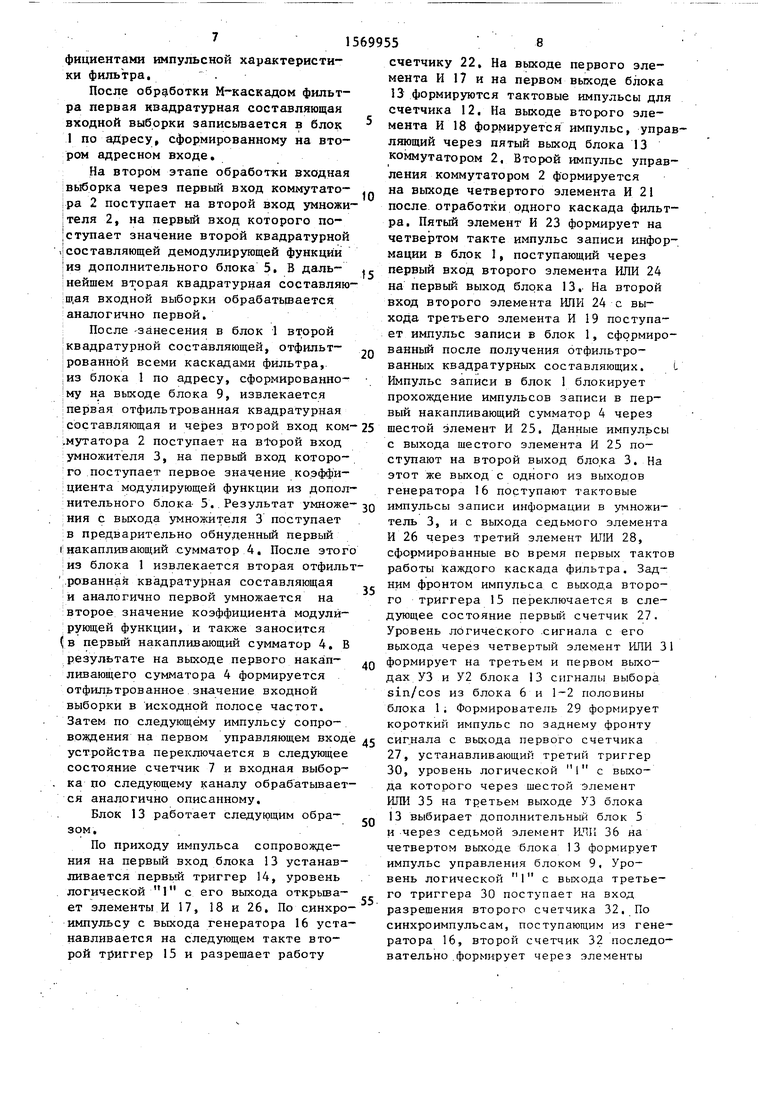

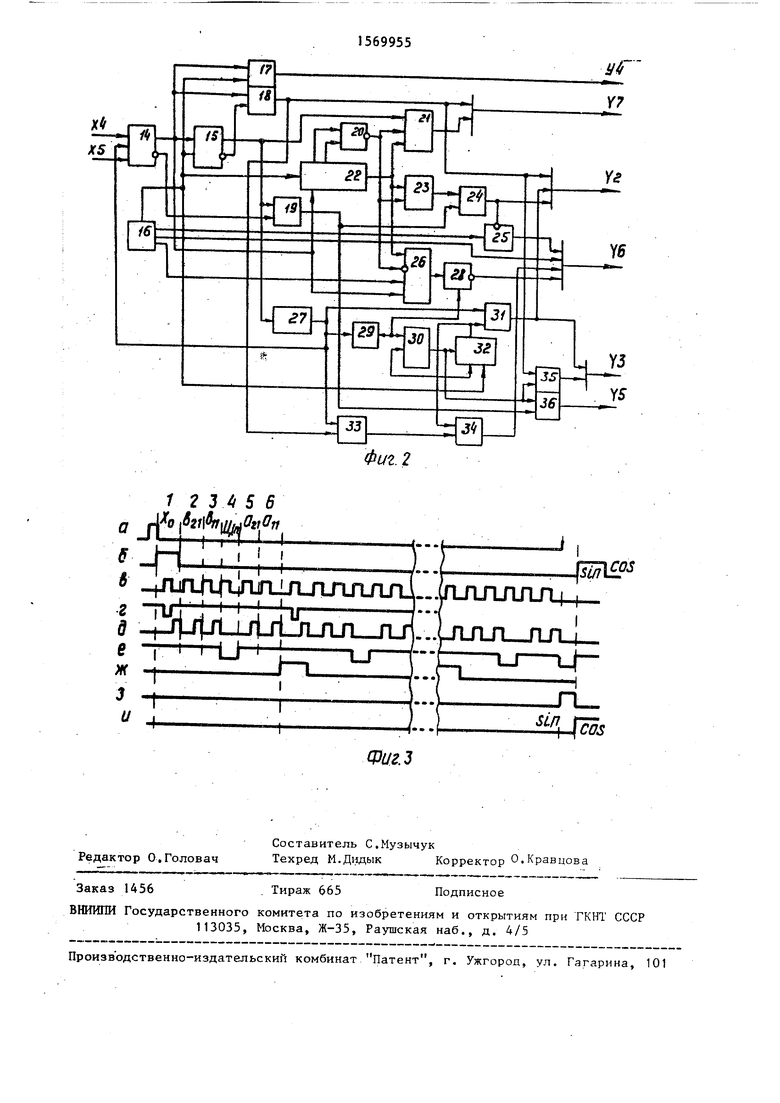

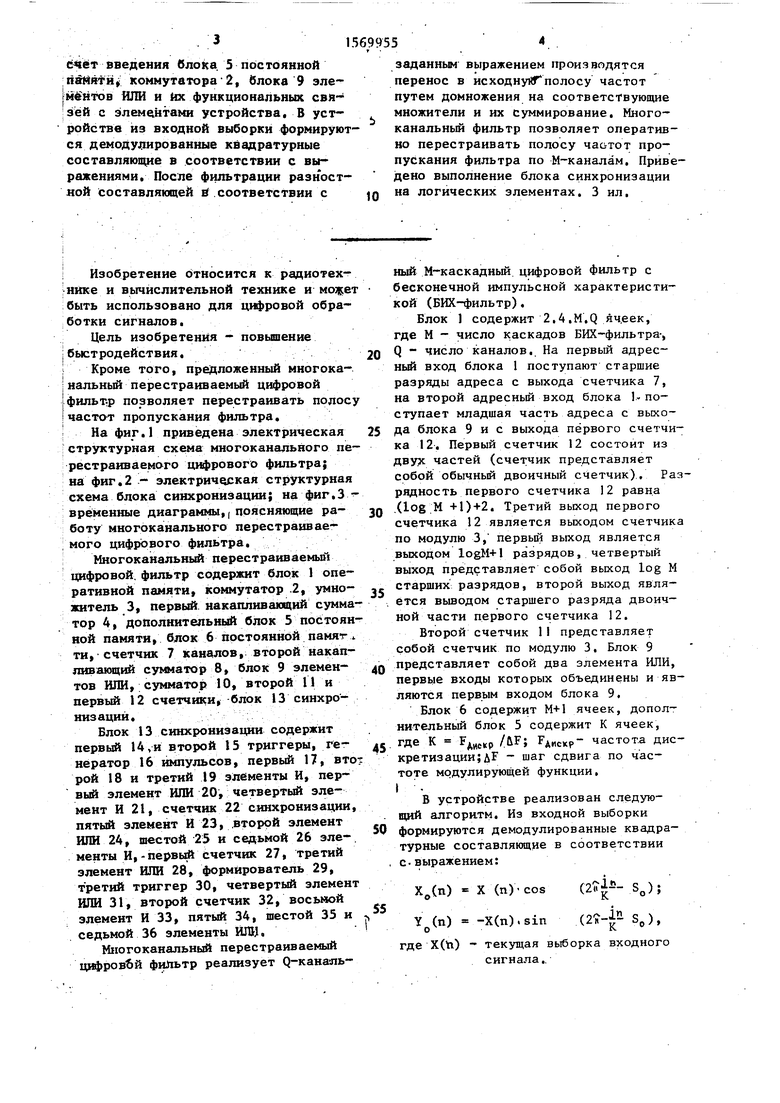

На фиг.1 приведена электрическая структурная схема многоканального перестраиваемого цифрового фильтра; на фиг.2 - электрическая структурная схема блока синхронизации; на фиг.З - временные диаграммы,, поясняющие ра- боту многоканального перестраиваемого цифрового фильтра.

Многоканальный перестраиваемый цифровой, фильтр содержит блок 1 оперативной памяти, коммутатор 2, умно- житель 3, первый накапливающий сумматор 4, дополнительный блок 5 постоянной памяти, блок 6 постоянной памят „ ти, счетчик 7 каналов, второй накапливающий сумматор 8, блок 9 элемен- тов ИЛИ, сумматор 10, второй 11 и первый 12 счетчики, блок 13 синхронизации.

Блок 13 синхронизации содержит первый 14,и второй 15 триггеры, ге- нератор 16 импульсов, первый 17, втот рой 18 и третий 19 элементы И, первый элемент ИЛИ 20, четвертый элемент И 21, счетчик 22 синхронизации, пятый элемент И 23, второй элемент ИЛИ 24, шестой 25 и седьмой 26 элементы И,-первый счетчик 27, третий элемент ИЛИ 28, формирователь 29, третий триггер 30, четвертый элемент ИЛИ 31, второй счетчик 32, восьмой элемент И 33, пятый 34, шестой 35 и седьмой 36 элементы ИЛИ.

Многоканальный перестраиваемый цифровой фильтр реализует Q-канальный М-каскадный цифровой фильтр с бесконечной импульсной характеристикой (БИХ-фильтр).

Блок 1 содержит 2.4.M.Q ячеек, где М - число каскадов БИХ-фильтра, Q - число каналов. На первый адресный вход блока 1 поступают старшие разряды адреса с выхода счетчика 7, на второй адресный вход блока 1- поступает младшая часть адреса с выхода блока 9 и с выхода первого счетчика 12. Первый счетчик 12 состоит из двух частей (счетчик представляет собой обычный двоичный счетчик). Рарядность первого счетчика 12 равна (log M +1)+2. Третий выход первого счетчика 12 является выходом счетчик по модулю 3, первый выход является выходом logM+1 разрядов, четвертый выход представляет собой выход log M старших разрядов, второй выход является выводом старшего разряда двоичной части первого счетчика 12.

Второй счетчик 11 представляет собой счетчик по модулю 3. Блок 9 представляет собой два элемента ИЛИ, первые входы которых объединены и являются первым входом блока 9.

Блок 6 содержит М+1 ячеек, дополнительный блок 5 содержит К ячеек, где К - /bF; ГА„скр- частота дискретизации; ДГ - шаг сдвига по частоте модулирующей функции,

I

В устройстве реализован следующий алгоритм. Из входной выборки формируются демодулированные квадратурные составляющие в соответствии с-выражением:

Х„(п) « X (n)-cos

( so);

Yo(n) - -X(n),sin ( Sc),

где X(ri) - текущая выборка входного сигнала.

Затем производится фильтрация разностной составляющей в соответствии с выражением: и;(п)-ь,; U;(n-i) +ь,;и;(п-2) + + S;, X;., (п);

X((n) U;(n) + aMU,(n-l) + az;U ;(n-2); и

v;(n) B,;v(n-l) +b2;V,(n-2) + S;- - Y«-,(n);

Y;(n) V;(n) i I,...,N,

+ a,;V(n-l) + a,;V(n-2);

где а,

51

Ч,1 , Ь5;- коэффициенты БИХ-фильтра; масштабирующий множител

Затем производится перенос в исходную полосу частот путем домноже- ния-на множители вида: sin(), cos(2 к n/N), и их суммирования.

Фильтр работает следующим образом

По импульсу, приходящему на трети управляющий вход устройства сбрасывается счетчик 7, второй счетчик II переходит в следующее состояние, на выходе второго накапливающего сумматора 8 формируете я суммарный код из предыдущего состояния второго накапливающего сумматора 8 и кода модулирующей функции, поступающего на второй управляющий вход устройства. Код приращения модулирующей функции равен j/К, где j - приведенная частота модулирующей функции.

Затем по импульсу сопровождения, поступающему на первый управляющий вход устройства (фиг,За), счетчик 7 переходит в следующее состояние и блок 13 начинает генерировать управляющие сигналы первого этапа обработки.

На управляющий вход коммутатора 2 с пятого выхода У7 блока 13 (фиг.Зб) поступает управляющий код, в результате чего к выходу коммутатора 2 подключается его первый вход. На втором выходе У6 блока 13 (фиг.Зг) формируется короткий импульс сброса, который поступает на управляющий вход первого накапливающего сумматора 4. С входа устройства входная выборка через первый вход коммутатора 2 поступает на второй вход умножителя 3, на первый вход которого поступает значение первой квадратурной составляющей демодулирующей функции из дополнительного блока 5, Результат умножения с выхода умножителя 3 заносится в первый накапливающий

;

;

569955

сумматор 4. Затем по импульсу, поступающему с первого входа У4 блока 13, устанавливается в следующее состояние первый счетчик 12 и из блока 1, по адресу, сформированному на первом и втором адресных входах, извлекает- ся первый сомножитель U(n-2) и через второй вход коммутатора 2 посту-.

IQ пает на второй вход умножителя 3, на первый вход которого с выхода блока 6 поступает коэффициент импульсной характеристики фильтра Ъг, . Результат умножения заносится в пер-

15 вый накапливающий сумматор 4. Затем аналогично извлекается второй сомножитель U,(n-l), умножается на коэффициент импульсной характеристики

фильтра b,, и заносится в первый накапливающий сумматор 4, В результате на выходе первого накапливающего сумматора 4 формируется текущее значение и(п) сомножителя, которое . записывается в блок 1 во время чет- вертого такта, затем из блока 1

извлекается вновь первый сомножитель U,(n-2) и через второй вход коммутатора 2 поступает на второй вход умножителя 3, на первый вход .которо- го поступает коэффициент импульсной характеристики фильтра а41, результат умножения записывается в первый накапливающий сумматор 4. Аналогично извлекается второй сомножитель U«(n-l), умножается на коэффициент

импульсной характеристики фильтра

.

и заносится в первый накапливающий сумматор 4. В результате на выходе первого накапливающего суммато-

ра 4 формируется первая квадратурная составляющая входной выборки, отфильтрованная первым каскадом фильтра. Затем на управляющий вход коммутатора 2 с пятого выхода У7 блока 13

(фиг.Зж) приходит управляющий код, в результате чего к выходу коммутатора 2 подключается его третий вход. Информация с выхода первого накапливающего сумматора 4 через третий вход

коммутатора 2 поступает на второй вход умножителя 3, на первый вход которого из дополнительного блока 5 поступает значение масштабирующего множителя. Одновременно импульсом с

второго выхода блока 13 обнуляется первый накапливающий сумматор 4. В дальнейшем обработка информации следующим каскадом фильтра не отличается от описанного, но с другими коэффициентами импульсной характеристики фильтра.

После обработки М-каскадом фильтра первая квадратурная составляющая входной выборки записывается в блок 1 по адресу, сформированному на втором адресном входе.

На втором этапе обработки входная выборка через первый вход коммутатора 2 поступает на второй вход умножи

теля 2, на первый вход которого поступает значение второй квадратурной составляющей демодулирующей функции из дополнительного блока 5. В даль- .- нейшем вторая квадратурная составляющая входной выборки обрабатывается аналогично первой.

После занесения в блок 1 второй квадратурной составляющей, отфильтрованной всеми каскадами фильтра, из блока 1 по адресу, сформированному на выходе блока 9, извлекается первая отфильтрованная квадратурная составляющая и через второй вход ком-25 мутатора 2 поступает на второй вход умножителя 3, на первый вход которого поступает первое значение коэффициента модулирующей функции из допол-

20

нительного блока 5. Результат умноже- зд импульсы записи информации в умножитель 3, и с выхода седьмого элемента И 26 через третий элемент ИЛИ 28, сформированные во время первых тактов работы каждого каскада фильтра. Задним фронтом импульса с выхода второго триггера 15 переключается в следующее состояние первый счетчик 27. Уровень логического сигнала с его выхода через четвертый элемент ИЛИ 31

40

35

ния с выхода умножителя 3 поступает в предварительно обнуленный первый

(накапливающий сумматор 4. После этого из блока 1 извлекается вторая отфильт рованная квадратурная составляющая и аналогично первой умножается на второе значение коэффициента модулирующей функции, и также заносится

(в первый накапливающий сумматор 4. В результате на выходе первого накапливающего сумматора 4 формируется отфильтрованное значение входной выборки в исходной полосе частот. Затем по следующему импульсу сопровождения на первом управляющем входе устройства переключается в следующее состояние счетчик 7 и входная выборка по следующему каналу обрабатывается аналогично описанному.

Блок 13 работает следующим образом.

По приходу импульса сопровождения на первый вход блока 13 устанавливается первый триггер 14, уровень логической 1 с его выхода открывает элементы И 17, 18 и 26. По синхроимпульсу с выхода генератора 16 устанавливается на следующем такте второй триггер 15 и разрешает работу

50

55

формирует на третьем и первом выходах УЗ и У2 блока 13 сигналы выбора sin/cos из блока 6 и 1-2 половины блока 1. Формирователь 29 формирует короткий импульс по заднему фронту сигнала с выхода первого счетчика 27, устанавливающий третий триггер 30, уровень логической с выхода которого через шестой элемент ИЛИ 35 на третьем выходе УЗ блока 13 выбирает дополнительный блок 5 и через седьмой элемент ИЛИ 36 на четвертом выходе блока 13 формирует импульс управления блоком 9. Уровень логической 1 с выхода третьего триггера 30 поступает на вход разрешения второго счетчика 32. По синхроимпульсам, поступающим из генератора 16, второй счетчик 32 последовательно формирует через элементы

-

5

счетчику 22. На выходе первого элемента И 17 и на первом выходе блока 13 формируются тактовые импульсы для счетчика 12. На выходе второго элемента И 18 формируется импульс, управляющий через пятый выход блока 13 коммутатором 2. Второй импульс управления коммутатором 2 формируется на выходе четвертого элемента И 21 после отработки одного каскада фильтра. Пятый элемент И 23 формирует на четвертом такте импульс записи информации в блок 1, поступающий через первый вход второго элемента ИЛИ 24 на первый выход блока 13, На второй вход второго элемента ИЛИ 24 с выхода третьего элемента И 19 поступает импульс записи в блок 1, сформированный после получения отфильтрованных квадратурных составляющих. I Импульс записи в блок 1 блокирует прохождение импульсов записи в первый накапливающий сумматор 4 через шестой элемент И 25. Данные импульсы с выхода шестого элемента И 25 поступают на второй выход блока 3. На этот же выход с одного из выходов генератора 16 поступают тактовые

формирует на третьем и первом выходах УЗ и У2 блока 13 сигналы выбора sin/cos из блока 6 и 1-2 половины блока 1. Формирователь 29 формирует короткий импульс по заднему фронту сигнала с выхода первого счетчика 27, устанавливающий третий триггер 30, уровень логической с выхода которого через шестой элемент ИЛИ 35 на третьем выходе УЗ блока 13 выбирает дополнительный блок 5 и через седьмой элемент ИЛИ 36 на четвертом выходе блока 13 формирует импульс управления блоком 9. Уровень логической 1 с выхода третьего триггера 30 поступает на вход разрешения второго счетчика 32. По синхроимпульсам, поступающим из генератора 16, второй счетчик 32 последовательно формирует через элементы

у1569955

34 на четвертом, третьем и ходах блока 13 сигналы управ оркой и умножением на знаулирующей функции. Фронтом с выхода второго счетчика вается третий триггер 30. лемент ИЛИ 36 формирует ие сигналы для блока 9 на выходе блока 13 в момент записи отфильтрованных квадкомпонент входной выборки.

гаемое устройство позволяет о перестраивать полосу часскания фильтра по М канасущественно расширяет функе возможности устройства.

10

15

н те хо до вы ра оп вы вх ко бл ко да ни вх с су ко 20 уп пе вх вх ро ти та ка ка вх му и с пе со со вх вы вы ра бл вх вт сум ка 45 пе

Формула изобретения

Многоканальный перестраиваемый цифровой фильтр, содержащий блок оперативной памяти, счетчик каналов, выход которого соединен с первым адресным входом блока оперативной памяти, последовательно соединенные первый счетчик, блок постоянной памяти, умножитель и первый накапливающий сумматор, выход которого является выходом многоканального перестраиваемо- го цифрового фильтра, последовательно соединенные второй счетчик и сумматор, а также второй накапливающий сумматор и блок синхронизации, первый вход которого является первым управляющим входом многоканального перестраиваемого цифрового фильтра, а второй вход блока синхронизации соединен с вторым выходом первого счетчика, вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с управляющим входом первого накапливающего сумматора, о тличаю- щ и и с я тем, что, с целью повыше

10

0

5

5

0

ния быстродействия, введены допдлни- тельный блок постоянной памяти, выход которого соединен с первым входом умножителя, блок элементов ИЛИ, выход которого соединен со старшими разрядами второго адресного блока оперативной памяти, и коммутатор, выход которого соединен с вторым входом умножителя, управляющий вход которого подключен к второму выходу блока синхронизации, третий выход . которого соединен с управляющими входами блока постоянной памяти и дополнительного блока постоянной памяти, вход последнего из которых соединен с выходом второго накапливающего сумматора, первый и второй входы которого Являются вторым и третьим 0 управляющими входами многоканального перестраиваемого цифрового фильтра, входом которого является первый вход коммутатора, второй вход которого соединен с выходом блока оперативной памяти, а третий вход коммутатора соединен с выходом первого накапливающего сумматора и входом блока оперативной памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, пятый и шестой выходы которого соединены с управляющим входом коммутатора и первым входом блока элементов ИЛИ соответственно, второй вход которого соединен с выходом сумматора, второй вход которого соединен с третьим выходом первого счетчика, четвертый выход которого соединен с младшими разрядами второго адресного входа блока оперативной памяти, причем вход второго счетчика соединен с вторым входом второго накапливающего сумматора и входом сброса счетчика каналов, вход которого соединен с 5 первым входом блока синхронизации.

5

0

X

v

xs

1 2 3 4 S 6 xo fzifoyftOtiOn

Фиг 2

Фиг.з

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-12—Подача