Изобретение относится к импульсной технике, а именно к устройствам с двумя устойчивыми состояниями. . Цель изобретения - упрощение синхронного D-триггера.

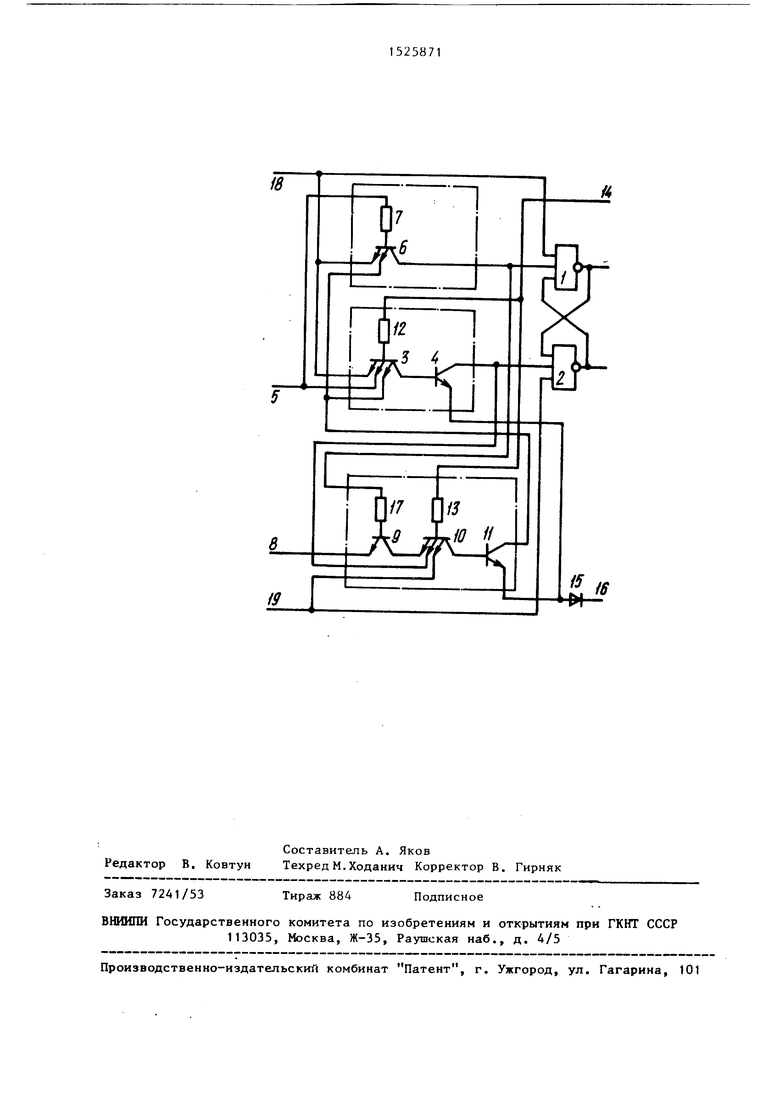

На чертеже приведена принципиальная схема синхронного D-триггера,

Синхронный D-триггер содержит первый 1 и второй 2 элементы И-НЕ транзисторно-транзисторной логики, выход первого элемента И-НЕ 1 соединен с первым входом второго элемента И-НЕ 2, выход которого соединен с первым входом первого элемента И-НЕ 1, коллектор третьего транзистора 3 соединен с базой первого транзистора 4, тактовый вход 5 синхронного D-триггера соединен со вторым эмиттером третьего транзистора 3 и базой пятого транзистора 6 через третий резистор 7, коллектор транзистора 6 и коллектор транзистора 4 соединены соответственно со вторьми входами первого и второго элементов И-НЕ 1,2, D-БХОд 8 синхронного

D-триггера соединен с эмиттером шестого транзистора 9, коллектор которого соединен с первым эмиттером четвертого транзистора 10, коллектор которого соединен с базой второго транзистора 11, базы транзисторов 3 и 10 соединены через соответственно первый и второй 12, 13 резисторы с шиной .питания 14, эмиттеры транзисторов 4 и 11 соединены с анодом диода 15, катод которого соединен с общей шиной 16, коллектор транзистора 11 соединен со вторым эмиттером транзистора 3 и эмиттером транзистора 6, коллектор транзистора 4 соединен со вторым эмиттером транзистора 10, а коллектор транзистора 6 соединен с базой транзистора 9 через четвертый резистор 17. На чертеже дополнительно показана организация входов асинхронной установки 18 и асинхронного сброса 19.

Транзистор 6 и резистор 7 образуют первый вспомогательный логический

О)

15

элемент, вьтолняющий функцию а-Ь + с, транзистор 3, транзистор 4 и резистор 12 образуют второй вспомогательный огический элемент, выполняющий ункцию И-НЕ, транзистор 10, транзисторы 9, 11 и резисторы 13,17 образуют третий вспомогательньй эле- мент, выполняющий функцию d-e-(+k). ри этом третий вспомогательный логи- д еский элемент образует RS-триггеры с первьм и вторьм логическими элеентами, а первый 1 и второй 2 элеенты И-НЕ образуют выходной RS-триг- гер.

Работа синхронного D-триггера отображается таблицей истинности.

При логическом О на тактовом входе 5 синхронного D-триггера первый и второй вспомогательные логические элементы устанавливаются в состояние 1/1, тем самым удерживая выходной RS-триггер в предыдущем состоянии. По переднему фронту тактирующего импульса третий вспомогательный логи- 25 ческий элемент устанавливает первый и второй логические элементы в соот- ветствии с D-входом, которые в свою очередь переключают выходной S-триггер и блокируют третий логический элемент от переключений. После, окончания тактового импульса состояние на выходах сохраняется. Таким образом, предлагаемое устройство выполняет функцию синхронного D-триггера, Формула изобретения 35

Синхронный D-триггер, содержащий первый и второй элементы И-НЕ тран20

30

5

д

5 5

0

0

зисторно-транзисторной логики, выход первого элемента И-НЕ соединен с пер- вьм входом второго элемента И-НЕ, выход которого соединен с первым входом первого элемента И-НЕ, эмиттеры первого и второго транзисторов через диод соединены с общей шиной, коллектор первого транзистора соединен с вторьи входом второго элемента транзисторно-транзисторной логики, а база подключена к коллектору третьего тран зистора, база которого через первый резистор соединена с шиной питания, а первый эмиттер - с тактовым входом, база второго транзистора соединена,с коллектором четвертого транзистора, база которого через второй резистор соединена с шиной метания, базы пятого и шестого транзисторов соединены с первьми выводами соответственно третьего и четвертого резисторов, эмиттер шестого транзистора соединен с D-вxoдoм,o т л и- чающийся тем, что, с целью упрощения, второй вывод третьего резистора соединен с тактовьм входом, эмиттер пятого транзистора - с вторьм эмиттером третьего транзистора и коллектором второго транзистора, коллектор пятого транзистора - с вторьм входом первого элемента И-НЕ транзисторно-транзисторной логики и вторым выводом четвертого резистора, коллектор шестого транзистора соединен с первым эмиттере четвертого транзистора, второй эмиттер которого соединен с коллектором первого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный @ -Триггер | 1985 |

|

SU1336208A1 |

| Синхронный Д-триггер | 1987 |

|

SU1429298A1 |

| ТРИГГЕРНЫЙ СИНХРОННЫЙ D ТРИГГЕР | 2024 |

|

RU2827115C1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1999 |

|

RU2211529C2 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ МИКРОПРОЦЕССОРНЫХ СИСТЕМ ЖЕЛЕЗНОДОРОЖНОЙ АВТОМАТИКИ ОТ АППАРАТНЫХ И ПРОГРАММНЫХ НАРУШЕНИЙ В РАБОТЕ И УСТРОЙСТВО СРАВНЕНИЯ ПАРАФАЗНЫХ СИГНАЛОВ С ЗАЩИТОЙ ОТ ОПАСНЫХ ОТКАЗОВ | 2009 |

|

RU2385521C1 |

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| RS-ТРИГГЕР | 2015 |

|

RU2604682C1 |

Изобретение относится к импульсной технике, а именно к устройствам с двумя устойчивыми состояниями. Целью изобретения является упрощение синхронного Д - триггера. Синхронный Д - триггер содержит два элемента И-НЕ транзисторно-транзисторной логики, шесть транзисторов, четыре резистора и диод. Введение новых связей позволяет уменьшить количество элементов при сохранении функций синхронного Д -триггера. 1 ил.

| Шагурин И.И | |||

| Транзисторно-транзисторные логические схемы | |||

| М.: Сов | |||

| радио, 1974, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Синхронный Д-триггер | 1987 |

|

SU1429298A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-30—Публикация

1987-12-25—Подача