сл С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

Изобретение относится к технике связи. Целью изобретения является увеличение пропускной способности. Устройство содержит приемник с блоками дискриминатора длительности импульсов и готовности к приему и передатчик с блоками регистра сдвига и логики формирования импульсов данных и синхронизации, манипулируемых по длительности. В устройство введены RS- триггеры и D-триггер, которые обеспечивают занесение данных из источника информации в регистр сдвига передатчика без подтверждения готовности к приему. 1 ил.

Изобретение относи гея к технике связи и может использоваться при построении приемопередатчиков широтно-импульсной манипуляции.

Цель изобретения - увеличение пропускной способности.

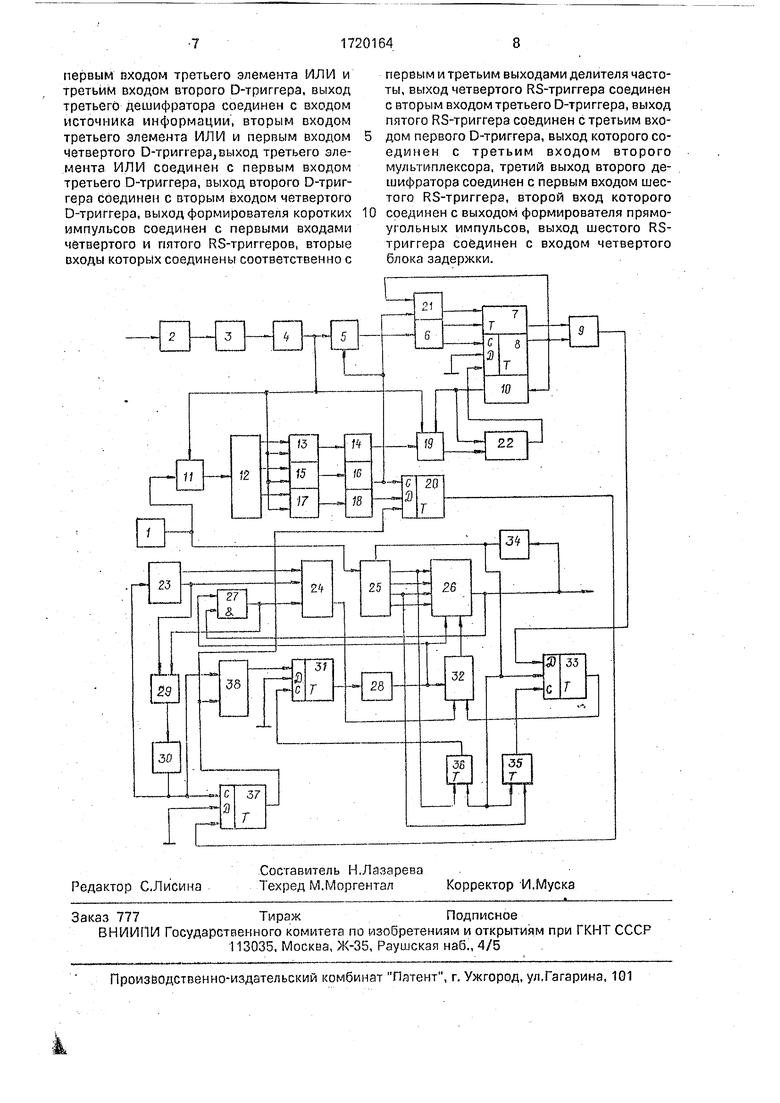

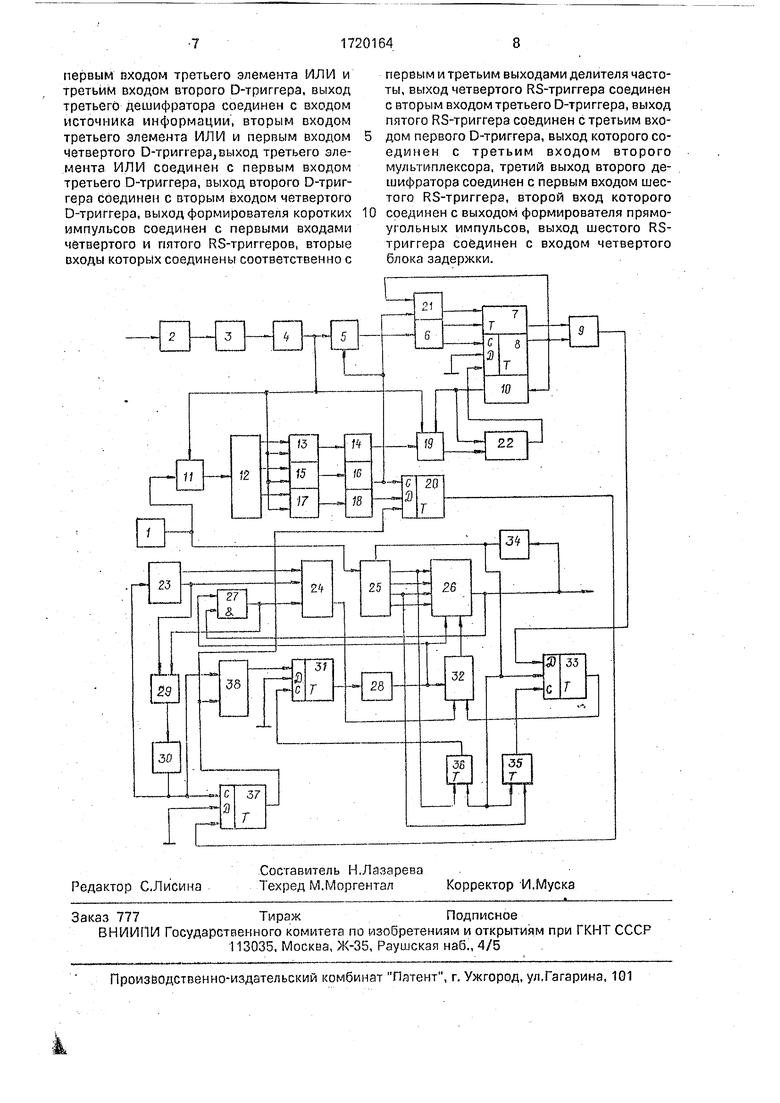

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импульсов, первый счетчик 5, первый Дешифратор 6, первый RS-триггер 7, триггер 8 буфер заполнен, первь(й элемент ИЛИ 9, второй блок 10 задержки, второй счетчик 11, второй дешифратор 12, второй RS-триггер 13, первый блок 14 задержки, третий RS-триггер 15 третий блок 16 задержки, шестой RS-триггер 17, четвертый блок 18 задержки, первый реп-.стр 19 сдви-. га, второй D-триггер 20, второй элемент

ИЛИ 21, блок 22 потребителя информации, источник 23 информации, второй регистр 24 сдвига, делитель 25 частоты, первый мультиплексор 26, элемент И 27, пятый блок 28 задержки, третий счетчик 29, третий дешифратор 30, третий D-триггер 31, второй мультиплексор 32, первый D-триггер 33, формирователь 34 коротких импульсов, пятый, четвертый RS-триггеры 35 и 36, четвертый D-триггер 37, третий элемент ИЛИ 38.

Устройство для приема и передачи данных работает следующим образом.

Делитель 25 делит частоту тактового генератора 1 и формирует на своих четырех выходах () четыре последовательности импульсов разной длительности Т1 Т2 ТЗ Т4, поступающие на мультиплексор 26. Выбор серии импульсов и их длительность на выходе мультиплексора 26 зависит от значения сигналов на его управляющих входах. С помощью формирователя 34 по заднему фронту каждого импульса происходит

vj Ю О

CN

N

синхронизация счетчиков делителя 25 для получения импульсов со скважностью 1/2. Данные от источника 23 записываются в параллельном коде в регистр 24.

Строб сопровождения данных устанавливает в нуль счетчик 29. При условии, что D-триггер находится в состоянии 1, очередным фронтом импульса с выхода RS- триггера 36 D-триггер 31 устанавливается в состояние, разрешающее через элемент И 27 выполнение сдвига в регистре 24 и счет числа переданных битов счетчиком 29. Кроме того, на управляющих входах мультиплексоров 26 и 32 устанавливаются значения сигналов, обеспечивающие формирование импульсов длительностью Т1 и Т2. Далее происходит сдвиг по каждому заднему фронту импульсов с выхода мультиплексора 26 данных в регистре 24.

В зависимости от значения очередного бита формируется импульс длительностью Т1 илиТ2. По окончании передачи происходит изменение значения сигнала на выходе дешифратора 30 (код, занесенный в счетчик 29, соответствует числу передаваемых битов в каждом поле данных), установка D-триггера 37 в О и через третий элемент ИЛИ 38 установка D-триггера 31 в состояние, обеспечивающее передачу импульсов синхронизации длительностью ТЗ или Т4, прекращение сдвига информации в регистре 24 и счета числа импульсов счетчиком 29.

Длительность импульсов синхронизации зависит от состояния D-триггера 33. Информация в D-триггер 33 записывается по- каждому переднему фронту импульса с выхода RS-триггера 35 и зависит от готовности устройства к приему. Установка в 1 R-S- триггеров 35 и 36 происходит по переднему фронту импульсов с выходов делителя 25. Сброс D-триггера 33, RS-триггеров 35 и 36 выполняется в конце цикла формирования каждого импульса на выходе мультиплексора 26 сигналом с выхода формирователя 34.

Задержка занесения информации о состоянии готовности к приему в D-триггер 33 на период паузы ТЗ позволяет подготовиться за это время к приему данных с линии связи путем считывания потребителем информации из регистра 19 и передать в цикле формирования импульса синхронизации сигнал о готовности к приему. В результате повышается пропускная способность устройства. Сброс D-триггера 33 в конце каждого импульса в состояние, обеспечивающее формирование импульсов длительностью Т4, необходим для устранения влияния на работу устройства переходных процессов.

По окончании передачи очередного поля информации сигнал с выхода дешифратора 30 поступает на вход источника 23 и сообщает ему о готовности к передаче, По

5 этому сигналу источник 23 в цикле формирования импульса синхронизации длительностью ТЗ выполняет запись очередного поля данных в регистр 24 и сброс в О счетчика 29. Однако нахождение D-триггера 37 в со0 стоянии О препятствует с помощью сигнала с его инверсного выхода, поступающего через элемент ИЛИ 38, установке тактирую- щ ими импульсами D-триггера 31 в состояние, обеспечивающее про5 должение передачи данных до момента получения сигнала о готовности-к приему от удаленного абонента. После получения сигнала о готовности к приему по заднему фронту синхроимпульса происходит установка в 1 D-триггера 20, сигнал с. выхода

0 которого устанавливает в 1 D-триггер 37, что в свою очередь вызывает сброс в О D-триггера 20.

В результате на выходе элемента ИЛИ 38 формируется сигнал, обеспечивающий

5 разрешение передачи данных по фронту очередного тактирующего импульса. В результате наличия RS-триггера 36 фронт тактирующего импульса на тактовом входе D-триггера 31 сдвинут относительно задне0 го фронта импульса на выходе мультиплексора 26 на величину паузы Т1, что и увеличивает пропускную способность устройства. При этом происходит переход к режиму передачи данных уже в процессе

5 формирования импульса синхронизации в его. начальной стадии с длительностью Т1.

Входной аналоговый сигнал из линии связи через входной усилитель 2, фильтр 3 нижних частот и формирователь 4 прямо0 угольных импульсов поступает на блоки 5, 11,19. Импульс, поступающий на установочный вход счетчика 11, разрешает начать измерение его длительности путем подсчета импульсов с выхода тактового генератора 1.

5 В зависимости от длительности входных импульсов с помощью дешифратора 12 устанавливаются в 1 триггеры 13, 15, 17.

Если длительность импульса Т4, то все триггеры устанавливаются в 1, при ТЗ-

0 триггеры 13 и 15, при Т2 - триггер 13. По заднему фронту входного импульса происходит сдвиг данных в регистре 19. Необходимая задержка обеспечивается блоком 14 задержки. Одновременно происходит счет 5 числа принятых битов счетчиком 5. Если принят хотя бы один бит, то сигналом с выхода дешифратора 6 устанавливается в 1 триггер 7, что означает Приемник занят,

После приема всего поля данных с известным фиксированным числом битов устанавливается в 1 триггер 8 и через эле мент ИЛИ 21 переводит в состояние О триггер 7. С помощью элемента ИЛИ 9 формируется сигнал К приему не готов, поступающий на D-вход триггера 33. Он запоминается по фронту импульса, поступающего на С-вход D-триггера 33. Сигнал Буфер заполнен с выхода триггера 8 через блок 10 задержки поступает на вход регистра 19, запрещая сдвиг в нем. Одновременно он поступает в блок 22. После считывания данных из регистра 19 блок 22 устанавливает триггер 8 в О.

При поступлении импульсов синхронизации длительностью ТЗ или Т4 выполняется сброс триггера 7 в нуль, установка в нуль счетчика.5 принятых битов. По заднему фронту импульса синхронизации выполняется занесение сигнала готовности к приему из триггера 17 в D-триггер 20. Последнее происходит лишь при отсутствии сигнала на установочном входе D-триггера 20 и соответствует завершению передачи данных. Необходимая задержка сигналов синхронизации обеспечивается блоками 16 и 18 задержки. В результате, если источник 23 информации осуществил занесение данных в регистр 24 для передачи, то происходит установка в 1 третьего D-три.тера 37, сброс второго D-триггера 20 и продолжается передача данных. Если данные не записаны из источника 23 информации в регистр 24 сдвига, то происходит лишь установка в 1 D-триггера 37 и в О D-триггера 20. Продолжение передачи данных происходит после записи их в регистр 24.

По окончании входного импульса (во время паузы) происходит сброс триггеров 13,15,17 и счетчика 11 и прекращение счета последним.

Пятый вход первого мультиплексора и первый вход второго мультиплексора подключены к выходу блока 28 задержки, так как в реальном устройстве функцию задержки сигнала выполняет сам D-триггер 31 формирования импульса синхронизации.

Формула изобретения Устройство для последовательного обмена данными с квитированием, содержащее последовательно соединенные усилитель, фильтр нижних частот, формирователь прямоугольных импульсов, первый счетчик, первый дешифратор, первый RS- триггер, первый элемент ИЛИ и первый D- триггер, последовательно соединенные второй счетчик, второй дешифратор, второй RS-триггер, первый блок,задержки, первый

регистр сдвига, блок потребителя информации, триггер буфер заполнен и второй блок задержки, выход которого соединен с вторым входом блока потребителя информации и вторым входом первого регистра 5 сдвига, второй выход второго дешифратора через последовательно соединенные третий RS-триггер и третий блок задержки соединен с вторым входом первого счетчика, первым входом второго D-триггера и пер0 вым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом первого, элемента ИЛИ и выходом триггера буфер заполнен, второй вход второго D- триггера соединен с выходом четвертого

5 блока задержки, выход формирователя пря- моугольных импульсов соединен с первым входом второго счетчика, вторыми входами второго и третьего RS-триггеров и третьим входом первого регистра сдвига, выход ге0 нератора тактовых импульсов соединен с вторым входом второго счетчика и первым входом первого делителя частоты, первый, второй, третий выходы которого соединены соответственно с первым, вторым, третьим

5 входами первого мультиплексора, выход третьего D-триггера через пятый блок задержки соединен с первым входом второго мультиплексора, выход которого соединен с четвертым входом первого мультиплексораг

0 пятый вход которого и первый вход элемента И соединены с выходом пятого блока задержки, выход первого мультиплексора является еыходом устройства и соединен с вторым входом элемента И и через форми5 рователь коротких импульсов с вторым входом делителя частоты и вторым входом первого D-триггера, первый выход источника информации соединен с первым входом второго регистра сдвига, второй вход кото0 рого и первый вход третьего счетчика соеди- нены с вторым выходом источника информации, выход элемента И соединен с третьим входом второго регистра сдвига и вторым входом третьего счетчика, выход ко5 торого соединен с входом третьего дешифратора, выход второго регистра сдвига соединен с вторым входом второго мультиплексора, выход второго элемента ИЛИ соединен с вторым входом первого

0 RS-триггера, втор ой выход первого дешифратора соединен с вторым входом триггера буфер заполнен, а также третий элемент ИЛИ, отличающееся тем, что, с целью увеличения пропускной способности, в него

5 введены четвертый, пятый, шестой RS-триг- геры и четвертый D-триггер, причем четвертый выход делителя частот соединен с шестым входом первого мультиплексора, выход четвертого D-триггера соединен с

первым входом третьего элемента ИЛИ и третьим входом второго D-триггера, выход третьего дешифратора соединен с входом источника информации, вторым входом третьего элемента ИЛИ и первым входом четвертого D-триггера, выход третьего элемента ИЛИ соединен с первым входом третьего D-триггера, выход второго D-триггера Соединен с вторым входом четвертого D-триггера, выход формирователя коротких импульсов соединен с первыми входами четвертого и пятого RS-триггеров, вторые входы которых соединены соответственно с

0

первым и третьим выходами делителя частоты, выход четвертого RS-триггера соединен с вторым входом третьего D-триггера, выход пятого RS-триггера соединен с третьим входом первого D-триггера, выход которого со- единен с третьим входом второго мультиплексора, третий выход второго дешифратора соединен с первым входом шестого RS-триггера, второй вход которого соединен с выходом формирователя прямоугольных импульсов, выход шестого RS- триггера соединен с входом четвертого блока задержки.

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-15—Публикация

1989-08-18—Подача