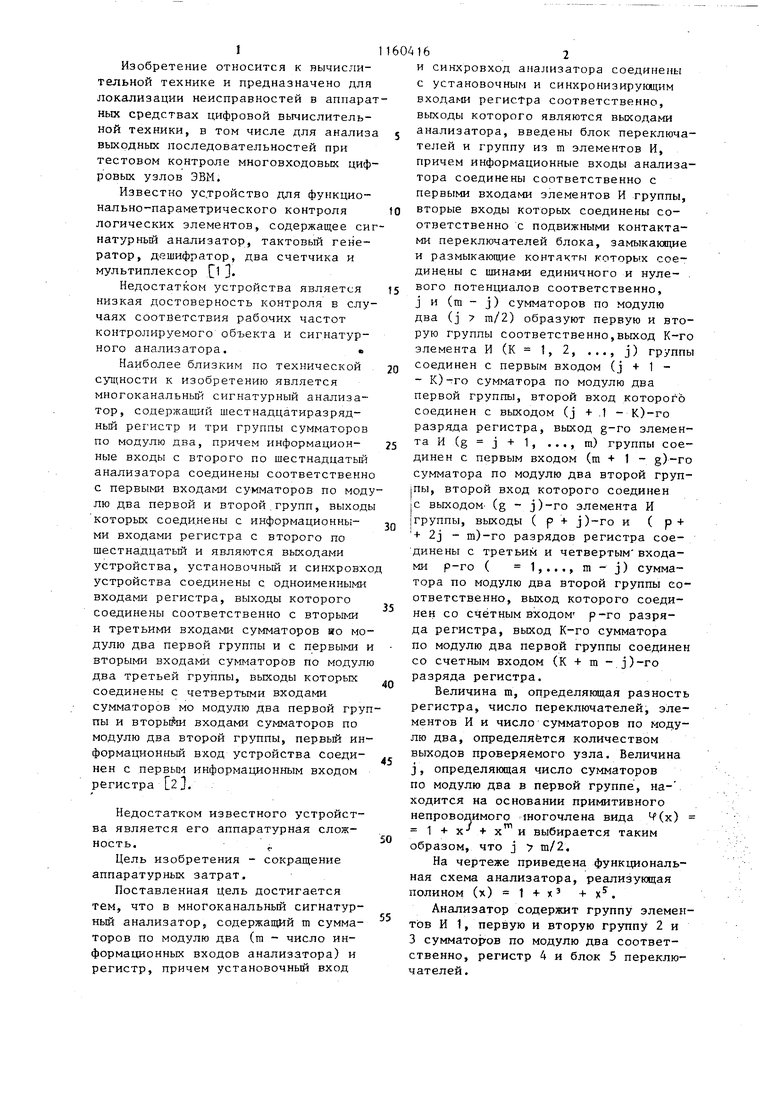

1 Изобретение относится к вычислительной технике и предназначено для локализации неисправностей в аппара ных средствах цифровой вычислительной техники, в том числе для анализ выходных последовательностей при тестовом контроле многовходовых циф ровых узлов ЭВМ. Известно устройство для функционально-параметрического контроля логических элементов, содержащее си натурный анализатор, тактовый генератор, дешифратор, два счетчика и мультиплексор 1J. Недостатком устройства является низкая достоверность контроля в слу чаях соответствия рабочих частот контролируемого объекта и сигнатурного анализатора. Наиболее близким по технической сущности к изобретению является многоканальный сигнатурный анализатор, содержащий шестнадцатиразрядный регистр и три группы сумматоров по модулю два, причем информационные входы с второго по шестнадцатый анализатора соединены соответственн с первыми входами сумматоров по мод лю два первой и второй . групп, выход которых соединены с информационными входами регистра с второго по шестнадцатый и являются выходами устройства, установочный и синхровх устройства соединены с одноименными входами регистра, выходы которого соединены соответственно с вторыми и третьими входами сумматоров но мо дулю два первой группы и с первыми вторыми входами сумматоров по модул два третьей группы, выходы которых соединены с четвертыми входами сумматоров МО модулю два первой гру пы и вторым входами сумматоров по модулю два второй группы, первьй ин формационный вход устройства соединен с первым информационным входом регистра 2 J. Недостатком известного устройства является его аппаратурная сложность. Цель изобретения - сокращение аппаратурных затрат. Поставленная Цель достигается тем, что в многоканальный сигнатурный анализатор, содержащий m сумматоров по модулю два (т - число информационных входов анализатора) и регистр, причем установочный вход 162 и синхровход анализатора соединены с установочным и синхронизирующим входами регистра соответственно, выходы которого являются выходами анализатора, введены блок переключатeJтeй и группу из m элементов И, причем информационные входы анализатора соединены соответственно с первыми входами элементов И группы, вторые входы которых соединены соответственно с подвижными контактами переключателей блока, замыкающие и размыкающие контакты которьх соединены с шинами единичного и нуле- , вого потенциалов соответственно, j и (га - j) сумматоров по модулю два (j 7 га/2) образуют первую и вторую группы соответственно,выход К-го элемента И (К 1, 2, ..., j) группы соединен с первым входом (j + 1 - К)-го сумматора по модулю два первой группы, второй вход которого соединен с выходом (j + .1 - К)-го разряда регистра, выход g-ro элемента И (g j + 1 , ..., m) группы соединен с первым входом (т + 1 - g)-ro сумматора по модулю два второй группы, второй вход которого соединен с выходом- (g - j)-ro элемента И группы, выходы ( р + j)-ro и ( р + + 2J - т)-го разрядов регистра соединены с третьим и четвертымвходами р-го ( 1,...,m-j) сумматора по модулю два второй группы соответственно, выход которого соединен со счётным ВХОДОМ р-го разряда регистра, ВЬЕХОД К-го сумматора по модулю два первой группы соединен со счетным входом (К + m -,j)-ro разряда регистра. Величина т, определяющая разность регистра, число переключателей, элементов И и число сумматоров по модулю два, определяется количеством выходов проверяемого узла. Величина j, определяющая число сумматоров по модулю два в первой группе, находится на основании примитивного непроводимого 1ногочлена вида (х) 1 + х- -I- х и выбирается таким образом, что j у га/2. На чертеже приведена функциональная схема анализатора, реализующая полином (х) 1 + х + х. Анализатор содержит группу элементов И 1, первую и вторую группу 2 и 3 сумматоров по модулю два соответственно, регистр 4 и блок 5 переключателей . Анализатор работает следующим образом. Сигналом с установочного входа анализатора устанавливаются в О в разряды регистра 4. На входы элемен тон И 1 поступает информация с выхо дов проверяемого блока, сопровождае мая синхросигналами. В многоканальном режиме все переключатели блока находятся в положении, обеспечивающем подачу на вторые входы элементов И 1 единичного потенциала. Сжатие входной информации - суммирование :мо модулю два выполняется .как на сумматорах групп 2 и 3 по модулю два, так и на триггерах со счетным входом регистра 4, информация с выходов которого представляет собой код (сигнатуру, поступающий с выходов анализатора на средства индикации для сравнения его с эталонным. Для локализации неисправностей в проверяемом блоке предусмотрена воз можность задания режимов с произвольным количеством его выходов с помощью переключателей блока 5. Известный анализатор для своей реализации требует 12 двухвхбдовых и 10 четьфехвходовых сумматоров по модулю два, суммарное количество входов которьск равняется 64, Таким образом, приведенные аппа рурные затраты на реализацию блока сумматора по модулю два .на один 164 разряд многоканального сигнатурного анализатора, равны 64/15, Величина 15 определяется тем, что в известном анализаторе (к) 1 + х Т.е.. В предлагаемом анализаторе для той же величины т, используяj например, полином (х) 1 X + X , получаемый из таблицы З при замене j на (m - j), количество входов сумматоров по модулю два определяется следующим образом: 2j + + ,4 (ш - j) 2-14 + 4 32. Для построения многоканального анализатора необходимо j 14 д ухвходовЬк сумматоров по модулю два и (га - j) четьфехвходовых сумматоров по модулю, два (т - j 1), Таким образом, приведенные аппаратурные затраты на один разряд предлагаемого айализатора 32/15, и сложность реализации блока сумматоров МО модулю два значительно меньше. Кроме того, предлагаемый анал затор отличается .более высоким быстродействием по сравнений с известным,, так как комбинационная чисть анализатора состоит из одноуровневой схемы, в то время как в известном устройстве комбинационная часть состоит из двух уровней (для большинства разрядов) сумматоров по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

| Многофункциональный модуль для устройств встроенного контроля | 1987 |

|

SU1529222A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1647571A1 |

| Многоканальный сигнатурный анализатор для микропроцессорной системы | 1986 |

|

SU1374226A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1795459A1 |

| Сигнатурный анализатор | 1986 |

|

SU1377859A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР, содержащий m сумматоров по модулю два (т - число информационных входов анализатора) и регистр причем установочный вход и синхровход анализатора соединены с устано вечным и синхронизируклцим входами parHCT f a соответственно, выходы которого являются выходами анализатора, отличающийся тем, что, с целью сокращения аппаратурны затрат, он содержит блок переключателей и группу из элементов И, причем информационные входы анализатора соединены соответственно с пер выми входами элементов И группы. вторые входы которых соединены Ьоответственно с подвижными контактами переключателей блока, замыкайщие и размыкающие контакты которых соединены с .пшнами единичного и нулевого потенциалов соответственно, j я (т - j ) сумматоров по модулю два (J т/2) образуют первую и вторую группы соответственно, выход К-го элемента И (К 1, 2, ..., j) группы соединен с первым входом (j 1 -К)-го сумматора по модулю два первой группы, второй вход которого соединен с выходом (j 1 - К)-го разряда регистра, выход -го элемента И (g 3 1J « ni) грзшпы соединен с первым входом (т + 1 -g)-ro сумматора по. модулю два второй группы, второй вход которого .соединен с выходом Cg-j)-ro элементам группы, выходы (р + j)-ro и (р + 2j - m)-ro разрядов регистра соединень с Третьим и четвертым входами р-го (,.,,, m- j) сумматора по модулю два :второй группы соответственно, выход которого соединен со счетным входом р-го разряда регистра, выход К-го -сумматора по модулю два первой группы соединен со счетным входом (К «- га - j)-ro разряда регистра.

Авторы

Даты

1985-06-07—Публикация

1983-04-11—Подача