3152

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации счетчиков, регистров и других технических средств этой области.

Цель изобретения - повышение быстродействия при сохранении помехозащищенности .

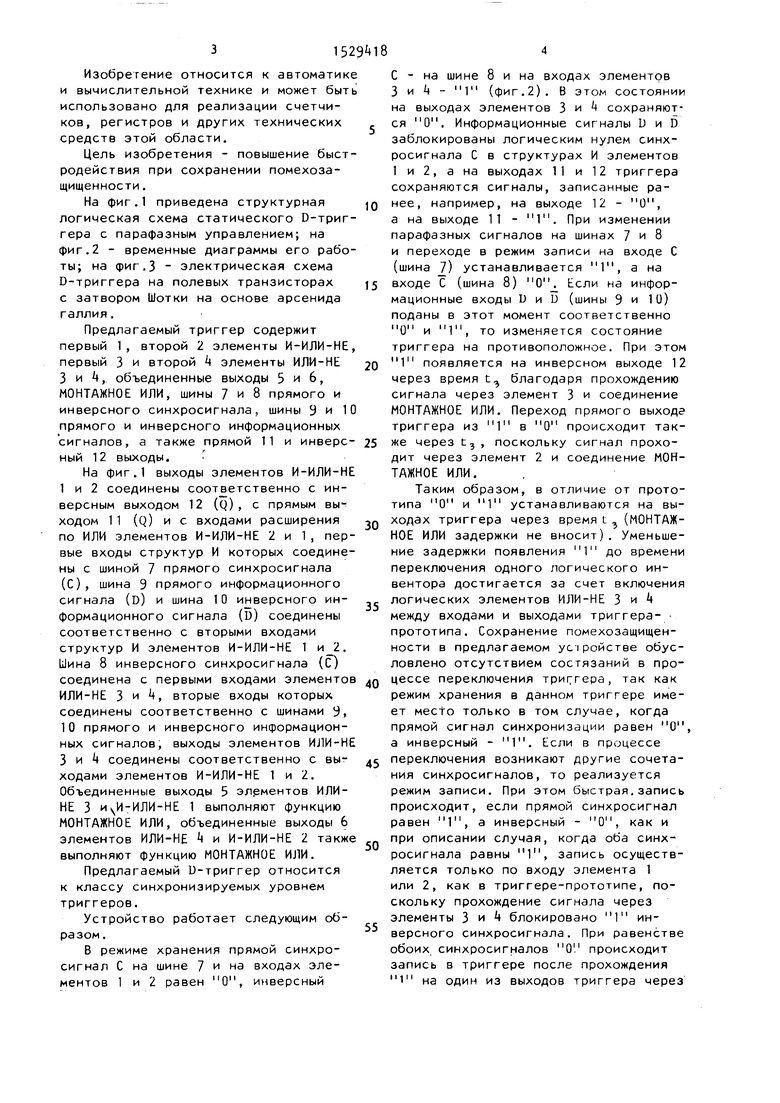

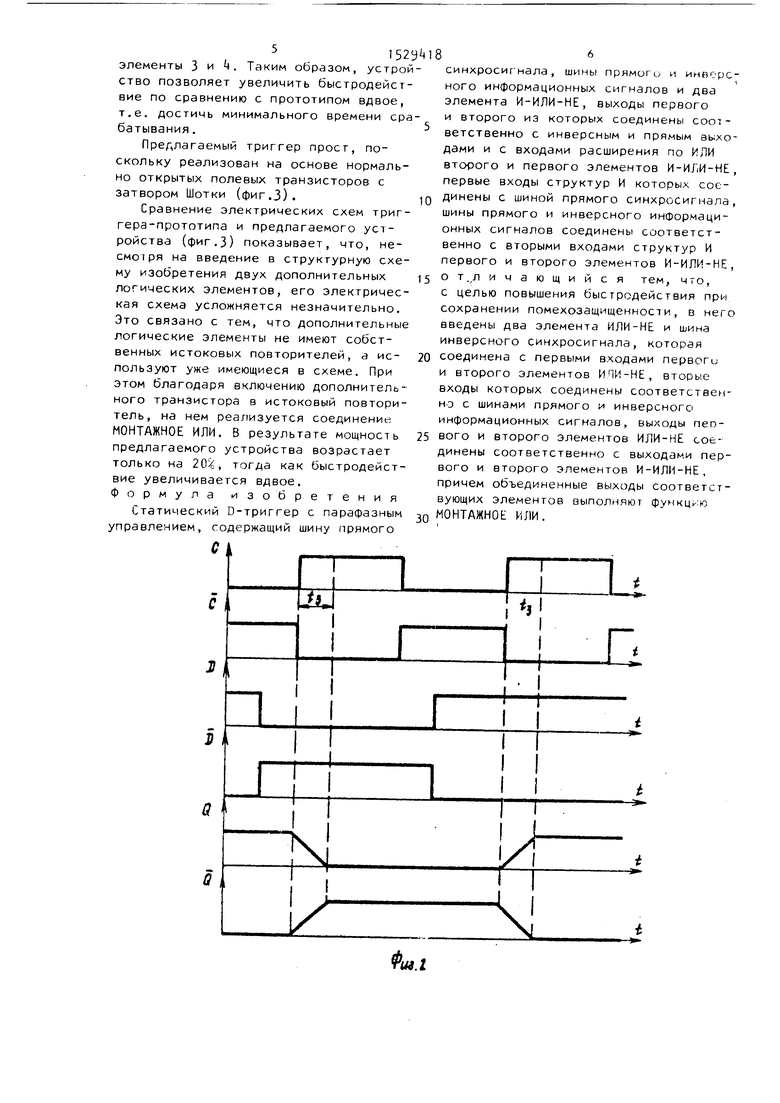

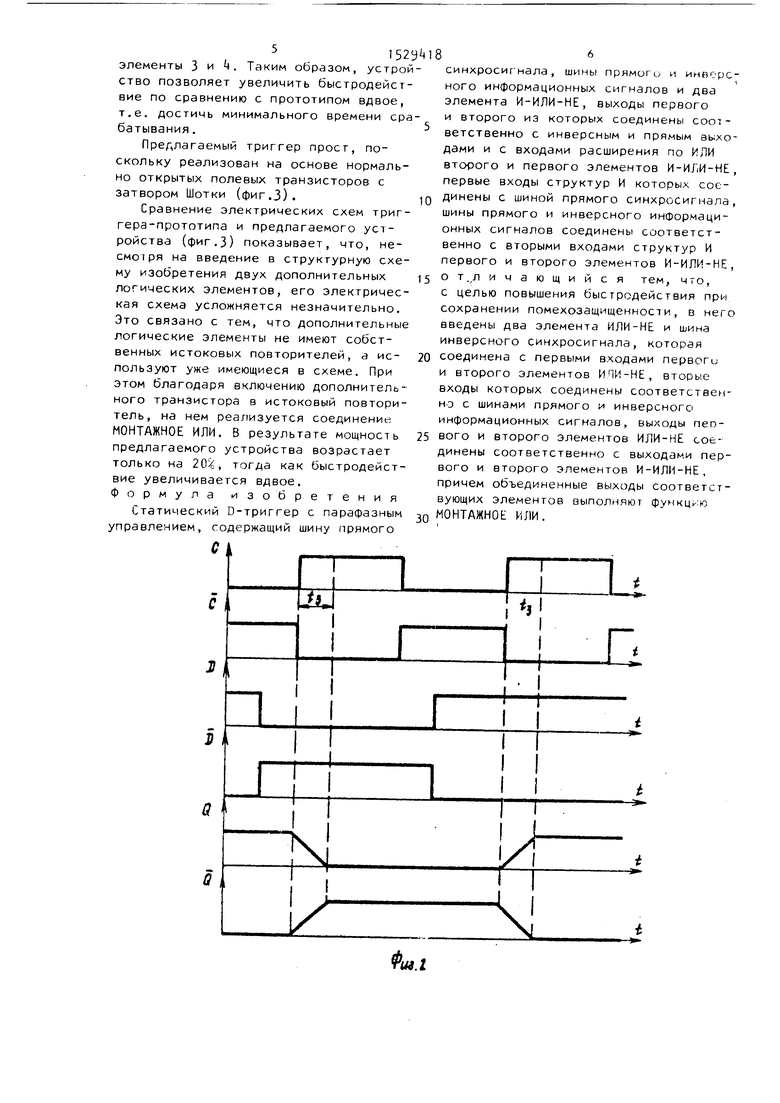

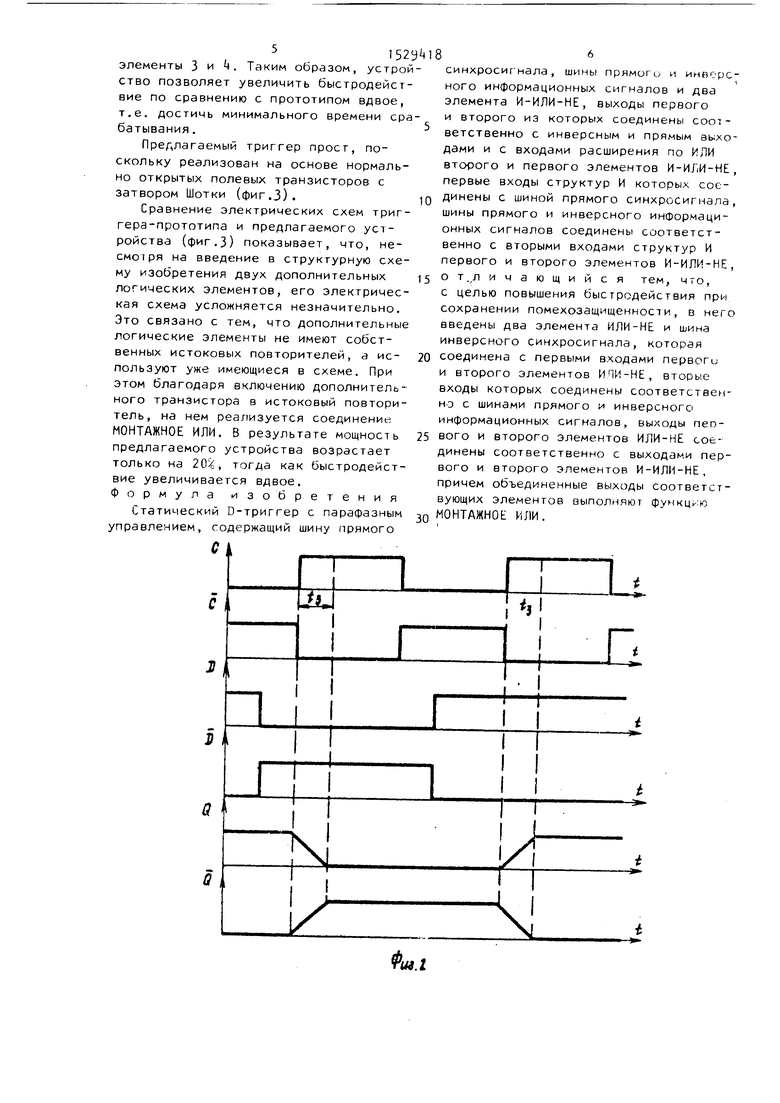

На фиг,1 приведена структурная логическая схема статического D-триг- гера с парафазным управлением; на фиг.2 - временные диаграммы его работы; на фиг.З электрическая схема D-триггера на полевых транзисторах с затвором Шотки на основе арсенида галлия .

Предлагаемый триггер содержит первый 1, второй 2 элементы И-ИЛИ-НЕ, первый 3 и второй k элементы ИЛИ-НЕ 3 и i, объединенные выходы 5 и 6, МОНТАЖНОЕ ИЛИ, шины 7 и 8 прямого и инверсного синхросигнала, шины 9 и 10 прямого и инверсного информационных сигналов, а также прямой 11 и инверс- ный 12 выходы.

На фиг.1 выходы элементов И-ИЛИ-НЕ 1 и 2 соединены соответственно с инверсным выходом 12 (Q) , с прямым вы- ходом 11 (Q) и с входами расширения по ИЛИ элементов И-ИЛИ-НЕ 2 и 1, первые входы структур И которых соединены с шиной 7 прямого синхросигнала (с), шина 9 прямого информационного сигнала (в) и шина 10 инверсного информационного сигнала (D) соединены соответственно с вторыми входами структур И элементов И-ИЛИ-НЕ 1 и 2. Шина 8 инверсного синхросигнала (С соединена с первыми входами элементов ИЛИ-НЕ 3 и 4, вторые входы которых соединены соответственно с шинами 9, 10 прямого и инверсного информационных сигналов, выходы элементов ИЛИ-НЕ 3 и 4 соединены соответственно с вы- ходами элементов И-ИЛИ-НЕ 1 и 2. Объединенные выходы 5 элементов ИЛИ- НЕ 3 ИуИ-ИЛИ-НЕ 1 выполняют функцию МОНТАЖНОЕ ИЛИ, объединенные выходы 6 элементов ИЛИ-НЕ и И-ИЛИ-НЕ 2 также выполняют функцию МОНТАЖНОЕ ИЛИ.

Предлагаемый D-триггер относится к классу синхронизируемых уровнем триггеров.

Устройство работает следующим образом .

В режиме хранения прямой синхросигнал С на шине 7 и на входах элементов 1 и 2 равен О, инверсный

Q 5

0 5

n Q

5

0

5

С - на шине 8 и на входах элементов 3 и 4 - 1 (фиг.2). В этом состоянии на выходах элементов 3 и 4 сохраняются О. Информационные сигналы D и D заблокированы логическим нулем синхросигнала С в структурах И элементов 1 и 2, а на выходах 11 и 12 триггера сохраняются сигналы, записанные ранее, например, на выходе 12 - О, а на выходе 11 - 1. При изменении парафазных сигналов на шинах 7 и 8 и переходе в режим записи на входе С (шина 7) устанавливается 1, а на входе С (шина 8) 0 Если на информационные входы D и D (шины 9 и 10) поданы в этот момент соответственно О и 1, то изменяется состояние триггера на противоположное. При этом 1 появляется на инверсном выходе 12 через время t благодаря прохождению сигнала через элемент 3 и соединение МОНТАЖНОЕ ИЛИ. Переход прямого выходе триггера из 1 в О происходит также через tj , поскольку сигнал проходит через элемент 2 и соединение МОНТАЖНОЕ ИЛИ. ,

Таким образом, в отличие от прототипа О и 1 устанавливаются на выходах триггера через время t (МОНТАЖНОЕ ИЛИ задержки не вносит). Уменьшение задержки появления 1 до времени переключения одного логического ин- вентора достигается за счет включения логических элементов ИЛИ-НЕ 3 и между входами и выходами триггера- прототипа. Сохранение помехозащищенности в предлагаемом усч ройстве обусловлено отсутствием состязаний в процессе переключения три17гера, так как режим хранения в данном триггере имеет место только в том случае, когда прямой сигнал синхронизации равен О, а инверсный - 1. Если в процессе переключения возникают другие сочетания синхросигналов, то реализуется режим записи. При этом быстрая,запись происходит, если прямой синхросигнал равен 1, а инверсный - О, как и при описании случая, когда оба синхросигнала равны 1, запись осуществляется только по входу элемента 1 или 2, как в триггере-прототипе, поскольку прохождение сигнала через элементы 3 и t блокировано 1 инверсного синхросигнала. При равенстве обоих синхросигналов О , происходит запись в триггере после прохождения 1 на один из выходов триггера через

элементы и k. Таким образом, устройство позволяет увеличить быстродействие по сравнению с прототипом вдвое, т.е. достичь минимального времени срабатывания .

Предлагаемый триггер прост, поскольку реализован на основе нормально открытых полевых транзисторов с затвором Шотки (фиг.З),

Сравнение электрических схем триггера-прототипа и предлагаемого устройства (фиг.З) показывает, что, несмотря на введение в структурную схему изобретения двух дополнительных логических элементов, его электрическая схема усложняется незначительно. Это связано с тем, что дополнительные логические элементы не имеют собственных истоковых повторителей, а ис- пользуют уже имеющиеся в схеме. При этом благодаря включению дополнительного транзистора в истоковый повторитель, на нем реализуется соединение МОНТАЖНОЕ ИЛИ. В результате мощность предлагаемого устройства возрастает только на 20%, тогда как быстродействие увеличивается вдвое. Формула изобретения

Статический D-триггер с парафазным управлением, содержащий щину прямого

синхросигнала, шины прямого и инверсного информационных сигналов и два элемента И-ИЛИ-НЕ, выходы первого и второго из которых соединены соответственно с инверсным и прямым выходами и с входами расширения по ИЛИ второго и первого элементов И-ИЛИ-НЕ, первые входы структур И которых соединены с шиной прямого синхросигнала, шины прямого и инверсного информационных сигналов соединены соответственно с вторыми входами структур И первого и второго элементов И-ИЛИ-НЕ, о т.,л ичающийся тем, что, с целью повышения быстродействия при сохранении помехозащищенности, в него введены два элемента ИЛИ-НЕ и шина инверсного синхросигнала, которая соединена с первыми входами первого- и второго элементов ИЛИ-НЕ, вторые входы которых соединены соответственно с шинами прямого и инверсного информационных сигналов, выходы пео- вого и второго элементов ИЛИ-НЕ соединены соответственно с выходами первого и второго элементов И-ИЛИ-НЕ, причем объединенные выходы соответствующих элементов оыполняют фуикц1 :ю МОНТАЖНОЕ ИЛИ.

HfJl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования манчестерского кода | 1987 |

|

SU1594701A1 |

| Универсальный ДV/Т/ триггер | 1988 |

|

SU1594673A1 |

| Универсальный DV(Т)-триггер | 1989 |

|

SU1698957A1 |

| ДВУХСТУПЕНЧАТЫЙ ТРИГГЕР | 2005 |

|

RU2294593C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство выборки-хранения | 1989 |

|

SU1612324A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2013015C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации счетчиков, регистров и других технических средств этой области. Цель изобретения - повышение быстродействия при сохранении помехозащищенности. Для этого в Д-триггер введены элементы ИЛИ-НЕ 3,4, объединенные выходы 5,6 "Монтажное ИЛИ" и шина 8 инверсного синхросигнала. Устройство также содержит элементы И-ИЛИ-НЕ 1,2, шину 7 прямого синхросигнала, шины 9,10 прямого и инверсного информационных сигналов, прямой и инверсный выходы 11,12. В предлагаемом Д-триггере сокращено время переходных процессов на выходах до одной элементарной задержки логического элемента. 1 ил.

Й/г.З

| Букреев И.Н, и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Сов.радио, 1975, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Алексеенко А.Г | |||

| и др | |||

| Микросхемотехника | |||

| - М.: Рад | |||

| и связь, 1982, с | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-22—Подача