Изобретение относится к автоматике и вычислительной технике, может быть использовано при построении преобразователей и касается усовершенст- вования известного устройства по авт.св. № 860054.

Целью изобретения является повышение точности преобразования за счет округления младшего разряда.

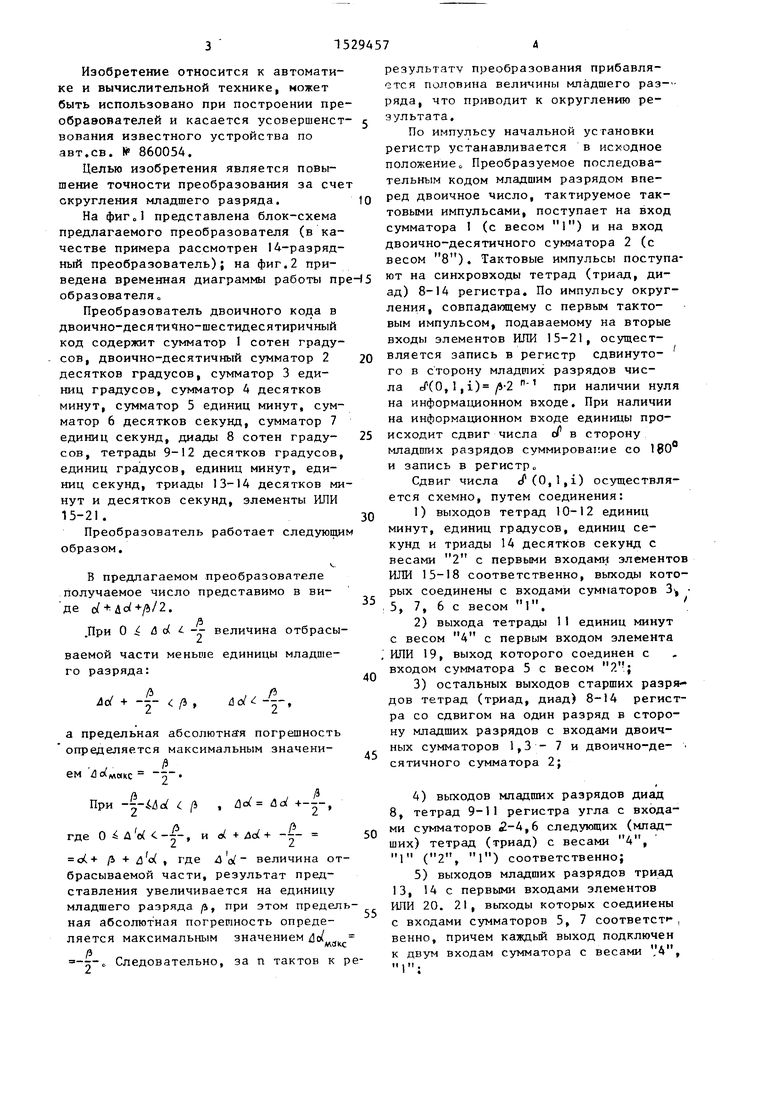

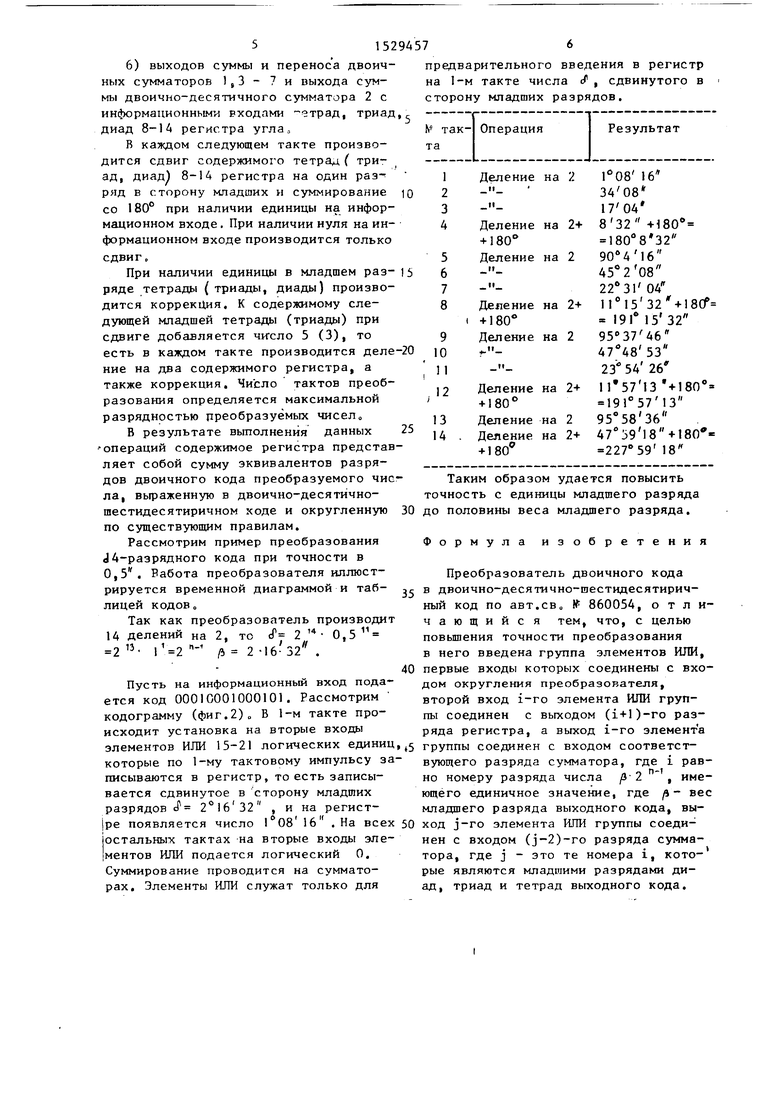

На фиг,1 представлена блок-схема предлагаемого преобразователя (в качестве примера рассмотрен 14-разрядный преобразователь); на фиг.2 приведена временная диаграммы работы пре образователя„

Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код содержит сумматор I сотен градусов, двоично-десятичный сумматор 2 десятков градусов, сумматор 3 единиц градусов, сумматор 4 десятков минут, сумматор 5 единиц минут, сумматор 6 десятков секунд, сумматор 7 единиц секунд, диады 8 сотен граду- сов, тетрады 9-12 десятков градусов, единиц градусов, единиц минут, единиц секунд, триады 13-14 десятков минут и десятков секунд, элементы ИЛИ 15-21.

Преобразователь работает следукирим образом.

В предлагаемом преобразователе получаемое число представимо в ви де d+-&ci+/ /2.

а.

.При О и d -- величина отбрасываемой части меньше единицы младшего разряда:

Л , /3 Ло( + - ft , /30/ ---,

а предельная абсолютнЯ Я погрешность определяется максимальным значениftем /1о(мкс

При i /i , do +---,

где О i д о( , и е( + ud+ -

o(-t- /i + V, где величина отбрасываемой части, результат представления увеличивается на единицу младшего разряда , при этом пределная абсолютная погрепшость определяется максимальным значением uoi

ЛЛЯК

Следовательно, за п тактов к ре- „ „ «

13, ИЛИ с вх венн к дв

j

0

5

0 5 0

5

0

5

0

„ „ «

результату преобразования прибавляется половина величины младшего раз- ряда, что приводит к округлению результата.

По импульсу начальной установки регистр устанавливается в исходное положение„ Преобразуемое последовательным кодом младшим разрядом вперед двоичное число, тактируемое тактовыми импульсами, поступает на вход сумматора 1 (с весом 1) и на вход двоично-десятичного сумматора 2 (с весом 8). Тактовые импульсы поступают на синхровходы тетрад (триад, диад) 8-14 регистра. По импульсу округления, совпадающему с первым тактовым импульсом, подаваемому на вторые входы элементов ИЛИ 15-21, осуществляется запись в регистр сдвинуто- го в сторону младших разрядов числа /(0,1, i) при наличии нуля на информационном входе. При наличии на информационном входе единицы происходит сдвиг числа cf в сторону младпшх разрядов суммирование со 180 и запись в регистре

Сдвиг числа (0,l,i) осуществляется схемно, путем соединения:

1)выходов тетрад 10-12 единиц минут, единиц градусов, единиц секунд и триады 14 десятков секунд с весами 2 с первыми входами элементов ИЛИ 15-18 соответственно, выходы которых соединены с входами сумматоров 3

, 5, 7, 6 с весом 1.

2)выхода тетрады 1I единиц минут с весом 4 с первым входом элемента

, ИЛИ 19, выход которого соединен с входом сумматора 5 с весом . ;

3)остальных выходов старших разрядов тетрад (триад, диад) 8-14 регистра со сдвигом на один разряд в сторону младших разрядов с входами двоичных сумматоров 1,3 - 7 и двоично-де- сятичного сумматора 2;

4)выходов младших разрядов диад 8, тетрад 9-11 регистра угла с входами сумматоров -4,6 следующих (младших) тетрад (триад) с весами 4,

1 (2, 1) соответственно;

5)выходов младших разрядов триад 13, 14 с первыми входами элементов ИЛИ 20. 21, выходы которых соединены с входами сумматоров 5, 7 соответст , венно, причем каждьй выход подключен к двум входам сумматора с весами , 4,

6) выходов суммы и переноса двоичных сумматоров 1,3- 7 и выхода суммы двоично-десятичного сумматора 2 с информационными входами етрад, триад диад 8- ft регистра угла,

В каждом следующем такте производится сдвиг содержимого тетрад ( триад, диад 8-14 регистра на один разряд в сторону младших и суммирование со 180° при наличии единицы на. информационном входе. При наличии нуля на информационном входе производится только сдвиг,

При наличии единицы в младшем раз- ряде тетрады ( триады, диады) производится коррекция, К содержимому следующей младшей тетрады (триады) при сдвиге добавляется чксло 5 (3), то есть в каждом такте производится деле ние на два содержимого регистра, а также коррекция. Число тактов преобразования определяется максимальной разрядностью преобразуемых чисел,

В результате выполнения данных операций содержимое регистра представляет собой сумму эквивалентов разрядов двоичного кода преобразуемого числа, выраженную в двоично-десятично- шестидесятиричном коде и округленную по существующим правилам.

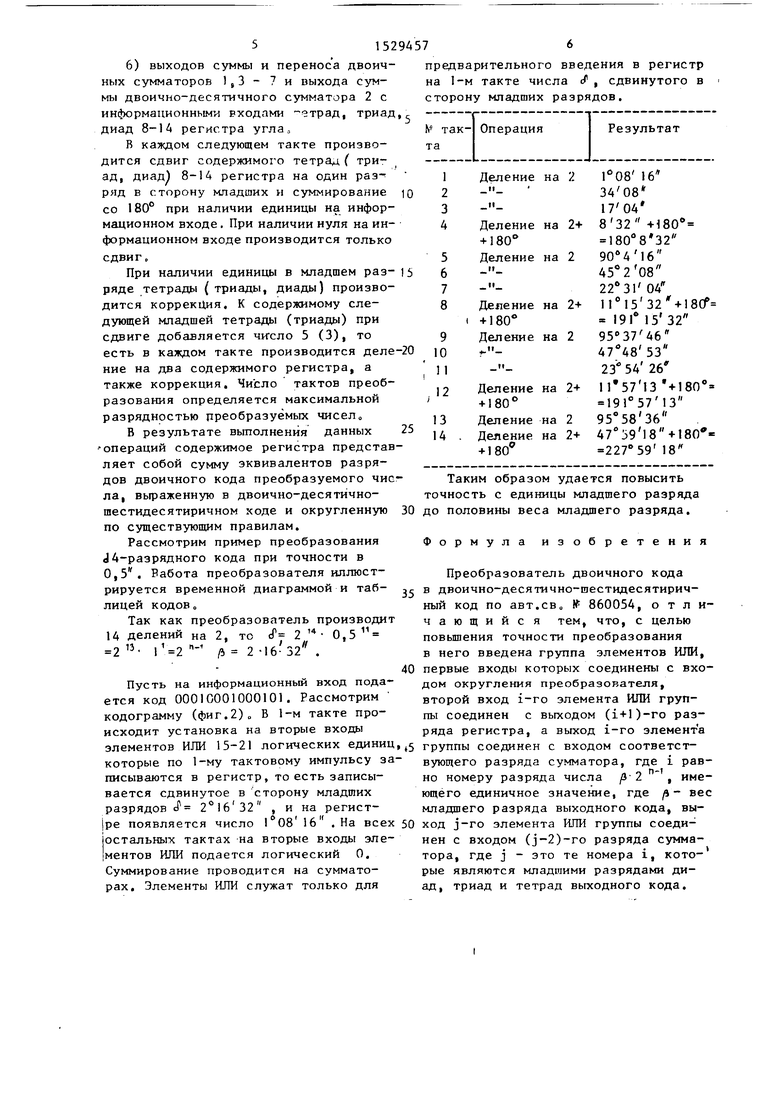

Рассмотрим пример преобразования JА-разрядного кода при точности в 0,5, Работа преобразователя иллюстрируется временной диаграммой и таблицей кодов

Так как преобразователь производит 14 делений на 2, то f 2 0,5 - Л 2-1632 ,

Преобразователь двоичного кода 35 в двоично-десятично-шестидесятиричный код по авт,св № 860054, отличающийся тем, что, с целью повьшения точности преобразования в него введена группа элементов ИЛИ, 40 первые входы которых соединены с входом округления преобразователя, второй вход i-ro элемента ИЛИ группы соединен с выходом (i-fl)-ro разряда регистра, а выход i-ro злемент а

Пусть на информационный вход подается код 00010001000101, Рассмотрим кодограмму (фиг,2)о В 1-м такте происходит установка на вторые входы

элементов ИЛИ 15-21 логических единиц,группы соединен с входом соответст- которые по 1-му тактовому импульсу за-вующего разряда сумматора, где i рав- писываются в регистр, то есть записы-но номеру разряда числа 2 , име- вается сдвинутое в сторону младшихющего единичное значение, где - вес разрядов 2° 1632 , и на регист-младшего разряда выходного кода, вы- ре появляется число 16 .На всех 50ход j-ro элемента ИЛИ группы соеди- остальных тактах на вторые входы эле-нен с входом (j-2)-ro разряда сумма- ментов ИЛИ подается логический О,тора, где j - это те номера i, кото- Суммирование проводится на суммато-рые являются младшими разрядами ди- рах. Элементы ИЛИ служат только дляад, триад и тетрад выходного кода.

предварительного введения в регистр на 1-м такте числа f , сдвинутого в сторону младших разрядов.

10

25

Таким образом удается повысить точность с единицы младшего разряда 30 до половины веса младшего разряда.

Формула изобретения

Преобразователь двоичного кода 35 в двоично-десятично-шестидесятиричный код по авт,св № 860054, отличающийся тем, что, с целью повьшения точности преобразования в него введена группа элементов ИЛИ, 40 первые входы которых соединены с входом округления преобразователя, второй вход i-ro элемента ИЛИ группы соединен с выходом (i-fl)-ro разряда регистра, а выход i-ro злемент а

I I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь кодов | 1989 |

|

SU1619402A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием известного устройства по авт.св.N 860054. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем, что в преобразователь, содержащий сумматор 1 сотен градусов, двоично-десятичный сумматор 2 десятков градусов, сумматор 3 единиц градусов, сумматор 4 десятков минут, сумматор 5 единиц минут, сумматор 6 десятков секунд, сумматор 7 единиц секунд, диоды 8 сотен градусов, тетрады 9-12 десятков градусов, единиц градусов, единиц минут, единиц секунд, триады 13-14 десятков минут и десятков секунд, дополнительно введены элементы ИЛИ 15-21. 2 ил.

Составитель M, Аршавский Редактор А.Маковская Техред М.Д1адыкКорректор С „Черни

Заказ 776П/56

Тираж 884

ВНИППИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг. I

Подписное

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-02-22—Подача