105

3. Преобразовагвпь ,по гш. 1 и 2, о тпичающийся тем, что в нем аБоично-шестиричный йреобразоватепь содержит сумматор, два эпемента И, элемент НЕ и эпрмент ИЛИ, первый вход которого соединен с выходом переноса сумматора и входом эпемента НЕ, второй вход эпемента ИЛИ соединен с выходом третьего, разряда сумматора и входом переноса cjevTMaTopa, выходы первого и BToij рого разрядов которого соединены с первым входом и входом четвертого разряда сумматора и первым входом первого эпемента .И и соответственно с вторым вхо529

дом четвертого разряда сумматора и пер вым входом второго эпемента И, вторые входы первого и второго эпементов И соединены с выходом эпемента НЕ, а выходы первого И второго эпементов И яв- (1Ч5отся соответственно первым и вторым выходами цвоично-шестиричного преобразоватепя, выход переноса которого явпя- , ется выходом- эпемента ИЛИ, а первый, второй и третий входы авоично-шестиричного преобразоватепя соединены соответствевн но с первыми входами первого и третЕ гего разрядов сумматора и вторым входом

первого разряда сумматора.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

1. ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНОШЕСТИДЁСЯТИРИЧНЫЙ КОД, оодвржатанй ц сумматоров, где Л -чиспо разрядов выходного кода, и (П -1) блоков коррекции, первый, второй и третий разрядные выходы которых явпяются информационными выходами преобразоватепя, а выход переноса -го ( 1,3,5, 6) биока коррекции соединен с входом переноса (f +1 )-го сумматора, первая группа входов j -го ( 5 1 - и ) сумматора соединена с выходами переноса (j -1)-го сумматора, вторая группа входов каждого сумматора сгоединена с информационными входами преобразоватепя, выходы группы старших разрядов всех сумматоров, кроме h -го, соединены с первым, и третьи входами соответствующих блоков коррекции, выходы мпадших разрядов всех сумматоров явпяются информапионвыми выхр дами преобразователя, выход старшего разряда И -го сумматора является информационным выходом преобрааоватепя,, о тличающийся тем, что, с депыо повышения точности и упрощения преоб.разователя, он содержит сумматор допей секунды, первый элемент ИЛИ в впеменг И, а второй и четвертый блоки коррекции содержат двоично-шестиричный преобраэсх ватепь и второй зпамент ИЛИ, первый . вход которого соединен с выходом переноса двоично-шестиричного преобразоватепя, второй вход соединен с выходом старшего разряда соответствующего сумматора, а выход второго элемента ИЛИ соединен с входом соответствующего сумматора, выходы группы мпадших разрядов сумматора допей секунды соединены с входами первого элемента ИЛИ, выход Koi oporo со&IliHeH с первым входом апемента И, второй вход которого соединен с выходом переноса сумматора долей секунды, ннфо маоиравые входы которого соединены с информадкойными входами преобразователя. i 2. Преобразователь по п. 1, о т п и(Л чающийся тем, что в нем -и .блок коррекции (кроме t 2,4) содержит сумматор, элемент И и элемент НЕ, ВХОД которого соединен с вьиигаом четвертого разряда сумматора и является выкоцом третьего разряда блока коррекции, ВЫХОД первого разряда которого соединен о ел с выходом первого разряда сумматора,вход переноса которого соединен с выходом переноса сумматора, являющегося :л выходом переноса блока коррекции, выход 0 второго разряда которого является выходом элемента И, першый вход которого соединен с выходом элемента НЕ, а второй вход элемента И соединен с выходом третьего разряда сумматора, 1тарвые входы nepBorOs второго разрядов которого соединены с г ервым входом блока коррекции, второй вход которого является первым входом третьего разряда сумматора, вторые входы второго и третьего разрядов которого, а также первый вход четвертого разряда сумматора соединены с третьгим входом блока коррекции.

,

Изобретена относится к автоматике в вычиспитепьной технике и предназначено дпя преобразования двоичного кода угпа в двоично десятичный код градусов, минут, секунд.

. Известен преобразоватепь двоичного кода Б пвоично-лесятично-шестидесятирич ный код, содержащий регистр, состоящий из тетрад, триад и диад, причем синхровходы регистра соединены с входом тактовых импупьсов преобразоватепя, двочяйо-дееятнчные сумматоры, выходы которых соедийень с соответствующими входами тетрад, триад и диад, выходы тетрад j триад и диад соединены соответственно с входами соответствующих сумматоров. Выходы переноса сумматоров мпадших разрядов тетрад, триад и диад соедиН|ены с входами соответственно.

Процесс преобразования двоичных ч ееп и двоинно-десятично-шестидесятиричкые представпяет собой прсгаедоватепькые операции депения на два содержимого двоично-десятичного регистра и суммирования с числами вида о( j . 180 в каждом такте, где oi - значение « -го разряа& преобразуемо1хэ двоичного чиспа. В 5 езупьтате выпопиения даннык операций содержимое двоично-десятичного регистра иредйтавпнет собой сумму эквивапентов разрядов двоичного кода преобразуемого ч-йспа, выраженные: в двоично-десятичношестидесятиричном коде l .

Недостатком этого преобразоватепя явцяется низкое быстродействие, так как Преобразование осуществляется в течение постулпекия и тактовых импульсов, где

П - количество разрядов входного кода. Деление на 2 осуществляется с точностью до 1 с„ Максимальная суммарная погрешность преобразования составляет 6,23 с.

Наиболее близким к предлагаемому по

техничесжой сущности и схемному построению является преобразоватепь двоичного кода в двоично-десятичный код, содержащий группу сумматоров и группу блоков

десятичкюй коррекции, входы которых соедине51Ы с выходами соответствующих сумматоров, а выход переноса бпока десятичной коррекции соединен с входом переноса «сумматора соседнего старщего десчтичного разряда 2j.

Недостаток известного преобразователя

состоит в НИЗКОЙ точности и сложности блоков десятичной коррекции.

Цель изобретения - повышение точнооти и упрощение преобразоватепя.

Поставленная цепь достигается тем, что в преобразователе двоичного кода в д Боично-десятично-шестидесятиричный код, содержащем Ц сумматоров, где П - чиспо разрядов выходного кода, и ( Ц-1) блоков коррекции, первый, второй и третий разрядные выходы которых являются информационными выходами преобразователя, а выход переноса i-го ( i 1,3,

5,6) бпока коррекции соединен с входом переноса ( « +1 )-го сумматора, первая группа входов j -го ( j 1 Г ) сумматора соединена с выходами переноса ( j-l)-ro сумматора, вторая группа входов 5;аждого сумматора соединена с ин формационными входами преобразоватепя,

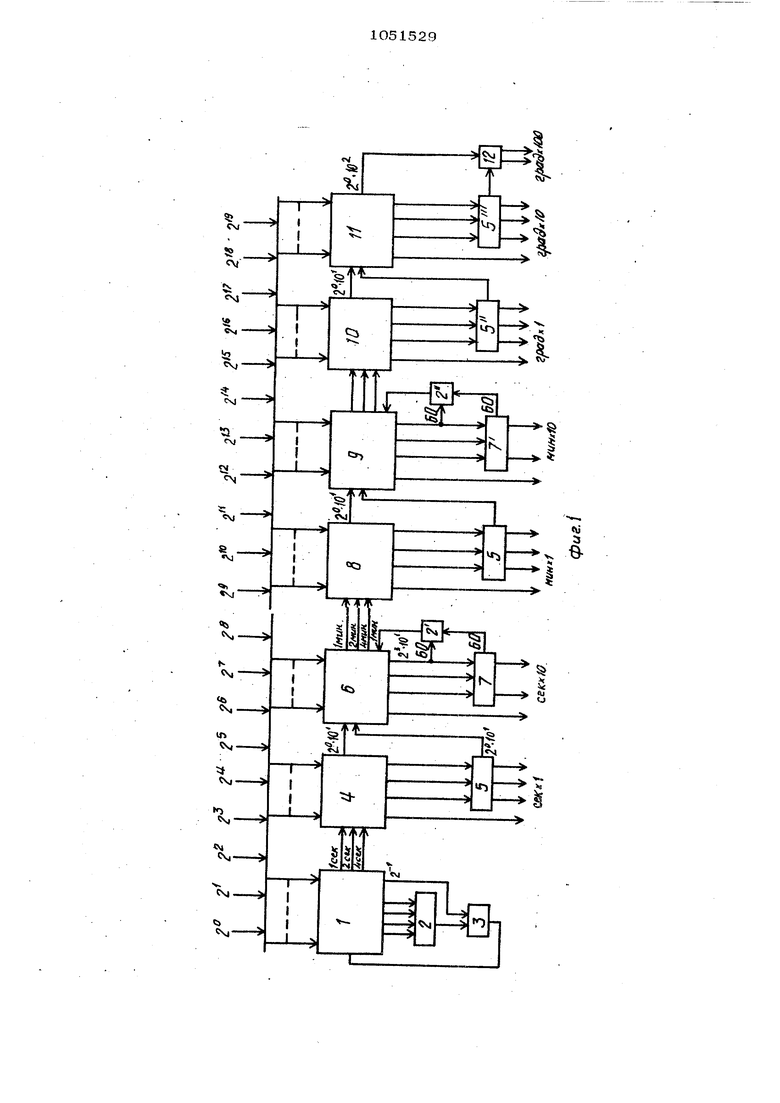

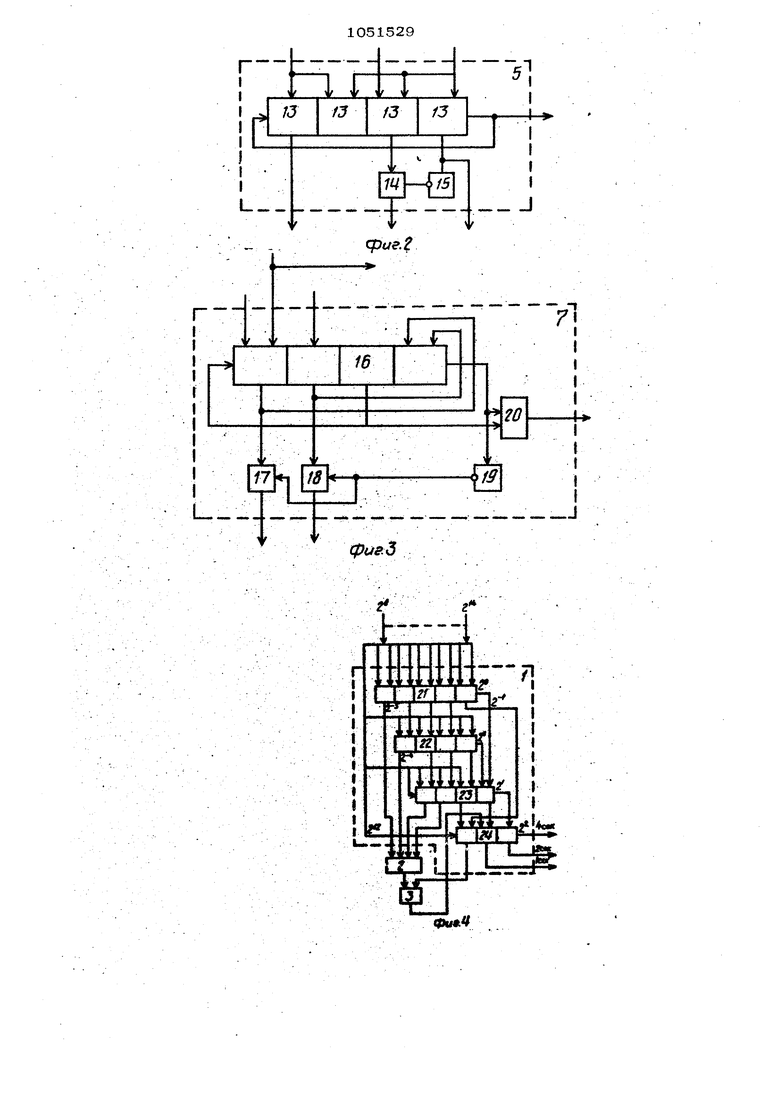

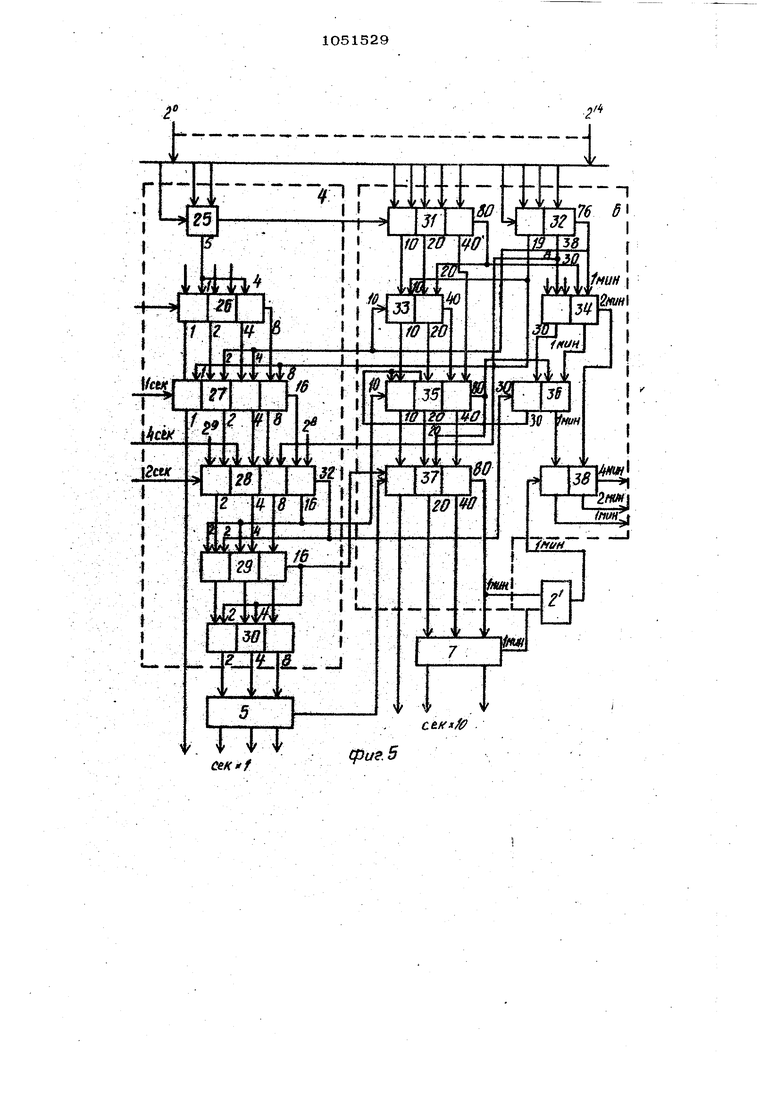

выходы группы старших разрядов всех сумматоров, кроме Ц- -го, соединены с пе первым,вторым и третьим входами,соответствующих блоков коррекции, выходы мпадших разрядов всех сумматоров являются информационными выходами преобразоватепя, выход старшего разряда И -го сумматора явпяется информационным выходом преобразователя, он содержит сум матор допей секунды, первыГ элемент ИЛИ и эпемент И, а второй и четвертый бпоки коррекции содержат двоично-шестеричный преобразоватепь и второй эпемент ИЛИ, первый вход которого соединен с выходом переноса двоично-шестиричного преобразователя, второй вход соединен с выходом старшего разряда схэответст-|Вуюшв1Х) сумматора, а выход второго эйе мента ИЛИ соединевГ с входом первой группы входов соответствующего сумматора выходы группы младших разрядов суммато- ра допей секунды соединены с входами первого элемента ИЛИ, выход которого , соединен с первым входом эгевмента И, второй вход которого соединен с выходом переноса сумматора допей секу иды, информационнью входы которого соединены с информационными входами преобреиэоватепя. Кроме того, в преобразователе -и блок-коррекции (кроме ,4) содержит сумматор, элемент И и эпемент НЕ, вход которого соединен с выходом четвертого разряда сумматора и явпяется вы ходом третьего разряда бгюка коррекпш, выход первого разряда которого соедйээв с выходом первого разряда сумматора, переноса которого соедивен с выходом переноса сумматора, являющегося выходом переноса блока KoppeKUtra, выхоа второго разряда которого явпяется выходом рпемента И, первый вход которого соединив с выходом элемента НЕ, а второй вход элемента И соединен с выходил третьего разряда сумматора, первые выходы первого и второго разрядов которого соединены с первым входом бгюка Kojq ций, второй вход которого явпяется перш ьходом третьего разряда сумматора, вторые входы второтю и третьего разрядов которого, а также первый вход четвер- того разряда сумматора соединены с Jтретьим входом блока коррекции..:, Т1ри этом в преобразователе двоичвошестиричный преобразоватепь содержит сумматор, два элемента И, элемент НЕ И ИЛИ.первый вхм которого соедв-ч нен с выходом переноса сумматора в вяо ом элемента НЕ, второй вход эпемента ИЛИ соединен с выходом третьего ряда сумматора и входом переноса сумматора, выходы первого и второго разрядов которого соединены с первым входом в входом четвертого разряда сумматора в tiepBbiM входом первого элемента И и соответственно с вторым входом четвертого разряда сумматора и первым входом второго элемента И, вторые входы первого и второго элементов И соединены с выходом элемента НЕ, а выходы первого в второго элементов И явпяюто соответственно первым и вторым выходами двоичношестиричного преобразователя, выход переноса которого является выходом эл«(.ч мента ИДИ, а первый, второй и третий входы двоично-шестирич ного 1феобразователя соединены соответственно с первыми входами первого и третьего разрядов румматора и вторым входс«{ nepieoro разряда сумматора. На фиг. 1 пршедена функивовапьная схема преобразователя двоичного кода градусов, минут, секунд в двоичвог-десятично-шестидесятирвчный код} на фиг. 2 бпок-схема бловса ко1Ч екцив; на фиг. 3 блок-схема двовчво-шестврвчного преобразователя; ва фвг. 4 - один вз. вариантов исполнения схемы соединения сумматора долей секунды; на фвг« 5 - то же v сумматора единиц и йесятков секунд; Hia 4«г. 6 - то же., суммато{ единиц и десятков минут; на фиг. 7 - .то жв сумМаторов едннви, десятков, сотен градусов, Преобразоватепь двоичного кода граду сов, минут, секунд в двовчно-десятвчношестидесятврвнный код сОдержвт сумматор 1 долей свкущы, выходы сумматора 1, имеющие веса (2,2,,2) секунды соединены с входами апемента ИЛИ 2 выход которого соединен.с одним входом элемента И 3, второй вход которого сое диве в с выходом сумматора с суноы, формирующего экан.енве 2 , выход элемента И 3 соединен с вторым входом сумматора 1 допей сшсуноы, мируйщего звачен аепых секунд. Выхода сумматора 1 долей секунд,, имеющие веса целых секунд 2, 2, 2 (1, 2,4 с) соединены с первыми входами первого сумматора {единиц секунд) 4, выхода которого с весами (2, 2, 2)iJ xlO соадинены с входами блока 5 кор рекцин, выход сумматора 4 с весом 2 Ю и выхош 1 блока 5 коррекцвв соединены с выходными шинами, а выход сумматора 4 едишшсекунд с весам 2 1О и выход переноса блока 5 Kopi рекции соединены с входами второго / сумматора {десятков секунд)6. Выходы .51 второго сумматора в с весами (2, 2, 2) р 10 соединены с входами двоичношестиричного преобразом1те 1Я 7. Выкоды STopdro сумматора 6, имеющие значения минут (if 2, 4 мин) подключены к входам третьего сумматора (единиц минут) 8j выходы которого с весами (2 2 , 2) соединены с входами бпока 5 коррекции -, а выход сумматора 8 с весом 2 10 и выход переноса бпока 5 кор: рекции соединены, с вход1эми четвертого сумматора (десятков минут) 9, выходы которого с весами (2, 2, 2) 1О соединены с входами двоично-шестиричного преобразоватепя 7 , выходы сумма. тора 9s ИФ №Ющие значения 1 граД,1 2 гра 4 град, соединены с первыми входами . пятого сгумматора (единиц градусов). Ю, выходы которого соединены с входами бпюка 5 кор{дакции (единиц градусов). Выходы cyiMMaTOpa 10 и бпока 5 коррек ции с весом 2° 1О соединены с вхог дамй шестого сумматора (десятков граду сов) 11, выход перецопнения которого соединен с входами блока 5 коррекции и с входами седьмого сумматора (сотен градусов) 12, Блок 5 коррекции содержит (фигв 2) сумматор 13, входы которого явпяются В5содами блока коррекции с весами (24 2, 2) .. где К номер тетрады преобразования. Выходы первого и четвертого разрядовсуммато|90В ГЗ явпяются разрядными выходами (выхоцйМй сумм) блока коррт кцпи с вес Ш2: 2. 10«-.. Выход третьего разряда сумматора 13 соединен с входом элемента И 14, второй вход которого соединен с выходо эпемента НЕ 15, вход которого соедине , с выходом, четвертого разряда сумматор 13« Выход элемента И 14 является рйарядньш Бьтодом бпока кор-рекиии с весом . Выход переноса сумматора 13 соединен с входом первого раэряна cyiviiviaTopa 13 и является вь{ходом неэешса бпока коррекции с весом , ю.;- . Двойчио-шестйршный преобразоватепь 7 содержит (фиг. 3) сумматоры ЗГб, входы которых явпяются входами двоично-шестирич ного преобразователя t весами (2, 22, 2 ) lO . Выходь первого и второго разрядов сумматоров 16 соединены с взводами четвертого раз ряда сумматора 1 б и с первыми входам элементов И 17 и 18 соответственно, вторые вхрдь которых соединены с EWвыхойом элемента НЕ 19, вход которог соединен с выходом четвертого разряда 29. ® сумматора 16 и входом эпемеита ИЛИ 20. Cyi iMaTQp 1 допей секунды содержит (фиг.4) сумматоры 21-24. Сумматор 4 содержит (фиг, 5) су1у1маторы 25-30. CvtvJMarop 6 десятков секунд содержит cjTs4MaTopb 31 - 38. Сумматор 8 единиц минут содержит (фиг. 6) сумматоры 3943, Сумматор 9 десятков минут соцер жит сумматоры 44-49. CyMNfaTop 10 единиц градусов содержит (фиг. 7) сумматоры 5O-S2, Су гматор 11 десятков градусов содержит сумматоры 53-55. Веса поступающих на вход преобразователя разрядов кода можно выразить соотношением W-1 Ол АЛЛ где И копичество разрядов п еобра -. зуемого числа; И1 - порядковый номер разряда входного кода. Рассмотрим работу преобразователя при условии, что количество разрядов преобразуемого числа П 20. Веса двадцати разрядов входного кода, их округленные значения в виде градусов, минут, секувд ,и значения погрешностей приведены в табл. 1. В. табл. 2 приведекьг окрз гпенные значения весов разрядов входко} о кода и представленные в виде степеней 2, а также абсолютные значения погрешностей округпекия. Разряды входного кода, содержащие допй секундя, поступают йа с адматор долей секунды. Сумматоры осуществляют суммирование погрешностей в порядке их возрастания. Первый разряд сумматора 21 осуществляет суммирование значении 0,03125 2 погрешностей, бодёржащихся в значениях разрядов входного кода с весами 2 и 2°, второй разряд сумматора 21 осуществляет суммирование значения 0,0625 2 погрешностей, содержащихся в значениях разрядов входного кода с весами 2 и 2 и значение переюса из первого разряда сумматора 21 и т.д. в соответствии со значениями поправок из табп. 2. Результаты суммирования, а шленно, значения 2 , 2, 2 , поступают на первые вхоаы cyt/iMaTopa 22, на вторые входы которо:пэ поступают разряды входного кода 2 , 2 , содержащие значения погрешностей 2, 2 5, 2, 2,, Резупьта1Ъ1 с ммирования с весами , 2, 2 и выходы переноса сумматоров 21 и 22 поступают на входы сумматора 23, который суммирует их значения со значениями разрядов, входного кода 2, , содержащие значения по грешностей 2 , 2 . 2. Сумматор 24 осуществляет суммирование значений выходов сумматоров 21 и 23, имеющих значения 2 , 2 и 2 и значения погрешности 2, содержащейся в разряде входного кода с весом 2. Конечные результаты суммирования с весами 2 , 2, 2, 2 с первых разрядов сумма I торов 21-23 и второго разряда суммато ра 23 поступают ни элемент ИЛИ 2, а с выхода элемента ИЛИ 2 - на вход элемента И 3, на второй вход которого поступает значение 2 с выхода первого разряда сумматора 24. Таким образом, элемент И 3 формирует значение погрешности 0,5 сек, которое округляется до целой секунды и поступает на вход второго разряда сумматора 24. Таким образом, сумматор 24 фсэрмирует значения целых единиц секунд 2® « 1 с, 2 2 с 2 в 4 с, которые поступают затем на входы сумматоров ецивиц секунд 4. Из табп. 2 видно, что суммарное значение погрешностей не превышает целого числа секунд - 5.,. Разряды входного кода, содержащие единицы и десятки секунд, поступают на сумматоры (единиц и десятков секунд 4 и 6. В табп. 3 приведен вариант разложения значений секунд для суммирования На сумматор 25 портупаизт значения входных разрядов кода, содержащие в paa пожен и число 5. Результат суммирования (сЗ9.«ма), равный 5, поступает на первый и третий разряды сумматора 26 а значение переноса сумматора 25 поступ ет на сумматор 31, На остальные входь сумматора 26 поступают значения разрядов входного кода. Результаты суммирования - 1,2,4,8 - Поступают на первые входы cjMMaTopa. 2t, на вход переноса и на входы которого поступают значения переноса 1 с из сумматора 1 допей секунды и значения , получившихся на выходах сумма1Ч ра 32, так как одним из слагаемых сумматоров десятков с&кунл является число 19, поскольку оно три раза встречается в разложении значений секунд (табя. 3). Результат суммирования на выходе младшего разряда сумматора 27, равный 2° 10° поступает на вмход пре образователя, а результаты суммирования ра выходах старших разрядов сумматора . .27 и значение переноса сумматора IS поступают на первые входы сумматора 128, на вторые входы которого поступают значения переносов 2 и 4 с, сфорг миро ванные сумматором 1 допей секунды, 1и значения 2 и 16 разрядов входного кода 2 н 2°. Значения единиц секунд, получившиеся в результате суммирования на сумматоре 28, поступают на входы сумматора 29j а значения десятков се;кунд, получившихся в результате суммирования единиц секунд, поступают на сумматоры 6 десятков секунд. Значения выходов старшего разряда сумматора. 28 (2,4,2) поступают на входыпервого и второго раэгрядов сумматора 29, а значения десятков (1О,30) поступают на входы сумматоров 35 и 36 десятков 1секунд, Выходы сумматора 29 поступают на входы сумматора ЗО, значения сумм которого поступают на входы блока 5 коррекции, реализующего таблицу истинности, приведенную в табп. 4. Значения сумм блока 5 коррекции (2, , 2) -10° поступают на выходы преобразователя в качестве единиц секунд, а значение переноса 2° - Ю блока 5 коррекцнег и значение 2 1О переноса сумматора 29 поступают на входы первого разряда сумматора 37. Пере эс сумматора ЗО равен нупю, так как максемалыюе значение сумм сумматора 29 равно 2-3 + 42 + 8« « 22, а ва входы сумматора 30 поступает значение 22 - 10 12, поскольку значение 2 1О переноса сумматора 29 поступает на сумматор 37. Разряды входного кода, содержащие десятки секунд, в соответствий с табп. 3, поступают на входы сумматора 31 (Ю, 2О, 4О) н сумматора 32 (19, 38). Результаты & суммирован суммато ров 31-32 Ю с i 5 30 с поступают на входы сумматора 33, а значение суммы старшего разряда сумматора 32, равное ЗО, поступает на вход младшего разряда сумматора 34, на другие входы которого поступают значения разрядов входного кода, содержащие значения ЗО. На входы второго разряда сумматора 34 поступают значения сумм и переносов, 6О С 1 мин. Сумматоры 3536 ocjylцecтвnяют суммирование десятков секуна. Прв наличии переноса сумматоров Р 6О с часть значения, равная 1 мин, поступает на входы сумматоров с весами единиц минут. На выходе младо швго разряда сумматора 7 формируете значение 2®-Ю с, поступающее на

выход пр образоватепя, а значения сумм двух разрядов сумматора 37 и часть значения переноса сумматора 37 , поступают на входы aeoiWHoшестиричного преобразоватепя 7.

Таблица истинности двоично-игвстиричного преобразователя 7 приведена в

табп. 5..

Двоично-шестиричный преобразователь

7 формирует значения десятков секунд (24 2) 10 поступающие на выходы блока, и значение переноса, равное 1 мин KOTopqe поступает на элемент ИЛИ 2 . На второй вход элемента ИЛИ 2 посту пает часть значения переноса сумматора 37,. равная 1 мин. Эти значения не могут присутствовать одновременно, так как максимальное значение общей суммы сумматора 37 равно 110, и значения сумм 20, 40 и 80 не могут присутствовать одновременно. .

Значение 1 мин с выхода элемента ИЛИ 2 поступает на -первый вход сумматора 38, на второй вход которого поступает значение 1 мин с выхода второго разряда сумматора 36. На вход второго разряда 38 сумматора поступает значение 2 мин, сформированное на выходе переноса сумматора 34.

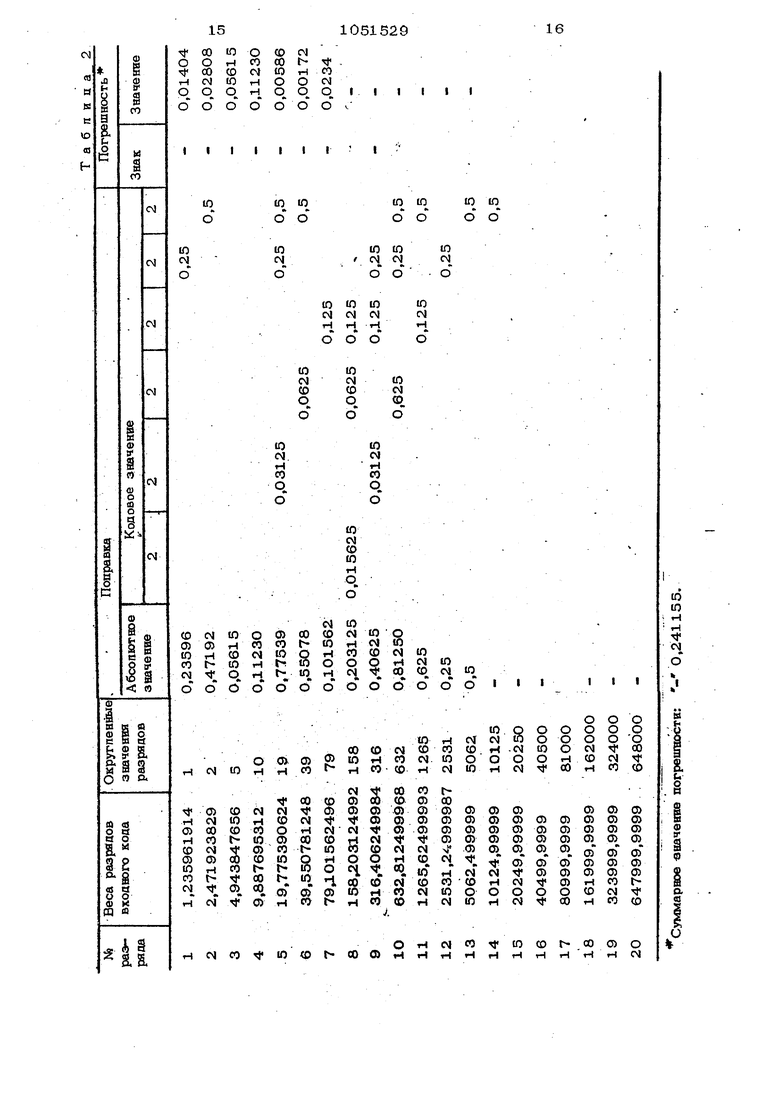

. Сумматор 38формирует значения переносов 1, 2 и 4 мин, поступающие на входы сумматора 8 единиц минут. Наибольшее значение суммы секунд не превышает .ЗОО б.Разряды входного кода, содержащие еаинииь и десятки минут, и их разложения дпя суммирования, приведены в габр;. 6.

На вхо№1 сумматора 39 поступают значения 5, содержащиеся в разрядах входного кода. Результат суммирования этого сумматора, равный 5, поступает на входы первого и третьего разрядов сумматора 4О, а значение переноса сумматора 39, равное 1О, поступает на-вхо сумматора 44 десятков минут. На входы сумматора 40 поступают кроме того значения 1,2,4, содержащиеся в разрядах входного кода. Сфо1:а {ированные сумматором 40 значения 1,2,4,8 поступают на сумматор 41, на входы которого поступают также значения переаосов 1 и 4 мин, сформированные сумматором 38

и значения 2 и 8 содержащиеся в разif it рядах входного кода 2, 2. Выход

мпадшего разряда сумматора 41 - 2®я ilO поступает на выход креобразоватепя, а выходы остальных разрядов суМ матера 41 и часть его переноса 1О

поступают на сумматор 42 на младший разряд которого поступает, кроме того, значение 2 мин, сформированное;сумматором 38. Выходы сз мматора 42 и часть

его переноса :10, поступают-tia входы сумматора 43, который форхгирует значения 2,4,8, поступавшие на блок 5 коррекции, формирующий значения единиц минут (2, 2, 2) . 10 , которые выда0 ются на выход преобразователя и значение 10 мин (2, 10 ), поступающее . на вход переноса сумматора 49. Части переносов сумматоров 41 и 42,равные 10, поступают на вход сумматора 46.

Сумматоры 44, 46, 48,:49 и-45

осуществляют последовательное суммирование десятков минут. По мере возникновения переносов, больших 60,.часть переноса, равная 60, поступает на входы

0 сумматора 47, формирующего значения .единиц градусов, возникш1те в результате суммирования десятков минут, а часть переносов, меньшая 60, -продолжает суммироваться на сумматорах десятков ми5 нут.

Значение выхода младшего разряда сумматора 49 2 --10 поступает на выход преобразователя, а выходы дЬух других ра.зрядов сумматора 49 и часть значения его переноса 60 поступают на двоично-шестиричный преобразователь 7, который формирует значения (2,2)f X 10 десятков минут, пострта1бш.ие на выход преобразователя и зне.чение переноса, pijBHoe 60, поступающее на вход элемента ИЛИ 2, на второй вход которого поступает значение переноса, равное 60, с выхода переноса сумматора 49.

Одновременно эти значения присутствовать не могут, так как максимальное

значение общей суммы на входах сумматора 49 равно 100. Значение 1 град, с выхода элемента ИЛИ 2 поступает на вход второго разряда сумматора 45, первый разряд которого осуществляет сум- миро на ние значений 30, содержащихся в значениях разрядов входного кода 2 и 2. Результат суммирования (ЗО) поступает на.входы первого и второго разрядов сумматора 48. Выход суммы и

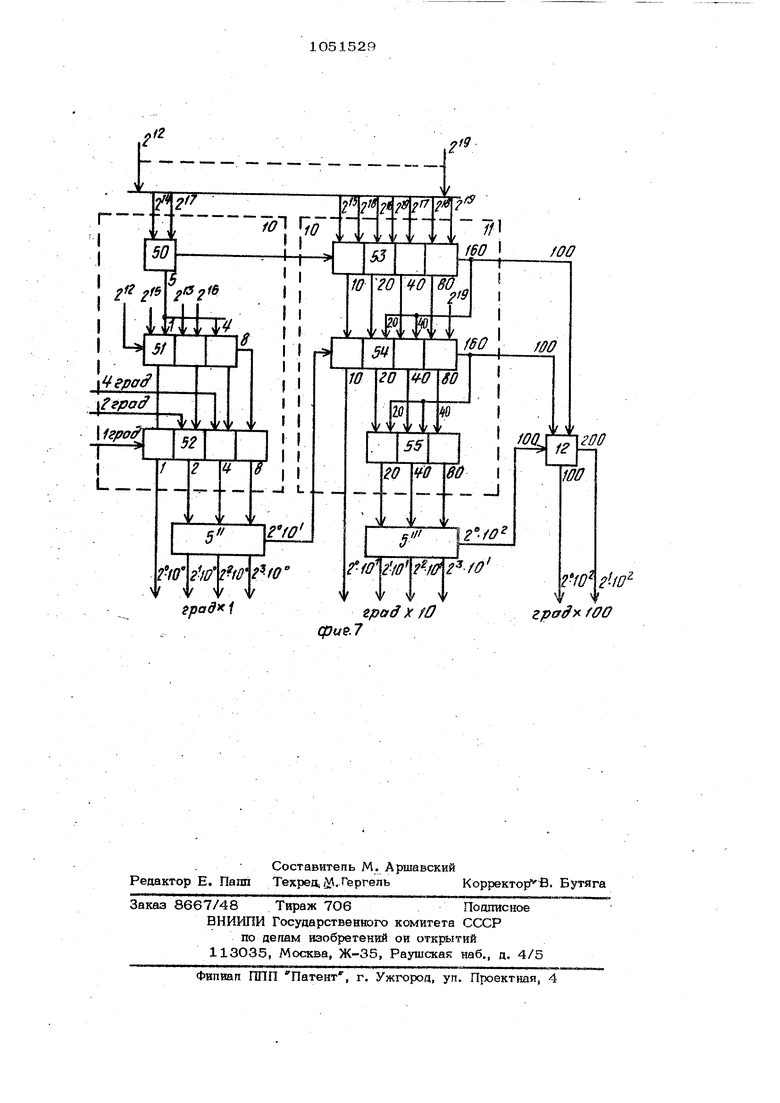

0 переноса второго разряда сумматора 45 поступают Hia входы сумматора 47, на вторые входы первого разряда усумматора 47 поступают значения переносов, равные 60. Сумматор 47 форшир тот зна5 чения 1, 2 и 4 град, поступающие на сумматор 10 единиц градусов, так как наибольшее количество суммирующих минут не превышает 25О, что равно . Разряпы входного кода, содержащие еди1ШиЫ| десятки и сотни градусов и их раэпожание дпя суммирования, щ иввдены ,в табл. 7.-. На вхопы сумматора 5 О поступают аначения.б, содержащиеся в разрядах входного кода результат суммирования которого, равный 5, поступает на входы пер вого и второго разрядов суь матора 51, на другие вхошы,- сумматора 51 поступа ют значения 1,2 и 4 содержащиеся в разрядах входного кода, Вьпсоды суммато ра 51 и значения переносов 1, 2 и 4град.сформированнЬю сумматорами 47, поступают на входы сумматора52.Максимальная общая сумма на вхосГах сумматора 51 не превыщает значения 11, . так как второй вход старшего разряда сумматора 51 не используется. А nocsom ку сука«арное значение переносов flB.cyw Матора 9 десятков минут не может 1февышать 4 , максимальная общая сумма сумматор 52 не может превьтшать значения 15, т.е. перенос cyvtMalropa 52 равен нулю. Результат суммирования в младшем разряде сумматора 52, равный 2 10 поступает на выход преобразователя, а результаты суммщювания в его .ставших разрядах поступают на входы блока 5 |Коррекп1 И, кото1и 1й формирует з ченвя ,{2, 2, 2) 1О°, поступающие на преобразователя, и зшчение перенос 2. Ю, поступа1ощве ва вход сумматор 54, сумматор 53. осущеегвпйет суммирование значений десятков градусов, содержащихся в разрядах входвогр кода. Сумматор 54 осуществляет с п мврованй значега1й выходов сумматора 53 и значения 8О, содержащегося во входном разряде 2 , значения переноса вэ суммвто{юв 1О единиц градусов;в части значения перенос сумматора53, меш шей 1ОО. Части значений переносов сумматоров 53 и 54 равные 1ОО, поступают на входам. суммато 12 сотев. Выход .младщего разряда сумматора 54, равный 2 1О , nocTyinaeT на выхо преобразователи, а результаты суммирования остальных разрядов сумматора 54 и часть его переноса, меньшая 1ОО, иоступают на входы сумматора 55, исходы которого поступают на входы блока 5коррекции. Значение переесса сумматора 55 равно нулю, так как максимальная общая сумма сумматора 53 равна 270, максимальная общая сумма: сумматора 54 равна 26О (270-1ОО-ИО + 80), а на входы сумматора 55 поступают значб ния, сумма которых не превышает 150 (260-1О-1ОО). Сформированные блоком 5 коррекции значения сумм (2, 2, 2) -ю посту пают на выходы преобразователя, а значение переноса, равное Z 1О, посту пает на вход сумматора 12 сотен, кото Армирует значения 2/ 10, К 1О % поступающие ш выходы преобразователя. В преобразователе ij время преобразования определяется разрядностью входного кода, так как вропесс преобра-. зования осушествлиется при последовательном поступлении входного кода в частотбй следования тактовых импульсов. Максимальное время сукшврованвя определяется суммарным временем задержки последовательно соеднюнных четырехразряпного двовчво-десятвчного сумматора дес;нтков градусов в сумматоров сотен градусов 2 6 2 - время задержки одного суммагдегора. Интервал времени между двумя тактовыми импульсами составит t рег Считая €pef. , получаем, что i«r3t;i7 Общее время преобразования преобрезО вателя составит t nt 20-t - . В предлагаемом преобразователе время прёо зования определяется времеяем задержнв последовательно соедвшввых одноразрядных сумматоров,а имен1аю: 35МА 3S V гбМ41 Ч5ММ 55М 2 3(2ИОГ15 )7)ЧиЛИ V При етом: ээм 1 время задержки сумматоров 21-24; + ii(n) - время задержки сумматора Ij SM4 время - задержки сумматора 28; 9М6 Ч -время задержки сумматора 37; + 2t, -время задержки су матора 34; -врек{Я задержки сумматоров 41-43; 10 в t - время задержки сумматоров 49, 45-47; «31 - время эадерхжи сумматора 52} I1-ГИ / -время задержки сумматоров 54, 55; -время . задержки сумматора 12;« i, Р задержки бпо. . . ка 5 коррекции: J.ЛП «1 ЗЙ-бТТ И время задержки преобразователя 7, откуда tii-(10+10+54-8+6+3+7+1 ).tV + t...+ / л Л, .«-- +6(4€ +t,j,)+2t SOtV +iAM + r74tC +7t1« + + 24-г +6t,i, -H2t(,, . Учитывая, , считаем приближенно, что i/ Э

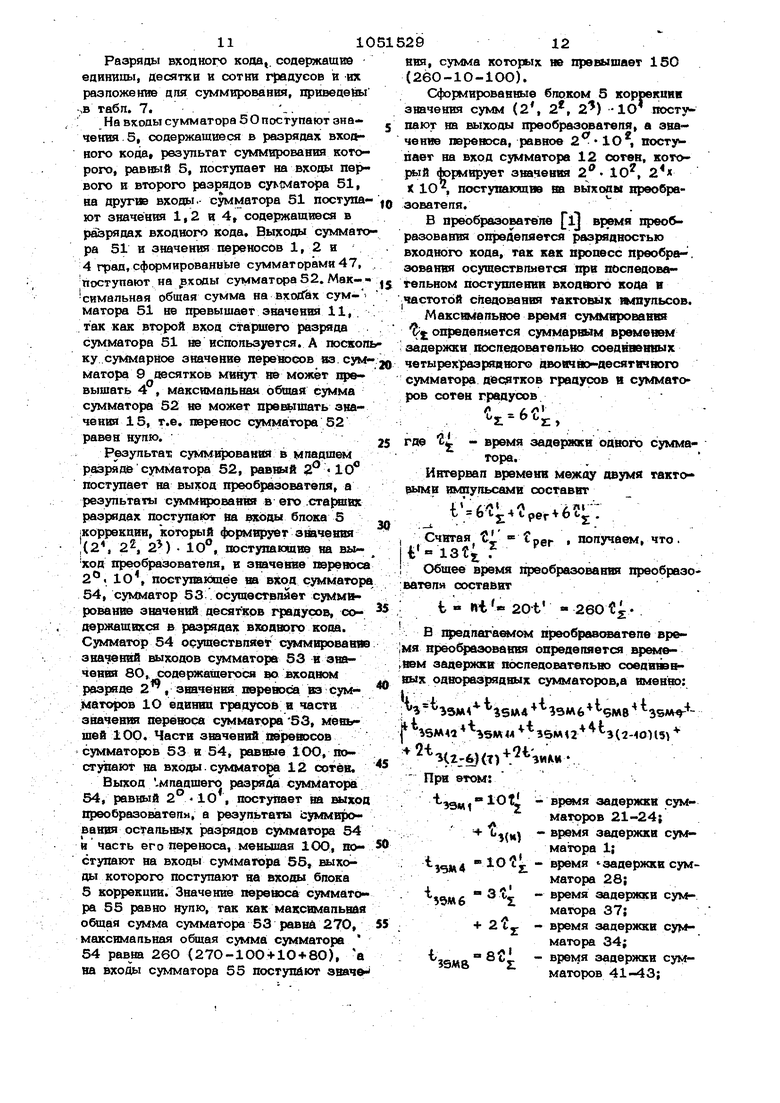

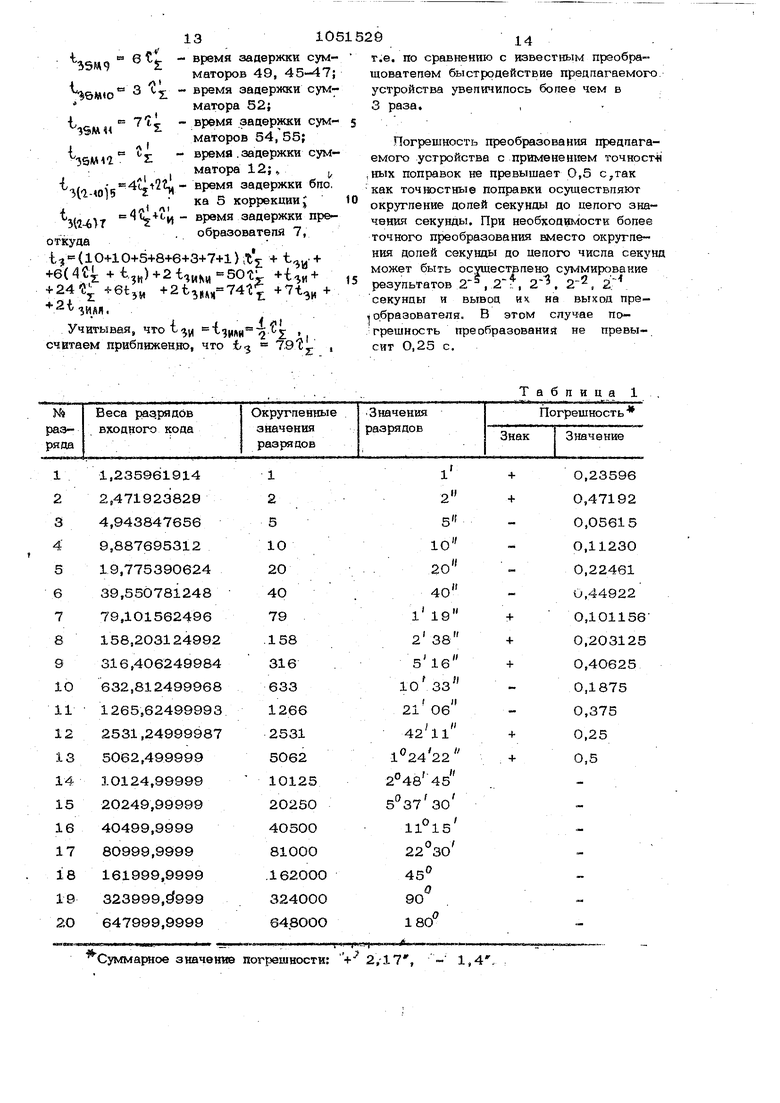

Суммарное значение погрешности: + 2,, - 1,4,

Таблица 1 614 т.е. по сравнению с известным преобращоватепем быстродействие прецпагаемого. устройства увепичйпось бопее чем в 3 раза. Погрешность преобразования предлагаемого устройства с применением точност-н ных поправок не превышает 0,5 с.гак как точностные поправки осуществляют округление долей секунды до целого значения секунды. При необходимости бопее точного преобразования вместо округления долей секунды до целого числа секунд может быть осуществлено суммирование - 0-2 результатов 2 , . , секунды и вывод ич на выход преобразователя. В этом случае погрешность преобразования не превысит О,25 с.

1 1

1 1 1

1

1

Таблица 4

Таблица 5

1 1

Г

105IS29

19

I Габпииа в

20

сек Iff

2 ttUH f CpuS.6 Htffffff

1 cpus.7

грсг fffO

tpaff )( fO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , 2, Авторское свидетепЬство СССР по заявке № 3406628, Kn.QO6 F 5/02t О2.О2.82... | |||

Авторы

Даты

1983-10-30—Публикация

1982-07-05—Подача