тично-щестидесятеричный или в двоично-десятичный код. Поставленная цель достигается за счет того, что в преобразователь кодов, содержащий сумматоры 1-7, регистр 33, состоящий из диады 14 и тетрад 19-20 и двоично-десятичного сумматора 8, дополнительно введены двоично-десятичный сумматор 32 младших разрядов, состоящий из двоично-десятичных тетрад 9-13, коммутатор 26, элементы И 21-24 и элемент НЕ 25. 2 табл., 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности преобразования двоичных кодов с произвольными весами старшего разряда в двоично-деся- (Л с: о с& о ГС

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобра- зователей.

Цель изобретения - расширение функциональных возможностей преобразователя за счет обеспечения возмож- ности преобразования двоичных кодов с произвольными весами старших разрядов R в двоично-десятично-шестидесяте ричный код или в двоично-десятичный код.

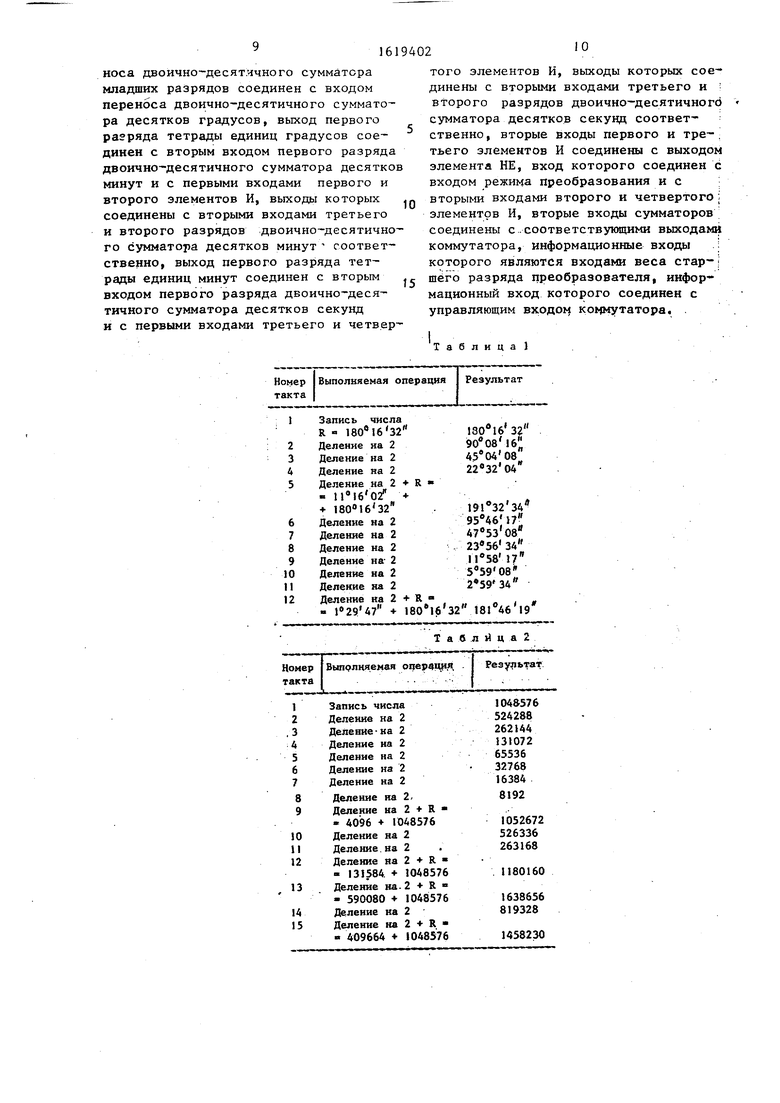

На фиг.1 представлена блок-схема предлагаемого преобразователя; на фиг.2 - кодограмма работы преобразования: а) 12-разрядного кода с весом старшего разряда R и 180е1б 32 в двоично-десятично-шеетидесятеричный код и

б) 15-разрядного кода с весом старшего разряда R 104°85 76я в двоично десятичный код.

Преобразователь кода содержит сум- матор 1 сотен градусов, сумматор 2 десятков градусов, сумматор 3 единиц градусов, сумматор 4 десятков минут, сумматор 5 единиц минут, сумматор 6 десятков секунд, сумматор 7 единиц цекунд, двоично-десятичный сумматор 8 десятков градусов, двоично-десятичный сумматор 9 единиц градусов, двочно-десятичный сумматор JO десятков минут, двоично-десятичный сумма- тор И единиц мииут, двоично-десятичный сумматор 12 десятков секунд, двоично-десятичный сумматор 13 единиц секунд, диады 14 сотен градусов, тетрады 15-20 десятков градусов, еди- ниц градусов, десятков минут, единиц минут, десятков секунд, единиц секунд, элементы И 21-24, элемент НЕ 25 и коммутатор 26.

Входы сброса тетрад соединены.с входом 27 начальной установки, синхро- входы - с входом 28 тактовых импульсов преобразователя. Вход 29 режима

задает реализуемый закон преобразования, вход веса старшего разряда 30 обеспечивает возможность параллельной подачи этого кода, через информационный вход 31 преобразователя подается последовательный входной код младшими разрядами вперед. Двоично-десятичные сумматоры 9-13 в совокупности образуют двоично-десятичный сумматор младших разрядов 32. Тетрады 14-20 в совокупности образуют регистр 33.

Преобразователь работает следующи образом.

По импульсу начальной установки тетрады 14-20 устанавливаются в исходное положение. На входе преобразователя 29 устанавливается логическая 1, если преобразователь работает в режиме преобразования двоичного кода с весом R старшего разряда в двоично-десятично-шестидесятерич- ный код, и логический О, если преобразователь работает в режиме преобразования двоичного кода с весо старшего разряда R в двоично-десятичный код. На входе 30 коммутатора 26 подаются разряды числа R, представленного в выходном коде. Преобразуемое двоичное число последовательным кодом младшими разрядами вперед, тактируемое тактовыми импульсами, поступает на информационный вход 31 преобразователя. Тактовые импульсы поступают на синхровходы диады 14 сотен градусов, тетрат 15- 20, При наличии единицы на информационном входе 31 коммутатор 26 открыт и число R попадает на сумматоры 1-7, затем в двоично-десятичные сумматоры 8-13 и записывается в регистр 33. При наличии лидирующих нулей на информационном входе коммутатор 26 закрыт и в регистр 33 записывается число О, В последующих тактах преобразования производится сдвиг содержимого диады 14 и тетрад 15-20 в сторону младших разрядов и суммирование с R при наличии единицы на информационном входе 31. При наличии нуля на информационном входе 11 проис ходит сдвиг.

Сдвиг содержимого диады J4 и тетрад 15-20 осуществляется схемно путем соединения:

1)старших разрядов диады 14, тетрад 15-20 со сдвигом на один разряд в сторону младших разрядов с входами сумматоров 1-7;

2)младших разрядов диады 14, тетрад 15, 17 и 19 с весом 1 с разрядами

двоично-десятичных сумматоров 8, 9, 11 и 13 с весами 1, 4 соответственно;

3)младшего разряда тетрады 16 с весом 1 с входом двоично-десятичнс- го сумматора 10 с весом 1 и с первыми входами элементов И 21 и 22, выходы которых соединены с входами двоично-десятичного сумматора 10 с весами 4 и 2 соответственно;

4)младшего разряда тетрады 18 с весом 1 с входом двоично-десятичного

сумматора 12 с весом 1 и с первыми входами элементов И 23 и 24, выходы которых соединены с входами двоично- десятичного сумматора 12 с весами 4 и 2 соответственно;

5)вторые входы элементов И 21 и 23 соединены с выходом элемента НЕ 25, вход которого соединен с вторыми входами элементов И 22 и 24 и является входом режима преобразования.

При наличии единицы в младшем разряде диады 14, тетрад 15-19 производится коррекция, R содержимому следующих младших тетрад 15-20 при сдвиге добавляется число 5 при преобразовании в двоично-десятичный код, а при преобразовании в двоично-де- сятично-шестидесятеричный код - число 5 к содержимому тетрад 15, 16, 18 и 20, и число 3 - к содержимому тетрад 17 и 19. Выбор чисел 5 или 3 в тетрадах 17 и 19 осуществляется с помощью элементов И 21-24.

При наличии единицы на входе 29 режима преобразования элементы И 21 и 24 открыты, вход режима преобразования соединяется с вторыми входами элементов И 22 и 24, т.е. они на выходе повторяют входной сигнал с младших разрядов тетрад 16 и 18 и выходы соединены с входами двоично0

5

десятичных сумматоров 10 и 12 с весом 2. А эчементы 21 и 23 закрыты, гак как на их вторые входы подается 5 логический О и независимо от сигналов на первых входах элементов И 21 и 23 на их выходах имеет место логический О, а выходы соединены с входами двоично-десятичных суммаС торов 10 и 12 с весом 4.

При наличии единицы на младших разрядах тетрад 16 и 18 к содержимому тетрад 17 и 19 прибавляется число 3, т.е. осуществляется преобра5 зование в двоично-десятично-шестиде- сятеричный код. При наличии нуля на входе 29 элементы И 21 и 23 открыты, т.е. они на выходе повторяют входной сигнал с младших разрядов тетрад 16 и 18, а выходы соединены с входами двоично-десятичных сумматоров 10 и 12 с весом 4. При этом элементы И 22 и 24 закрыты, так как на их вторые входы подается логический О и независимо от сигналов на первых входах элементов И 22 и 24 на их выходах имеет место логический О, а выходы соединены с входами двоично- десятичных элементов 10 и 12 с весом

0 2. Элементы И 22 и 24 закрыты, так как на их вторые входы подается логический О с входами сумматоров 10 и 12 с весом 2. При наличии единицы на младших разрядах тетрад 16 и 18

5 к содержимому тетрад 17 и 19 прибавляется число 5, т.е. осуществляется преобразование в двоично-десятичный код.

Число тактов преобразования опре0 деляется максимальной разрядностью преобразуемых чисел. В результате выполненных операций содержимое регистра представляет собой сумму экви валентов разрядов двоичного кода пре-

5 образуемого числа, выраженную в коде, зависящем от выбора вида преобразования.

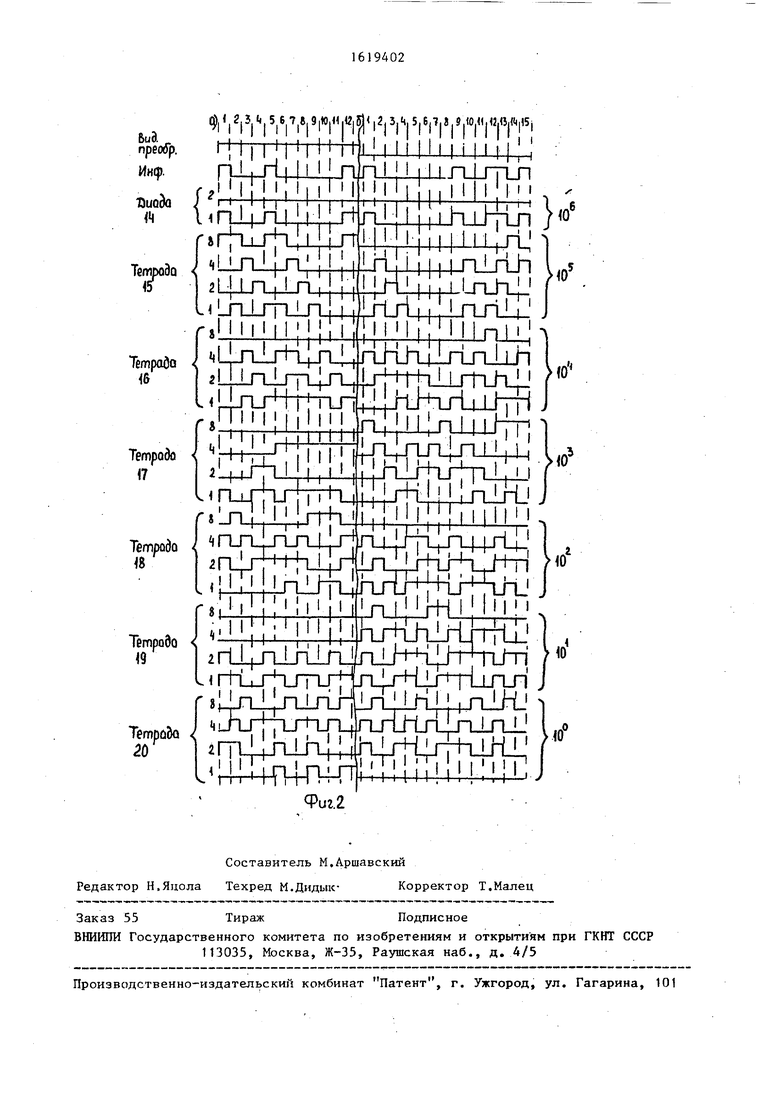

Рассмотрим пример преобразования Q 12-разрядного кода с весом старшего разряда R 180°1 б 32 в двоично- десятично-шестидесятеричный код. Работа преобразователя иллюстрируется временной диаграммой (фиг.2а) и табл.1 кодов.

Пусть на информационный вход подается код 100010000001 (ст. разряд), на входах коммутатора 26 устанавливается число R 180°16 32. На вход

29 вида преобразования подается логическая 1. При этом при наличии единицы на младших разрядах тетрады 16 или 18 производится коррекция. К содержимому следующей младшей тетрады 17 или 19 при сдвиге добавляется число 3, а при наличии единицы на младших разрядах диады 14, тетрад 15-19 производится коррекция. К со- держимому следующей младшей тетрады 15, 16, 18 и 20 при сдвиге добавляется число 5.

Рассмотрим пример преобразования 15-разрядного кода с весом старшего разряда R 104 585с7б в двоично- десятичный код. Работа преобразователя иллюстрируется временной диаграммой (фиг. 26) и табл,2 кодов.

Представление результатов преобразования в регистре преобразователя следующее: тетрада единиц секунд 10 тетрада десятков секунд 10 ; тетрада единиц секунд 10 ; тетрада десятков минут 10 ; тетрада единиц градусов 10 ; тетрада десятков градусов 10 ; диада сотен градусов 10 .

Пусть на информационный вход по- дается код 100000010001001 (ст. разряд). На входах коммутатора 26 устанавливается число R 104°85 7б , на вход 26 подается логический О. При этом при наличии единицы на младших разрядах диады 14 и тетрад 15-19 производится коррекция. К содержимому следующей младшей тетрады 15-20 добавляется число 5.

Формула изобретения

Преобразователь кодов, содержащий регистр, состоящий из тетрад единиц секунд, единиц минут, единиц граду- сов, десятков градусов и диады сотен градусов, сумматоры сотен градусов, единиц градусов, десятков минут, единиц минут, десятков секунд, единиц секунд, двоично-десятичный сумматор десятков .градусов, выходы которого соединены с соответствующими входами тетрады десятков градусов, выходы второго, третьего и четвертого разрядов тетрад единиц градусов, единиц минут, единиц секунд соединены соответственно с входами первого, второго и третьего разрядов соответствующих сумматоров, выходы сумматоQ

r 0

5

Q

5

0

0

ра сотен градусов соединены с соответствующими входами диады сотен градусов, выход старшего разряда которой соединен с первым входом первого разряда сумматора сотен градусов, вход переноса которого соединен с выходом переноса двоично-десятичного сумматора десятков градусов, первые входы первого и третьего разрядов которого соединены с выходом младшего разряда диады сотен градусов, синхровходы и входы сброса регистра соединены соответственно с тактовым и установочным входами преобразователя, выходы которого соединены с выходами регистра, отличающийся тем, что, с целью расширения класса решаемых задач путем обеспечения возможности преобразования двоичного кода с произвольным весом старшего разряда в двоично-десятичный и в двоично-десятично-шестидесятиричный коды, в него введены тетрады десятков секунд и десятков минут, с первого по четвертый элементы И, элемент НЕ, коммутатор, сумматор десятков градусов, двоично-десятичный сумматор младших разрядов, состоящий из последовательно соединенных двоично-десятичного сумматора единиц градусов, двоично-десятичного сумматора десятков минут, двоично-десятичного сумматора единиц минут, двоично-десятичного сумматора

десятков секунд, двоично-десятичного i

сумматора единиц секунд, причем разрядные выходы двоично-десятичного сумматора младших разрядов соединены с входами соответствующих тетрад регистра, а первые разрядные входы двоично-десятичного сумматора младших разрядов соединены с выходами соответствующих сумматоров, выходы с второго по четвертый разрядов тетрад десятков градусов, десятков минут, десятков секунд соединены соответственно с входами с первого по третий разрядов соответствующих сумматоров, выходы первых разрядов тетрады десятков градусов, тетрады десятков минут, тетрады десятков секунд соединены с вторыми входами первого и третьего разрядов двоично-десятичного сумматора единиц градусов, двоично- десятичного сумматора единиц минут и двоично-десятичного сумматора единиц секунд соответственно, выход переноса двоично-десятичного сумматора младших разрядов соединен с входом переноса двоично-десятичного сумматора десятков градусов, выход первого разряда тетрады единиц градусов соединен с вторым входом первого разряда двоично-десятичного сумматора десятков минут и с первыми входами первого и второго элементов И, выходы которых соединены с вторыми входами третьего и второго разрядов двоично-десятичного сумматора десятков минут соответственно, выход первого разряда тетрады единиц минут соединен с вторым входом первого разряда двоично-десятичного сумматора десятков секунд и с первыми входами третьего и четвер9402|0

того элементов И, выходы которых соединены с вторыми входами третьего и второго разрядов двоично-десятичного сумматора десятков секунд соответственно, вторые входы первого и третьего элементов И соединены с выходом элемента НЕ, вход которого соединен с входом режима преобразования и с вторыми входами второго и четвертого элементов И, вторые входы сумматоров соединены с соответствующими выходами коммутатора, информационные входы которого являются входами веса старшего разряда преобразователя, информационный вход которого соединен с управляющим входом коммутатора.

10

J5

Таблица )

« 2,3,11, 5.67.MiW,«itti

11 11 i

p Li.. H | | I И П/П

г/шХШиШ

) I I . I I I i I i M .

V

I

i

{:

rirtilrh

1J

ТегироЭа e

sL Jl+Ln.

гЛ 11 iljji

Тетробо &

empodo 17

ТТЛ

LlllTU1 I || ILT

rAmi i; 11 ц i

О 1 .1 L

l ч 11 11 H: i i i i i. 11

irUTTU i i

r.LrUMj t

njT4JTJTJ4J-yul/T4-n44-rU- ЭТ -trn-J

ujiT| nJJf . i i

nl HHI MM

iJ L I I I . I

.

I I I I I I

iJ L I I I . I

L rti iJTiJ-tl

r riUo-nJJiJ i

TempQtto 20

w-m-q

Фиг.2

i

/П

ViYiViYiViYiTi 51

I 1 I I I I

i i n 1111 i 11 i i;,

П

, , -П-ШТЛ

Ml ц I II I , 1Jll ll hiJ|Ln}rf

HO

1Шт1}$

JiWui iri 73X/uu(fn JUiTruA

nlrL

HO

nl HHI MM

iJ L I I I . I

HO

o°

1 i i i 111 i n i. i J

| Преобразователь двоичного кода угла в двоично-десятичный код градусов | 1981 |

|

SU993243A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Ј Я | |||

Авторы

Даты

1991-01-07—Публикация

1989-02-17—Подача