1

(21)4388789/24-24

(22)09.03.88

(46) 23.12.89. Бкш. № 47 (72) С.Г.Демин, В.Н.Гуминов, С.А.Филатов и С.Н.Абрамов

(53)681.327.6(088.8)

(56)Электронная промьгашенность, 1983, вып. 6 (123), с. 7,8.

Патент Великобритании № 2099649, кл. G 11 С 17/00, опублик. 1983.

(54)НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

(57)Изобретение относится к микроэлектронике, а именно к запоминающим устройствам, и может быть применено при создании ПЗУ большой информационной емкости. Цель изобретения - повышение информационной емкости накопителя. Для этого накопитель в каждой ячейке памяти содержит третий запоминающий транзистор с соответствующими связями. При этом количество шин накопителя не увеличивается, т.к. для выборки используются адресные шины второй группы накопителя. В результате площадь накопителя также не увеличивается, т.к. она определяется только количеством этих шин. 2 ил.

§

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

Изобретение относится к микроэлектронике, а именно к запоминающим устройствам, и может быть применено при создании ПЗУ большой информационной емкости. Цель изобретения - повышение информационной емкости накопителя. Для этого накопитель в каждой ячейке памяти содержит третий запоминающий транзистор с соответствующими связями. При этом количество шин накопителя не увеличивается, т.к. для выборки используются адресные шины второй группы накопителя. В результате площадь накопителя также не увеличивается, т.к.она определяется только количеством этих шин. 2 ил.

Изобретение относится к микроэлектронике, а именно к конструированию запоминающих устройств, и может быть использовано при создании постоянных запоминающих устройств (ПЗУ) большой информационной емкости.

Целью Изобретения является повышение информационной емкости ПЗУ.

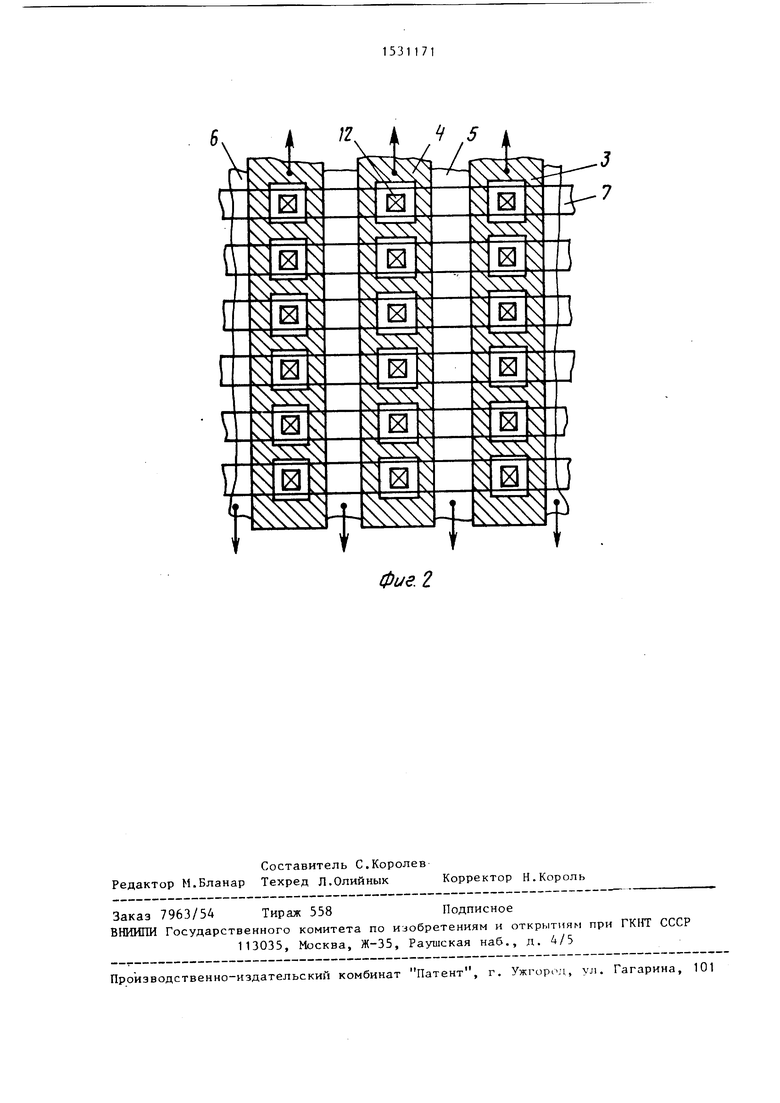

На фиг. 1 представлена электрическая схема предлагаемого накопителя; на фиг. 2 - топология накопителя.

Накопитель содержит первые 1 и вторые 2 запоминающие транзисторы, адресные шины первой 3 и 4 и второй 5 и 6 групп, разрядные шины 7, третьи запоминающие транзисторы 8. Для управления накопителем используются два дешифратора 9 и 10 слов и дешифратор 11 разрядов.

Устройство работает следующим образом.

Б отсутствии обращения к ПЗУ все выходы дешифраторов 9-11 строк и столбцов находятся под потенциалом, запирающим запоминающие транзисторы накопителя.

В режиме обращения на одной из адресных шин 3, 4 формируется уровень сигнала, обеспечивающий отпирание связанных с ней запоминающих транзисторов 1, 2 и 8, одновременно выбирается одна из разрядных шин 7 дешифра- рором 11.

В зависимости от адресного кода дешифратор Ю формирует уровень сигнала, обеспечивающий считывание информации из запоминающих транзисторов 1, 2 и 8, электрически связанных с данными шинами.

Зашивка информации в накопитель обеспечивается формированием высокоел

ро

го или низкого порогового напряжения МОП-транзистора.

Накопитель содержит адресные шины 3 и 4 первой группы, выполненные из поликремния, расположенные параллельно им адресные шины 5 и 6. второй группы, выполненные в виде диффузионных областей, и расположенные перпендикулярно им разрядные шины 7, выпол-. ненные из алюминия. Сток-истоковые области четьфех соседних транзисторов объединены и подключены к разрядным шинам 7 через контактное окно 12.

Формула изобретения

Накопитель для постоянного запоминающего устройства, содержащий ячейки памяти, каждая из которых состоит из двух запоминающих транзисторов, стоки которых подключены к соответстЧ.ьз - ХрГзЯ

2 ;

Фиг.

5

0

нующе разрядной шине накопителя, -затворы - к соответствующим адресным шинам первой группы накопителя, а истоки - к соответствующим адресным шинам второй группы накопителя, исток второго запоминающего транзистора каждой ячейки памяти, кроме последней, столбца накопителя соединен с истоком первого запоминающего транзистора следующей ячейки памяти этого же столбца накопителя, отличающийся тем, что, с целью повышения информационной емкости накопителя, он дополнительно содержит в каждой ячейке памяти третий запоминающий транзистор, сток и затвор которого соединены со стоками и затворами соответственно первого и второго запоминающих транзисторов ячейки, а исток подключен к разрядной шине следующего столбца Накопителя.

фие.2

Авторы

Даты

1989-12-23—Публикация

1988-03-09—Подача