Изобретение относится к вычислительной технике и может быть использовано в автоматике, измерительной технике.

Целью изобретения является повышение быстродействия запоминающего устройства.

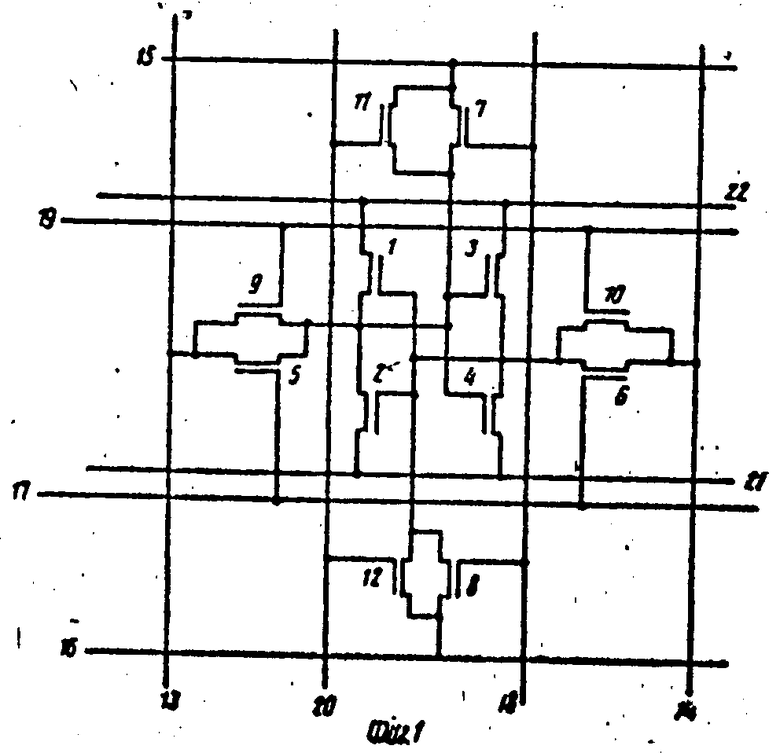

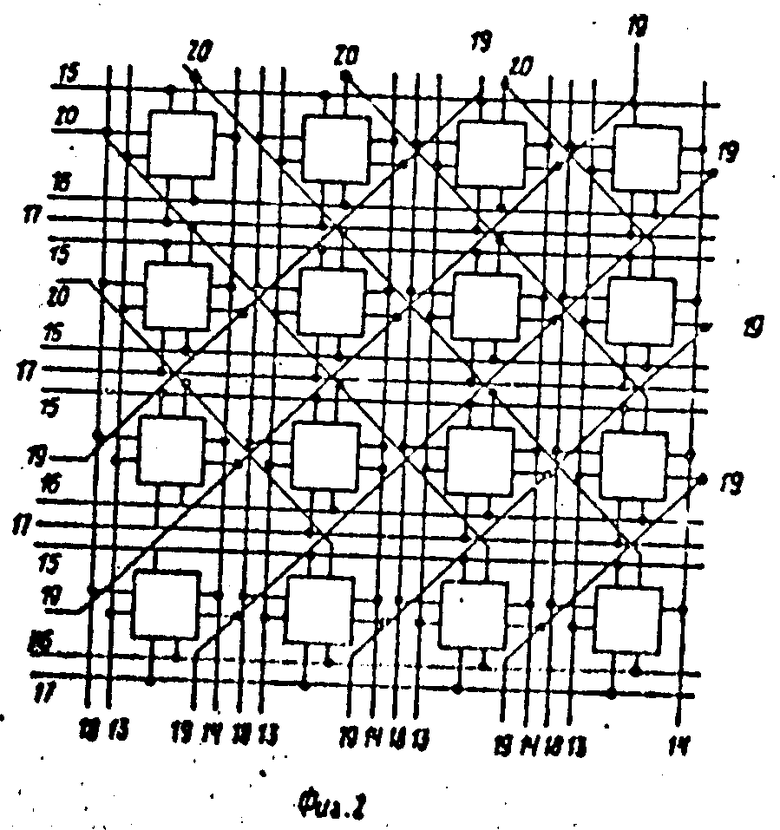

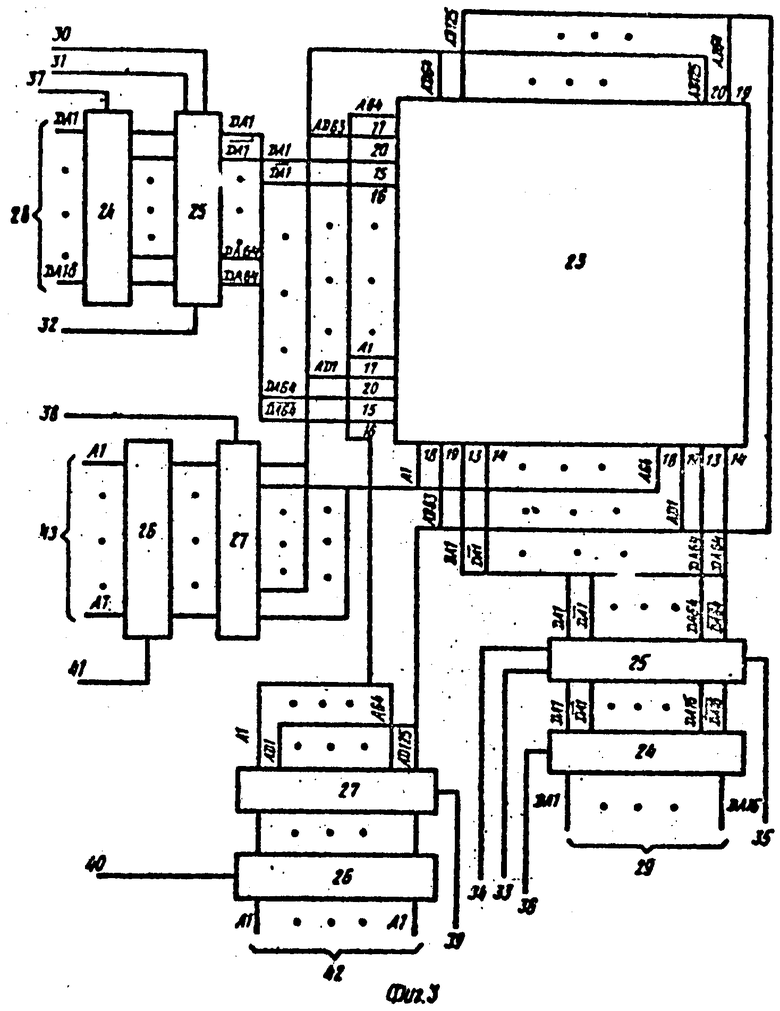

На фиг.1 представлена принципиальная схема элемента памяти; на фиг.2 - схема фрагмента накопителя; на фиг.3 - функциональная схема запоминающего устройства.

Накопитель информации содержит элементы памяти, состоящие из триггера на ключевых транзисторах 1-4 и восьми транзисторов 5-12 связи, шины 13 и 14 прямых и инверсных столбцов соответственно, шины 15 и 16 прямых и инверсных данных строк соответственно, шины 17 и 18 выборки строк и столбцов соответственно, шины 19 и 20 выборки диагоналей первой и второй групп соответственно, шину 21 нулевого потенциала, шину 22 питания.

Запоминающее устройство содержит накопитель 23 информации, усилители 24 записи-считывания, мультиплексоры 25 данных, дешифраторы 26, мультиплексоры 27 адреса, информационные входы 28 и 29 первой и второй групп соответственно, входы 30 и 31 управления коммутацией первого мультиплексора 25 данных, первый тактовый вход 32, входы 33 и 34 управления коммутацией второго мультиплексора 25 данных, второй тактовый вход 35, входы 36 и 37 управления записью-считыванием строк и столбцов соответственно, входы 38, 39 управления режимом выборки устройства, входы 40 и 41 разрешения выборки устройства, адресные входы 42 и 43 первой и второй групп.

Пример конкретного выполнения приведен для запоминающего устройства с емкостью матрицы 66х64 элемента памяти в строках и столбцах и 16-разрядными данными. В этом случае общее число фрагментов накопителя равно 16.

Полупроводниковое запоминающее устройство работает следующим образом. В режиме хранения напряжение на входах устройства 32, 41 и 40, 35 имеет низкий уровень, уровень напряжения на остальных внешних входах устройства значения не имеет. Низкий логический уровень напряжения на входах устройства 32 и 35 запрещает работу мультиплексоров 25, а на входах 40 и 41 - работу дешифраторов 26, таким образом на выходах дешифраторов 26 будет низкий логический уровень и шины 17, 18, 19 и 20 будут находиться под его действием, следовательно, транзисторы 5-12 связи в элементах, подключенные к этим шинам, будут закрыты.

При обращении к запоминающему устройству на адресных входах 42 и 43 выставляется адрес, на информационных входах 28 и 29 выставляются данные, на вход 37 подается высокий логический уровень, если запись - по столбцам, и низкий логический уровень, если чтение - по столбцам, на входе 36 выставляется высокий логический уровень, если запись - по строкам, и низкий логический уровень, если чтение - по строкам, на вход 38 подается низкий логической уровень, если обращение будет к столбцам, и высокий логический уровень, если обращение будет к шинам 20 выборки диагоналей второй группы, на вход 39 подается низкий логический уровень, если обращение будет к строкам, и высокий логический уровень, если обращение - к шинам 19 выборки диагоналей первой группы.

На входы 30 и 31 в двоичном коде задается адрес фрагмента по столбцам (16х64), где 16 - количество элементов памяти по вертикали матрицы накопителя 23, 64 - количество элементов памяти по горизонтали матрицы накопителя 23, на входы 33 и 34 в двоичном коде задается адрес фрагмента по строкам (16х64), где 16 - количество элементов памяти по горизонтали матрицы накопителя 23, 64 - количество элементов памяти по вертикали матрицы накопителя 23. После того, как управляющие сигналы, данные и адреса выставлены, подается высокий логический уровень на вход 41, если происходит обращение по столбцам, и на вход 40, если происходит обращение по строкам.

Таким образом, полупроводниковое запоминающее устройство позволяет обращаться к нему по двум координатам одновременно в режиме чтения и записи, так как при записи в любой столбец или диагональ по столбцу возможно чтение любой строки или диагонали по строке.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1989 |

|

SU1648205A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматике, измерительной технике. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что накопитель информации содержит две группы шин 19 и 20 выборки диагоналей с соответствующими связями, а запоминающее устройство содержит мультиплексоры данных и мультиплексоры адреса с соответствующими связями. Наличие шин 19 и 20 позволяет проводить выборку информации по столбцам, строкам и диагоналям матрицы накопителя. При этом подключение соответствующих входов к накопителю 23 с помощью мультиплексоров позволяет обращаться к устройству по двум координатам одновременно: по одной в режиме записи, а по другой и по диагонали в режиме считывания. 2 с.п. ф-лы, 3 ил.

| Патент ФРГ N 3313441, кл.C 11G 11/40, 1985. |

Авторы

Даты

1994-12-30—Публикация

1987-12-28—Подача