1

(21)4417553/24-24

(22)28.04.88 (46)

№ 47

23.12.89. Бюл. (72) И.З.Кузьменко, О.В.Рябова и А.У.Ярмухаметов (33) 681.325 (088.8)

(56)Авторское свидетельство СССР f 1045238, кл. Н 03 М 7/00, 1982.

Авторское свидетельство СССР № 1159164, кл. Н 03 М 7/00, 1983. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬ- НОГО КО,аА В ПАРАЛЛЕЛЬНЫЙ

(57)Изобретение относится к вычислительной технике, а именно к устройствам передачи информации, и может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи. Изобретение, используя в данное временное расположение информационных импульсов входных последовательностей таким образом, чтобы в момент записи информации под управлением импульсов одной последовательности значение импульсов другой последовательности соответствовало значению информации, получаемой из канала связи, позволяет упростить конструкцию преобразователя. Преобразователь последовательного кода в параллельный содержит регистр 1 сдвига, элемент ИЛИ 2, счетчик 3 импульсов, расширитель 4 импульсов и элемент 5 задержки. 2 ил.

Ф

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1517135A1 |

| Преобразователь последовательного кода в параллельный | 1983 |

|

SU1159164A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1376244A1 |

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1462485A2 |

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Преобразователь параллельного кода в последовательный | 1988 |

|

SU1587643A2 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

Изобретение относится к вычислительной технике, а именно к устройствам передачи информации, и может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи. Изобретение, используя в данное временное расположение информационных импульсов входных последовательностей таким образом, чтобы в моменты записи информации под управлением импульсов одной последовательности значение импульсов другой последовательности соответствовало значению информации, получаемой из канала связи, позволяет упростить конструкцию преобразователя. Преобразователь последовательного кода в параллельный содержит регистр 1 сдвига, элемент ИЛИ 2, счетчик 3 импульсов, расширитель 4 импульсов и элемент 5 задержки. 2 ил.

Изобретение относится к вычислительной технике, а именно к устройствам передачи и преобразования информации, и может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи.

Целью изобретения является упро- преобразователя.

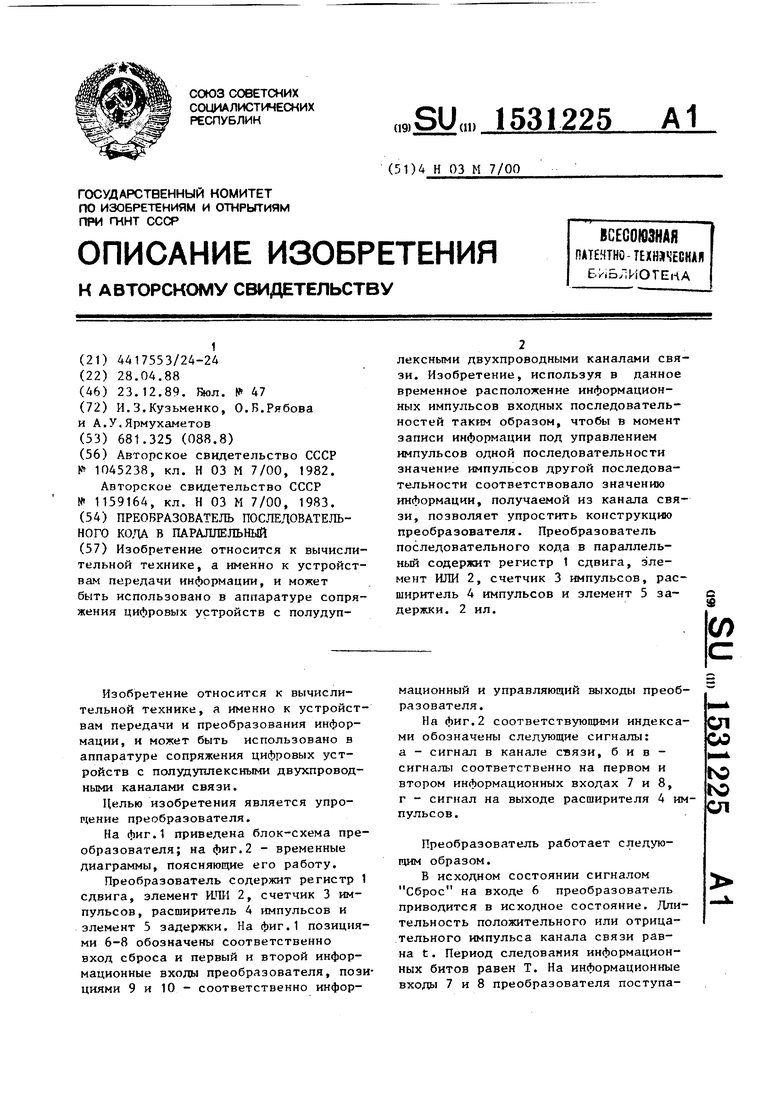

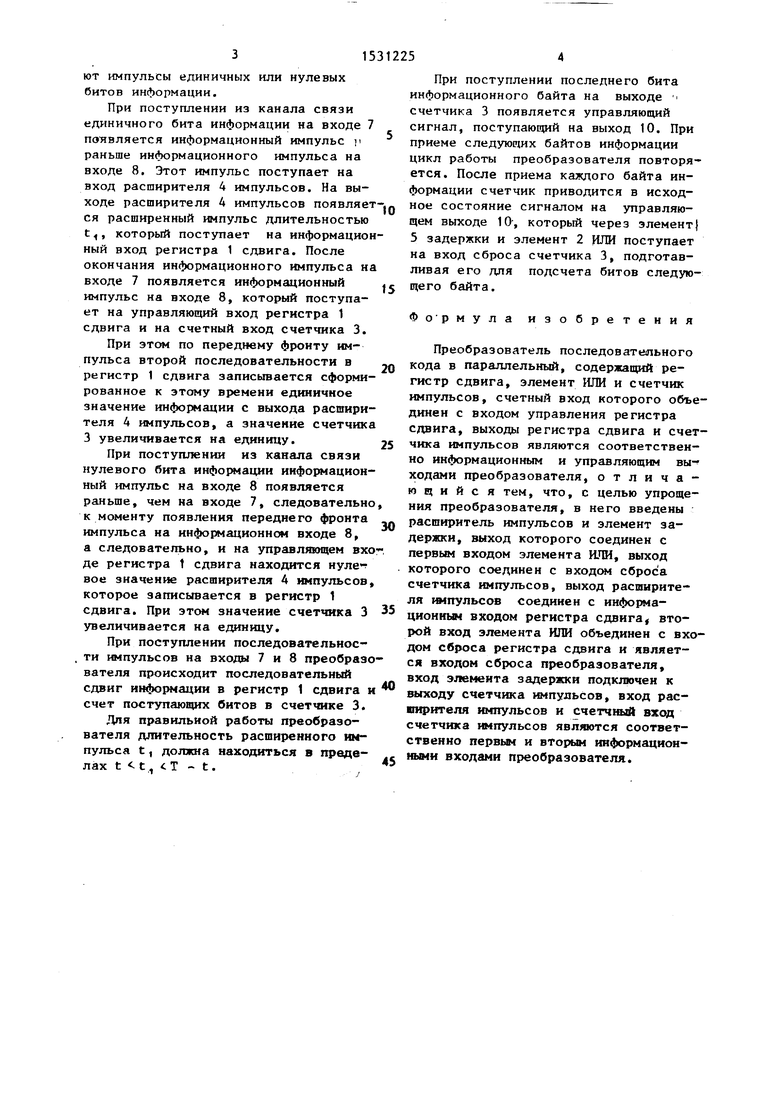

На фиг.1 приведена блок-схема преобразователя; на фиг.2 - временные диаграммы, поясняющие его работу.

Преобразователь содержит регистр 1 сдвига, элемент Шти 2, счетчик 3 импульсов, расширитель 4 импульсов и злемент 5 задержки. На фиг.1 позициями 6-8 обозначены соответственно вход сброса и первый и второй информационные входы преобразователя, позициями 9 и 10 - соответственно информационный и управляющий выходы преоб- разователя.

На фиг.2 соответствующими индексами обозначены следующие сигналы: а - сигнал в канале связи, б и в - сигналы соответственно на первом и втором информационных входах 7 и 8, г - сигнал на выходе расширителя 4 импульсов.

Преобразователь работает следующим образом.

В исходном состоянии сигналом Сброс на входе 6 преобразователь приводится в исходное состояние. Лли- тельность положительного или отрицательного импульса канала связи равна t. Период следования информационных битов равен Т. На информационные входы 7 и 8 преобразователя поступают импульсы единичных или нулевых битов информации.

При поступлении из канала связи единичного бита информации на входе 7 появляется информационный импульс г раньше информационного импульса на входе 8. Этот импульс поступает на вход расширителя 4 импульсов. На выходе расширителя 4 импульсов появляет ся расширенный импульс длительностью t , который поступает на информационный вход регистра 1 сдвига. После окончания информационного импульса на входе 7 появляется информационный импульс на входе 8, который поступает на управляюпщй вход регистра 1 сдвига и на счетный вход счетчика 3.

При этом по переднему фронту импульса второй последовательности в регистр 1 сдвига записьгаается сформированное к этому времени единичное значение информации с выхода расширителя 4 импульсов, а значение счетчика 3 увеличивается на единицу.

При поступлении из канала связи нулевого бита информации информационный импульс на входе 8 появляется раньше, чем на входе 7, следовательно к моменту появления переднего фронта импульса на информационном входе 8, а следовательно, и на управляющем вхо де регистра t сдвига находится нуле- вое значение расширителя А импульсов, которое записьгаается в регистр 1 сдвига. При этом значение счетчика 3 увеличивается на едашицу.

При поступлении последовательности импульсов на входы 7 и 8 преобразователя происходит последовательный сдвиг информации в регистр 1 сдвига и счет поступающих битов в счетчике 3.

Для правильной работы преобразователя длительность расширенного импульса t, должна находиться в преде

лах .,cT -t.

S

При поступлении последнего бита информационного байта на выходе счетчика 3 появляется управляющий сигнал, поступающий на выход 10. При приеме следуюрдих байтов информации цикл работы преобразователя повторяется. После приема каждого байта информации счетчик приводится в исходное состояние сигналом на управляющем выходе 10, который через элемент) 5 задержки и элемент 2 ИЛИ поступает на вход сброса счетчика 3, подготавливая его для подсчета битов следующего байта.

Ф о р мула изобретения

Преобразователь последовательного кода в параллельный, содержащий регистр сдвига, элемент ИЛИ и счетчик импульсов, счетный вход которого объединен с входом управления регистра сдвига, выходы регистра сдвига и счетчика импульсов являются соответственно информационным и управляющим вы- ходами преобразователя, отличающийся тем, что, с целью упрощения преобразователя, в него введены расширитель импульсов и элемент задержки, выход которого соединен с первым входом элемента ШТИ, выход которого соединен с входсм сброса счетчика импульсов, выход расширителя (шпульсов соединен с информационным входом регистра сдвига второй вход элемента ИЛИ объединен с входом сброса регистра сдвига и является входом сброса преобразователя, вход элемента задержки подключен к выходу счетчика импульсов, вход рас- пирителя импульсов и счетчный вход счетчика импульсов является соответственно первым и вторым информационными входами преобразователя.

ИММл--фиг.

фиг. 2

Авторы

Даты

1989-12-23—Публикация

1988-04-28—Подача