Изобретение относится к вычислительной технике и может быть использовано при создании преобразователей информац1 И, входящих в состав аппаратуры сопряжения цифровых уст- poiiCTB с полудуплексными двухпроводными каналами связи.

Целью изобретения является повышение помехоустойчивости преобразователя.

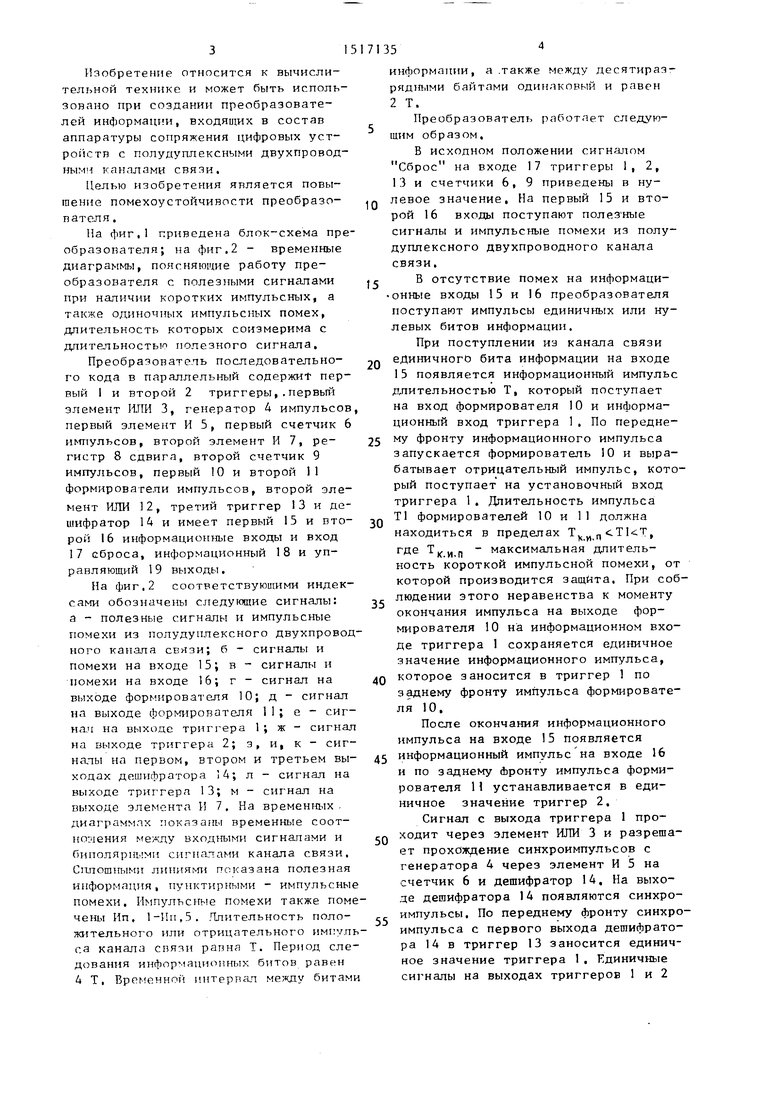

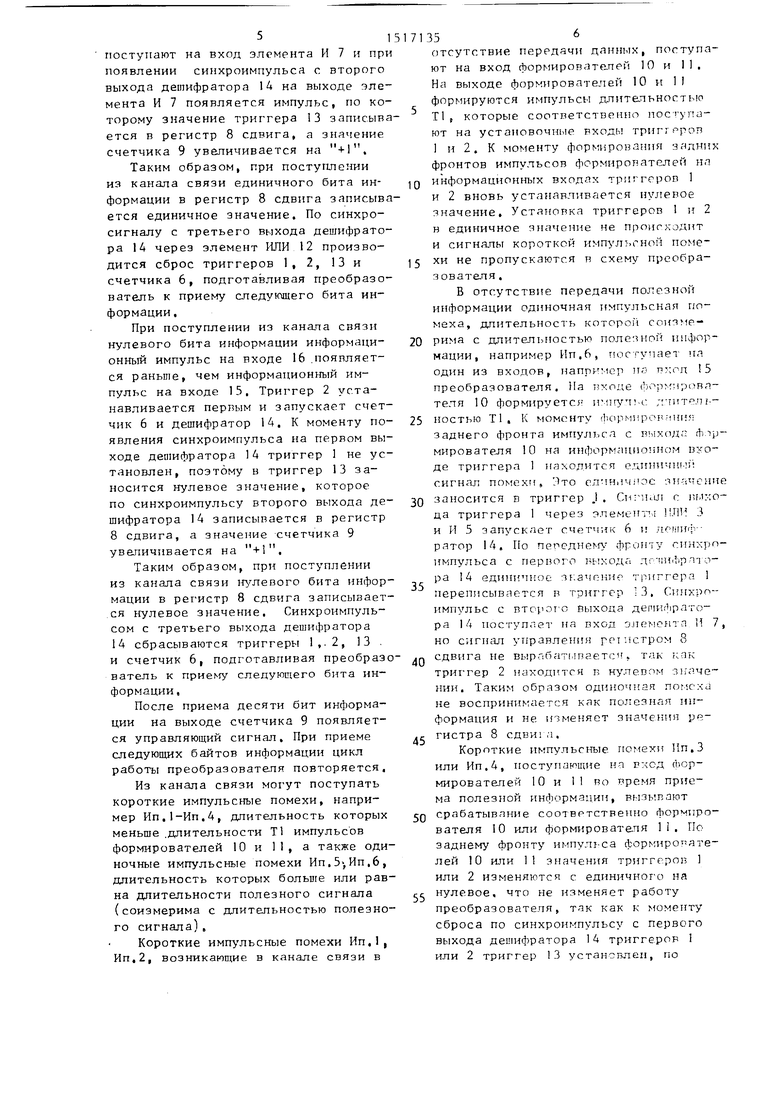

На фиг,1 приведена блок-схема преобразователя; на фиг.2 - временные диаграммы, поясняющие работу преобразователя с полезными сигналами при наличии коротких импульсных, а также одиночных импульсных помех, длительность которых соизмерима с длительностью полезного сигнала.

Преобразователь последовательного кода в параллельный coдepжиt первый 1 и второй 2 триггеры,.первьм элемент НИИ 3, генератор А импульсов первый элемент И 5, первый счетчик 6 и myльcoв, второй элемент И 7, регистр 8 сдвига, второй счетчик 9 импульсов, первый 10 и второй 11 формирователи импульсов, второй элемент ИЛИ 12, третий триггер 13 и дешифратор 14 и имеет первый 15 и второй 16 информационные входы и вход 17 сброса, информационный 18 и управляющий 19 выходы.

На фиг,2 соответствующими индексами обозначены следующие сигналы: а - полезные сигналы и импульсные помехи из полудуплексного двухпроводного канала связи; б - сигналы и помехи на входе 15; в - сигналы и помехи на входе 16; г - сигнал на выходе формирователя 10; д - сигнал на выходе формирователя 11; е - сиг нач на выходе триггера 1; ж - сигна на выходе триггера 2; з, и, к - сигналы на первом, втором и третьем выходах дешифратора lA; л - сигнал на выходе триггера 13; м - сигнал на выходе элемента И 7. На временных- диаграммах показаны временные соотнесения между входными сигналами и биполярными сигналами канала связи, С1гпош гыми линиями показана полезная информация, пунктирными - импульсны помехи. Импульсные помехи также помчены Ип. 1-Ип,5. Ллительность положительного или отрицательного импулса канала связи равна Т. Период следования информационных битов равен 4 Т, Временной интерпап между битам

5

0

5

0

5

0

5

0

5

информации, а .также между десятираз- ряд1П,1ми байтами одинаковый и равен 2 Т.

Преобразователь работает следующим образом.

В исходном положении сигналом Сброс на входе 17 триггеры 1, 2, 13 и счетчики 6, 9 приведены в нулевое значение. На первый 15 и второй 16 входы поступают полез ные сигналы и импульсные помехи из полудуплексного двухпроводного канала связи.

В отсутствие помех на информаци- онные входы 15 и 16 преобразователя поступают импульсы единичных или нулевых битов информации.

При поступлении из канала связи единичного бита информации на входе 15 появляется информационный импульс длительностью Т, который поступает на вход формирователя 10 и информационный вход триггера 1, По переднему фронту информационного импульса запускается формирователь 10 и вырабатывает отрицательный импульс, который поступает на установочный вход триггера 1. Длительность импульса Т1 формирователей 10 и 11 должна находиться в пределах , где , - максимальная длительность короткой импульсной помехи, от которой производится защита. При соблюдении этого неравенства к моменту окончания импульса на выходе формирователя 10 на информационном входе триггера 1 сохраняется единичное значение информационного импульса, которое заносится в триггер 1 по заднему фронту импульса формирователя 10.

После окончания информационного импульса на входе 15 появляется информационный импульс на входе 16 и по заднему Фронту импульса формирователя 1 устанавливается в единичное значение триггер 2.

Сигнал с выхода триггера 1 проходит через элемент ИЛИ 3 и разрешает прохождение синхроимпульсов с генератора 4 через элемент И 5 на счетчик 6 и дешифратор 14. На выходе дешифратора 14 появляются синхроимпульсы. По переднему фронту синхроимпульса с первого выхода дешифратора 14 в триггер 13 заносится единичное значение триггера 1. Единичные сигналы на выходах триггеров 1 и 2

поступают на вход элемента И 7 и пр появлении синхроимпульса с второго выхода дешифратора 14 на выходе элемента И 7 появляется импульс, по которому значение триггера 13 записывется в регистр 8 сдвига, а значение счетчика 9 увеличивается на +1,

Таким образом, при поступлении из канала связи единичного бита информации в регистр 8 сдвига записывется единичное значение. По синхросигналу с третьего выхода дешифратора 14 через элемент ИЛИ 12 производится сброс триггеров 1, 2, 13 и счетчика 6, подготавливая преобразователь к приему следующего бита информации.

При поступлении из канала связи нулевого бита информации информационный импульс на входе 16 .появляется раньше, чем информационный импульс на входе 15, Триггер 2 устанавливается первым и запускает счетчик 6 и дешифратор 14. К моменту появления синхроимпульса на первом выходе дешифратора 14 триггер 1 не установлен, поэтому в триггер 13 заносится нулевое значение, которое по синхроимпульсу второго выхода дешифратора 14 записывается в регистр 8 сдвига, а значение счетчика 9 увеличивается на +1.

Таким образом, при поступлении из канала связи 1Т1,глевого бита информации в регистр 8 сдвига записывает- ,ся нулевое значение. Синхроимпульсом с третьего выхода дешифратора 14 сбрасываются триггеры 1,. 2, 13 . и счетчик 6, подготавливая преобразователь к приему следующего бита информации.

После приема десяти бит информации на выходе счетчика 9 появляется управляющий сигнал. При приеме следующих байтов информации цикл работы преобразователя повторяется.

Из канала связи могут поступать короткие импульсные помехи, например Ип.1-Ип.4, длительность которых меньще .длительности Т1 импульсов формирователей 10 и 11, а также одиночные импульсные помехи Ип.5,Ип,6, длительность которых больше или равна длительности полезного сигнала (соизмерима с длительностью полезного сигнала),

Короткие импульсные помехи Ип.1, Ип,2, возникающие в канале связи в

171356

отсутствие передачи данных, поступают на вход формировлте пей 10 и II. На выходе формирователей 10 и 11 формируются импульсы дпительностью 11, которые соответственно пос упа- ют на установочные входы триггеров 1 и 2. К моменту формирования задних фронтов импульсов формирователей нл

Q информационных входах триггороп 1 и 2 вновь устанавливается нулевое значение. Установка триггеров 1 и 2 в единичное значение не происходит и сигналы короткой импул1 гной поме 5 хи не пропускаются н схему преобра- 3 овате.пя.

В отсутствие передачи полезной информации одиночная импульсная помеха, длительность KOTOpoii соизме20 рима с длительностью полезной информации, например Ип.6, поcryпает на один из входов, нaпp п-1ep пя пход 5 преобразователя. Па ()ор ;ировя теля 10 формируется ич1гл, тьс: ;: титр.п(-

25 ностью Т1, К моменту формирования

заднего фронта импульса с 1 ь ход;; гЬ тр- мирователя 10 на информационном вуо- де триггера 1 находится е.цнничн|.11 сигн;гл помсхп, Это слиничпос зиачснне заносится в триггер J, Сигиш с IU.IKO- да триггера 1 через элементм М.П1 3 и И 5 запускает счетчик 6 и гтоин р-- ратор 14. По пepeднe 1фронту cinixpo- нмпульса с первого 5ыхода дг- ии..чртора 14 единичное зк.ачоние триггера 1 переписывается в триггер 13, Синхроимпульс с второт о выхода дешифратора 14 ноступает на вход элемента И 7, но сигнет управления pPi icTpoM 8 сдвига не вырпбат лпаетс.. так как триггер 2 находится в нулевом 1;пче НИИ. Таким образом одиночная norscxa не воспринимается как полезная информация и не. изменяет значения регистра 8 сдвига,

Короткие импульсные помехи Пп.З или Ип,4, поступающие на рход (Ъор- мирователей 10 и 11 во премя приема полезной информации, вызывают

50 срабатывание cooTBPTCTBeiuio формирователя 10 или формироватепя Н, По заднему фронту импулг-са формирояаге- лей 10 или 11 значения триггеров 1 или 2 изменяются с единнчног о на

J5 нулевое, что не изменяет работу преобразователя, так как к моменту сброса по синхроимпульсу с первого выхода дешифратора 14 триггеров 1 или 2 триггер 13 установлен, по

30

35

40

45

)( илулг.гу с BTopoi o выхода де iDiiilip.iTopa 4 произведен сдвиг в ре- гнс 8 сдвига з 1ачемия сигнала с ;5Ь(хог1л триггера 13. Работа счетчи- 6 ti ;1,е ифратора 14 поддерживает- ( сг:чнич111 м значением одного из 1 ри: r ,;i;c;j 1 .или 2 I преобразователь С: 1 рпОа п.ч йс г прием бита полезной ин- ( с r - air.iii до конца. Таким образом, исм;.:гкие импульсные помехи, воздейст чу;о11:ие а-: цходы преобразователя во Бремя приема полезной информации, не влияют на правильную работу преоб- р .П чователя,

Одиночная импульсная помеха, лмпимер Ип,5, длительность котор ой ;. -; мерима с длительностью полезно- :о сигнала, аостунающая на вход 16 HV :. ТОра ювателя во время приема ио- .. -iioii информации, вызывает формиро- :,--ь:ие импульса на входе формировате- -i i 1 1 и не изменяет состояния других ч -;ментов преобразователя. Таким . ;-азом, одиночные импульсные поме- xi-:. длитв-чьность которых соизмери- :r-i с длитепьностью полезного сигна- la, воздействующие на входы преобра- ч. ггеля во время приема полезной Формации, не влияют на правильную г .1: :.jTy преобразователя,

,Г1 :я правильной работы преобразо- ;;-и еля В15еменные параметры синхроим- ь уш.сов на выходах дешифратора 14 долл; . удоБлотворять следующим соот- но.-иениям: длительность синхроимпульС. f в

4Т - Tj . я

Т2

время появления синхроимпульса с первого вых11да дешифратора 14 отно- ельно времени установки установив- fic; ося первым триггера 1 или 2 рав- ito JT2; премя появления синхроимпуль- .; , .третьего выхода дешифратора 14 ;1 ,ч ис1ггельно времени установки у .чичсьзп-. шег ося первым триггера 2 л J : i р:: Л i i О 7 Т 2 ,

Р

л а

изобретения

Пре1:Празонатель последователыю- ),.; L параплельный, содержащий ..i :::; : п гггорой триггеры, выходы ко- : рь;;ч с;,п ;u:iioMbi с первым и вторыч : Jд. первого элемента ИЛИ, гене

3

0

5

0

5

0

5

0

5

ратор импульсов, выход которого сое динен с Первым входом первого злемен та И, выход которого соединен со счетным входом первого счетчика импульсов, второй элемент И, регистр сдвига и второй счетчик импульсов, счетный вход которого объединен с управляющим входом регистра сдвига, входы сброса первого и второго триггеров объединены, выходы регистра сдвига и второго счетчика импульсов являются соответственно информационным и управляющим выходами преобразователя, отличающийся тем, что, с целью повышения помехоустойчивости преобразователя, в него введены формирователи импульсов, второй элемент ИЛИ, третий триггер и дешифратор, первый, второй и третий выходы которого соединены соответственно с установочным входом третьего триггера, с первым входом второго элемента И и с первым входом второго элемента Ш1И, выход которого соединен с входами сброса первого счетчика импульсов, третьего триггера и подключен к входу сброса первого триггера, выход третьего триггера соединен с информационным входом регистра сдвига, выходы первого и второго формирователей импульсов подключены к установочным входам одноименных триггеров, выход первого элемента ИЛИ соединен с вторым входом первого элемента И, информационный вход третьего триггера объединен с вторым входом второго элемента И и. подключен к выходу первого триггера, информационный вход которого объединен с входом первого форм фователя импульсов и является первым информационным входом преобразователя, третий вход г.торого элемента И подключен к выходу второго триггера, информационный вход которого объединен с входом nT jporo формирователя импульсов и является вторым информационным входом преобразователя, выходы первого счетчика импульсов соединены с входами дещифратора, управляющий вход регистра сдвига подключен к выходу второго элемента И, вход сброса второго счетчика импульсов объединен с вторым входом второго элемента UTri и является входом сброса преобразователя ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1980 |

|

SU924696A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Синхронизирующее устройство | 1984 |

|

SU1213528A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1989 |

|

SU1656546A1 |

| ДЕШИФРАТОР КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 2021 |

|

RU2754348C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании преобразователей информации, входящих в состав аппаратуры сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи. Изобретение обеспечивает защиту преобразователя от коротких импульсных помех, а также одиночных импульсных помех, соизмеримых по длительности с длительностью полезного сигнала, чем обеспечивается повышение помехоустойчивости преобразователя. Преобразователь последовательного кода в параллельный содержит три триггера 1, 2 и 13, два элемента ИЛИ 3 и 12, генератор 4 импульсов, два счетчика 6 и 9 импульсов, регистр 8 сдвига, два формирователя 10 и 11 импульсов и дешифратор 14. 2 ил.

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательного кода в параллельный | 1983 |

|

SU1159164A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-23—Публикация

1988-03-10—Подача