Изобретение oTHocirii:n к aRTOMirni- ке и В1,1чнслител1.иой технике и может HcnojTb3OBaTt CH для повышения достоверности обработки и передачи дискретной информации.

Цельн) изобретения является повышение помехоустойчивости устройства.

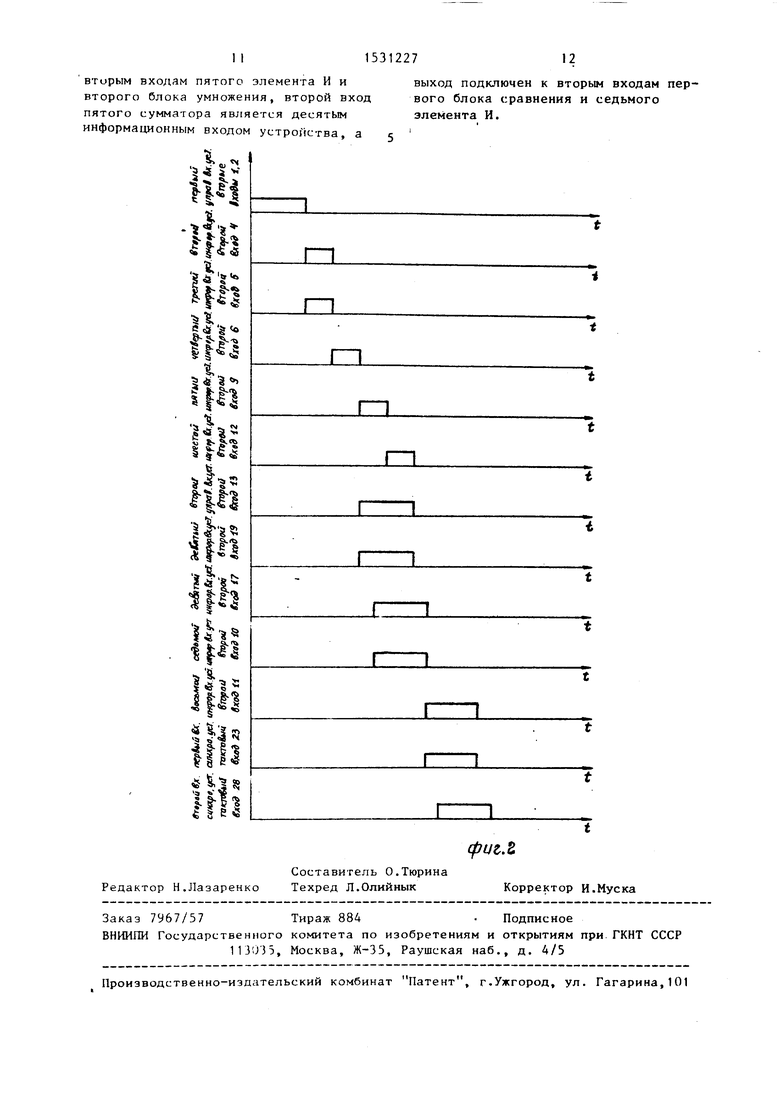

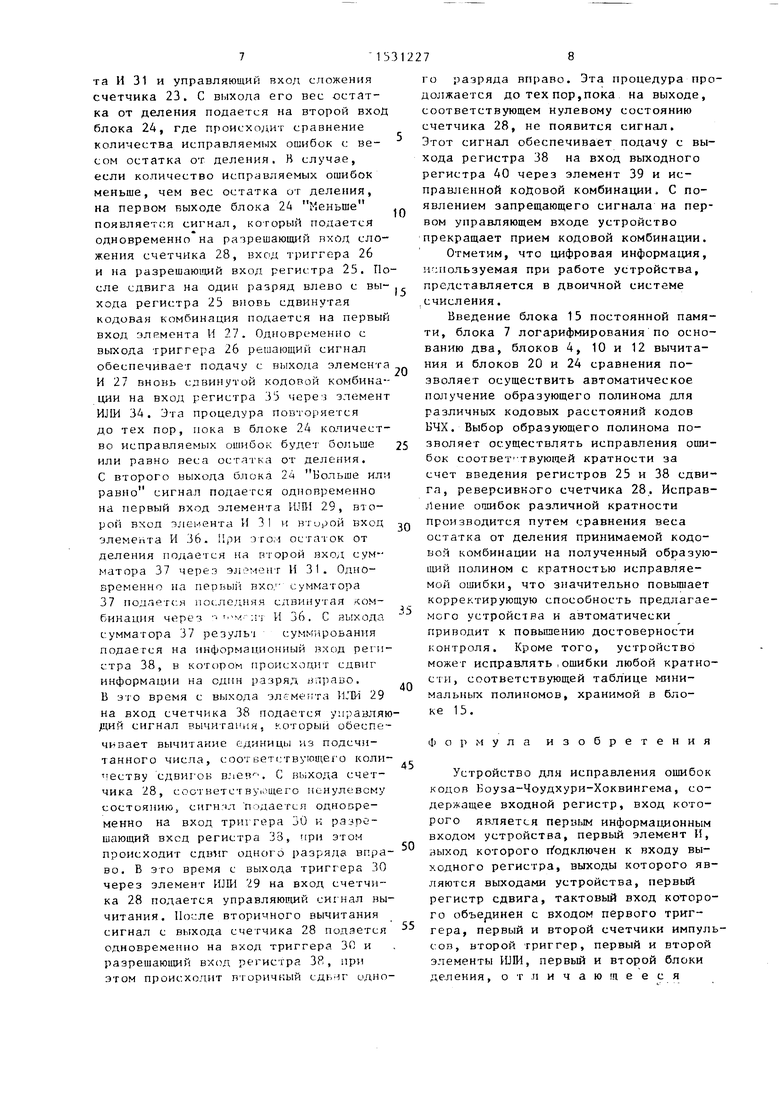

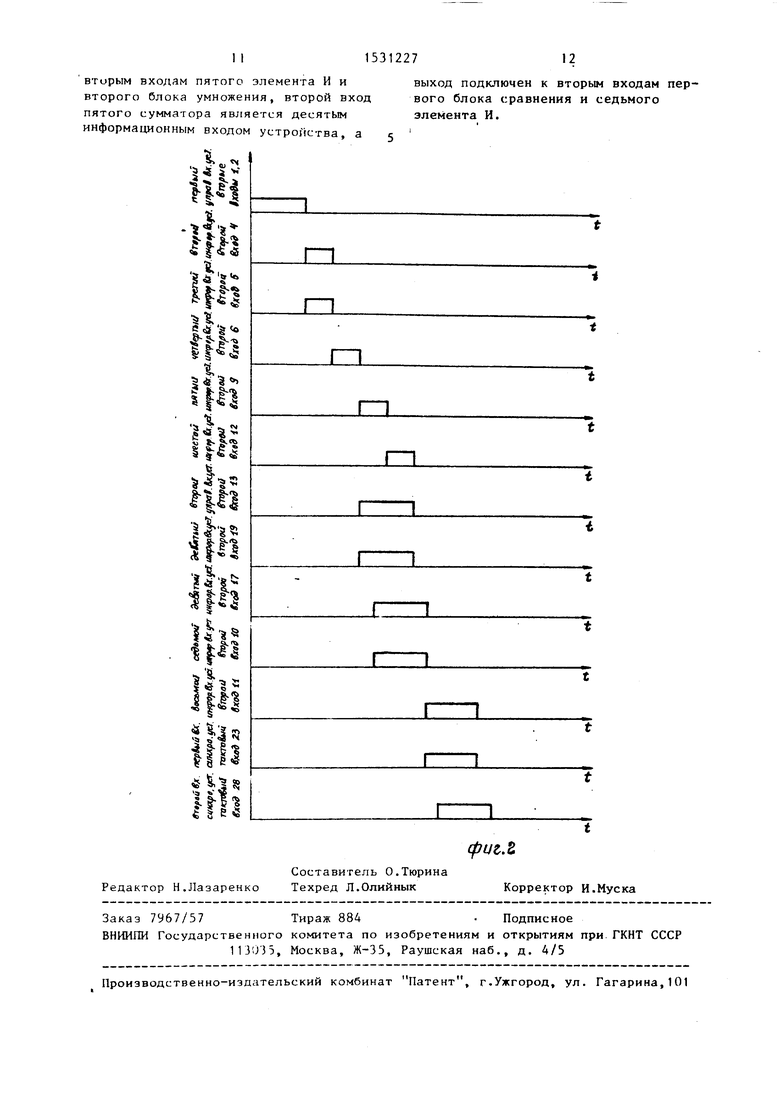

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- временная /u-iarjiaMMa сигналов на входах устройства.

Устройство содержит счетчики 1 и

2импульсогз, сумматор 3, блок Д вычитания, сумматор 5, блок 6 умножения, плок 7 логарифмирования, блок 8 деления, сумматор 9, 6j:oK 10 вычитания, блок 11 деления, блик 12 вычитания, perviCTp 13, регисгр 14 адреса, блок

15 постоянной памяти, блок 16; умноже ния, регисггр 17, элемент И 18, сумматор 19, блок 20 сравнения, элемент И 21, блок 22 деления, счетчик 23 импульсов, блок 24 сравнеьпти, регист 25 сдвига, триггер 26, элемент И 27, реверсивный счетчик 28, элемент ИЛИ 29, тригг ер 30, -элемен г И 31, входной регистр 32, элемент Н 33. Эле- мочг ИЛИ 34, регистр 35, элемент И 3 сумматор 37, реги(. гр 38 сл.вига, элемент И 39, выходнсп 1П;гис р 40,

Устройство работает следуютиим обр3ом,

11е1:1Всначял1,но и сумг-Лтор 5 заносися дpoичt oe чи;;ло, соответс 1 вующее единице, в блок 4 ,.1читания заноситс двоичное число, соо. ччггвующее количеству информационных символич кодовой комбинации, поступающей на перпы информлционный вход устройства, в блок 6 умн11жения заносится двоичное число, соответствую1цсе двойке, в ре- ги1:тр 13 заносится двоичное число, соогветствуклчее еп,инице, на вход сумматора 19 поступает двоичное число, соответстпую|; ее единице. В блоке 15 гк стояикой памяти запи.саны значения минимаг1ьных полиномов с со- О1 ветст вую1чими адресами .

Кодовая кcl бинaция, закодированная Щ1клическим кодом (К,К), поступа ег на вход регис гра 32 и одновременно на первые входь счетчиков 1 и 2 (счетчик 1 считает количес .тво единиц а счетчик . - количество нулей кодовой комбинации). На первый вход сумматора J Ц(дае ся шоичнсзе число, соответс } уы1цее количеству н.улей принимаемой (й комбинации, на вто

.

10

15

2025 ,

, 30

35

40

45

50

55

рой вход сумматора 3 подается двоичное число, соответствующее количеству единиц принимаемой кодовой комби-, нации. С выхода сумматора 3 количество символов, соответствующее результату суммирования, подается одновременно на вход сумматора 5 и вход блока 4 яычитания. С выхода блока 4 двоичное число, соответствующее количеству проверочных символов, подается на первый вход блока 6. Одновременно на второй его вход подается сигнал, соответствующий двойке. С выхода блока 6 двоичное число, cd- ответствуюиее результату умножения, подается на первый вход блока 8 деления. С выхода сумматора 5 результат суммирования подается на вход блока 7 логарифмирования по основанию два. С выхода блока 7 двоичное число, соответствующее результату логарифмирования, подается одновременно на второй вход блока 8 и на вхо; младших разрядов регистра 13. С выхода блока 8 двоичное число, соответствующее результату деления, подает- ся на первый вход сумматора 9, на второй вход которого подается двоичное число, соответствующее единице. С выхода сумматора 9 двоичное число, соответствующее результату суммирования, подается одновременно на первый вход блока 12 и первый вход блока 10. С выхода блока 10 на первый вход блока 11 деления подается двоичное число, соответствующее результату вычитания, на второй его вход подается число два. С.выхода блока 11 на первый вход блока 24 сравнения подается двоичное число, соответствующее результату деления. На второй вход блока 12 подается двоичное число, соответствующее единице. С выхода блока 12 двоичное число, соответствующее результату вычитания, подается на второй вход блока 20 сравнения. Одновременно на управляющий вход регистра 13 подается сигнал, который обеспечивает подачу двоичного числа, соответствующего единице, одновременно на первый вход сумматора 19 и на вход старших разрядов регистра 14. С выхода регистра 14 сформированный адрес прступает на вход блока 15. С выхода блока 15 выбранный минимальный полином подается на первый вход блока 16. Одновременно на второй вход блока 16 с выхода регистра 17 подается двоичное число, соответствующее единице, поскольку на вход регистра 17 подается высокий потенциал девятого информационного входа. С выхода сумматора 31 двоичное число, соответствующее результату суммирования, подается одновременно на второй вход элемента И 21 и первый вход блока 20 В блоке 20 сравнивается двоичное число, соответствующее результату суммирования в сумматоре 19 с двоичным числом, соответствующим порядку старшего из минимальных полиномов, которое подается с выхода блока 12. Если двоичное число, которое подается на первый вход блока 20, меньше или равно двоичному числу, соответствующему порядку старшего из минимальных полиномов, то тогда на первом выходе Меньше или равно блока 20 появится сигнал, который обеспечивает подачу двоичного числа с выхода сумматора 19 через элемент И 21 на информационный вход регистра 13. Это двоичное число с вы- хода регистра 13 подается одновременно на вход старщих разрядов регистра 14 и на первый вход сумматора 19. С выходов регистра 14 сформированный новый адрес подается на вход блока

15.С выхода блока 15 выбранный новый полином подается на первый вход блока

16.В блоке 16 выбранный новый полином умножается на предыдущий. Результат умножения записывается в регистр

17.На второй вход сумматора 19 одно временно с десятого информационного входа подается двоичное число, соответствующее единице. Результат суммирования подается на второй вход эле- мента И 21 и первый вход блока 20.

В блоке 20 сравнивается двоичное число, соответствующее результату суммирования в сумматоре 19 с двоичным числом, соответствующим порядку стар- шего из минимальных полиномов, которое подается с выхода блока 12. Если двоичное число, которое подается на первый вход блока 20, меньше или равно двоичному числу, соответствующе.

му порядку старшего из минимальных полиномов, на первом выходе Меньше или равно блока 20 появляется сигнал, который обеспечивает подачу двоичного числа с выхода сумматора 19 через элемент И 21 на информационный вход регистра 13. Затем повторяется процедура выбора и умножения полиномов. Эта процедура продолжается до

Q J520 25зо

.-

. 35

,

50

55

тех пор, пока на втором выходе блока 20 Больше не появится сигнал. С появлением на втором выходе Больше блока 20 сигнала обеспечивается подача двоичного числа, соответствующего результату умножения полиномов, находящихся в регистре 17, через элемент И 18 на второй вход блока 22 и одновременно подача принятой кодовой комбинации, находящейся в регистре 32, через элементы И 33, ЮШ 34 на вход регистра 35. С выХода регистра 35 принятая кодовая комбинация подается одновременно на второй вход элемента И 36, информационный вход регистра 25 сдвига, который сдвигает информацию на один разряд влево и первый вход блока 22. В блоке 22 принятая кодовая комбинация делится на соответствующий выбранный образующий полином. С выхода блока 22 остаток от деления подается одновременно на первый вход элемента И 31 и управляю1 Л1й вход сложения счетчика 23. С выхода счетчика 23 вес остатка от деления подается на второй вход блока 24, на который также подается двоичное число, соответствующее количеству исправляемых ошибок с выхода блока 11 . В блоке 24 происходит сравнение количества исправляемых ошибок с весом остатка от деления. В случае, если количество исправляемых ошибок меньше, чем вес остатка от деления, на первом выходе блока 37 Меньше появляется сигнал, который подается одновременно на управляющий вход сложения счетчика 28, вход триггера 26 и на разрешающий вход регистра 25 сдвига на один разряд влево. После сдвига на один разряд влево с выхода рег истра 25 кодовая комбинация подается на первый вход элемента И 27. Одновременно с выхода триггера 26 разрешающий сигнал подается на второй вход элемента И 27. Этот сигнал обеспечивает подачу сдвинутой кодовой комбинации через элемент ИЛИ 29 на вход регистра 25, с выхода которого сдвинутая кодовая комбинация подается одновременно на второй вход элемента И 36, первый вход блока 22 и информационный вход регистра .25. В блоке 22 происходит деление сдвинутой кодовой комбинации на выбранный образующий полином. С выхода блока 22 остаток от деления подается одновременно на первый вход элемен

та И 31 и управляющий вход сложения счетчика 23. С выхола его вес остатка от деления подается на второй вход блока 24, где происходит сравнение количества исправляемых ошибок с весом остатка от деления. Н случае, если количество исправляемых ошибок меньше, чем вес остатка от деления, на первом выходе блока 24 Меньше появляется сигнал, который подается одновременно на разрешающий вход сложения счетчика 28, вход триггера 26 и на разрешающий вход регистра 25, После сдвига на один разряд влево с вы- хода регистра 25 вновь сдвинутая кодовая комбинация подается на первый вход элемента И 27. Одновременно с выхода триггера 26 решающий сигнал обеспечивает подачу с выхода элемента И 27 вновь сдвинутой кодовой комбинации на вход регистра 35 через элемент ИЛИ 34. Эта процедура повторяется до тех пор, пока в блоке 24 количество исправляемых ошибок будет больше или равно веса остатка от деления. С второго выхода блока 24 Больше или равно сигнал подается одновременно на первый вход элемента ИЛИ 29, второй вход элемента И 31 и второй вход элемента И 36. При этом остаток от деления подается на второй вход сум- матора 37 через И 31. Одновременно на nepijbiii вхо/ сумматора 37 подается пос-ледняя сдвинутая комбинация через :п И 36. С выхода сумматора 37 резульч суммирования подается на информационный вход регистра 38, в котором происходит сдвиг информации на один разряд вправо. В это время с выхода элемеята ИЛИ 29

на вход счетчика 38 подается унравляю дин сигнал вычитания, который обеспечивает вычитание единицы из подсчитанного числа, COOTветствующег о коли- lecTBy сдвиг ов в.ме Г . С вь;хода счетчика 28, соответствунщего ненулевому состоянию, сигнял подается одновременно на вход, триггера 30 и разрешающий вход регистра 33, яри этом происходит сдвиг одного разряда вправо. В это время с выхода триггера 30 через элемент ИЛИ 29 на вход счетчика 28 подается управляющий сигнал вычитания. Ио;:ле вторичного вычитания сигнал с выхода счетчика 28 подается одновременно на вход триггера 3fi и разрешаю1ций вход регистра 38, при этом происходит вт оричкый сдьиг одно

0

0

.25

30

35

40

го разряда вправо. Эта процедура продолжается до тех пор,пока на выходе, соответствующем нулевому состоянию счетчика 28, не появится сигнал. Этот сигнал обеспечивает подачу с выхода регистра 38 на вход выходного регистра 40 через элемент 39 и исправленной кодовой комбинации. С появлением запрещающего сигнала на первом управляющем входе устройство прекращает прием кодовой комбинации.

Отметим, что цифровая информа1Ц1я, и люльзуемая при работе устройства, представляется в двоичной системе счисления.

Введение блока 15 постоянной памяти, блока 7 логарифмирования по основанию два, блоков 4, 10 и 12 вычитания и блоков 20 и 24 сравнения позволяет осуществить автоматическое получение образующего полинома для различных кодовых расстояний кодов ЬЧХ. Выбор образующего полинома позволяет осуществлять исправления ошибок соответ -твующей кратности за счет введения регистров 25 и 38 сдвига, реверсивного счетчика 28. Исправление ошибок различной кратности производится путем сравнения веса остатка от деления принимаемой кодовой комбинации на полученный образующий полином с кратностью исправляемой ошибки, что значительно повышает корректирующую способность предлагаемого устройства и автоматически приводит к повьш1ению достоверности контроля. Кроме того, устройство может исправлять , ошибки любой кратности, соответствующей таблице минимальных полиномов, хранимой в блоке 15.

формула изобретения

Устройство для исправления ошибок кодов Боуза-Чоудхури-Хоквингема, содержащее входной регистр, вход которого является первым информационным входом устройства, первый элемент И, выход которого п одключен к входу выходного регистра, выходы которого являются выходами устройства, первый регистр сдвига, тактовый вход которого объе/;инен с входом первого триггера, первый и второй счетчики импульсов, BTopoii триггер, первый и второй элементы ШШ, первый и второй блоки деления, отличающееся

тем, что, с целью повышения помехо- усугойчивости устройства, в него введены второй регистр сдвига, третий счетчик импульсов, реверсивный счетчик, регистр адреса, блок постоянной памяти, второй - седьмой элементы И, блок логарифмирования, блоки сравнения, регистры, сумматоры, третий ;блок деления, блоки вычитания и бло- ки умножения, первые и вторые входы первого и нторого счетчиков импульсов попарно объединены и подключены соответственно к первому информационному и первому управляющему входам устройства, выходы первого и второго счетчиков импульсов и входного регисра подключены соответственно к первому и второму входам парного сумматора и первому входу второго элемента И, выход которого соединен с первым входом первого элемента HJIH, выход которого соединен с входом первого регистра, вьгход которого подключен к первому входу первого блока деления, информационному входу первого регистра сдвига к первому входу третьего элемента И, выход которого подключен к первому входу второго сумматора, выход которого соединен с информаци- онным входом второго регистра сдвига выход которого соединен со своим входом обнуления и первым входом первог элемента И, выход первого сумматора подключен к первым входам третьего сумматора и первого блока вычитания, вторые входы которых являются соответственно третьим и вторым информа- ционныйи входами устройства, выход первого блока вычитания подключен к первому входу первого блока умножения второй вход которого является четвертым информационным входом устройства а выход соединен с первым входом второго деления, выход третье- го сумматора через блок логарифмирования соединен с входом младших разрядов регистра адреса и вторым входом второго блока деления, выход которого подключен к первому входу четвертого сумматора, второй вход которого является информационным входом устройства, а выход соединен с первыми входами второго и третьего блоков вычитания, вторые входы которых являются соответс;твеино шестым и седьмым информационными входами устроства, выходы irropDi L) и третьего блоков вычитания П(.);1к.:|К1Ч( соответствен

Q г ,. 5 о 5

0

0

5

но к первым входам первого блока сравнения и третьего блока деления, второй вход которого является восьмым информационным входом устройства, а выход подключен к первому входу второго блока сравнения, первый выход которого соединен с вторым входом третьего элемента И и первыми входами четвертого элемента И и второго элемента ИЛИ, выходы которых подключены соответственно к второму входу второго сумматора и вычитающему входу реверсивного счетчика, первый выход которого через второй триггер соединен с вторым входом второго элемента ИЛИ и непосредственно подключен к тактовому входу второго регистра сдвига, первый выход первого блока сравнения соединен с вторым входом второго элемента И и первым входом пятого элемента И, выход которого подключен к второму входу первого блока деления, выход которого соединен с вторым входом четвертого элемента И и информационным входом третьего счетчика импульсов,, тактовый вход которого является первым синхронизирующим входом устройства, а выход подключен к второму входу второго блока сравнения, второй выход которого подключен к входу первого триггера и суммирующему входу реверсивного счетчика, тактовый вход которого является вторым синхронизи- РУЮ1ЦИМ входом устройства, выход подключен к второму входу первого элемента И, выход первого регистра сдвига подключен к своему входу обнуления и первому входу шестого элемента И, второй вход и выход которого соединены соответственно с выходом перво- го триггера и вторым входом первого элемента ИЛИ, второй выход первого блока сравнения подключен к первому входу седьмого элемента И, выход которого подключен к информационному входу второго регистра, тактовый 1ВХОД которого является вторым управля- |ю1цим входом устройства, а выход сое- |Динен с первым входом пятого сумматора и входом старших разрядов регистра адреса, выходы которого подключены к входам блока постоянной памяти, выход которого соединен с первым входом второго блока умножения, выход которого подключен к первому входу третьего регистра, второй вход которого является девятым информационным входом устройства, а выход подключен к

вторым входам пятого элемента И и второго блока умножения, второй вход пятого сумматора является десятым информационным входом устройства, а с

выход подключен к вторым входам первого блока сравнения и седьмого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для повышения достоверности обработки и передачи дискретной информации. Цель изобретения - повышение помехоустойчивости устройства. Устройство для исправления ошибок кодов Боуза-Чоудхури-Хоквинима содержит датчики 1,2 и 23 импульсов, сумматора 3,5,8,19 и 37, блоки 4,10 и 12 вычитания, блоки 6 и 16 умножения, блок 7 логарифмирования, блоки 8,11 и 22 деления, блоки 20 и 24 сравнения, элементы И 18,21,27,31,39,33 и 36, регистры 35,13,17, регистры 25 и 38 сдвига, входной и выходной регистры 32 и 40, элементы ИЛИ 29 и 34, триггеры 26 и 30, реверсивный счетчик 28, регистр 14 адреса и блок 15 постоянной памяти. 2 ил.

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1115055A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для исправления двойных и обнаружения многократных ошибок циклическими кодами | 1983 |

|

SU1185611A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-23—Публикация

1987-07-09—Подача