Hf

я е 1- JJ- 3Пг

-йгОтОт®

гг

2

У

Од

сд

W

гОтОт®

+

У

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ, осуществляющих параллельное суммирование чисел, представленных в кодах с иррациональными основаниями, с получением суммы в минимальной форме

Цель изобретения - повышение быстродействия.

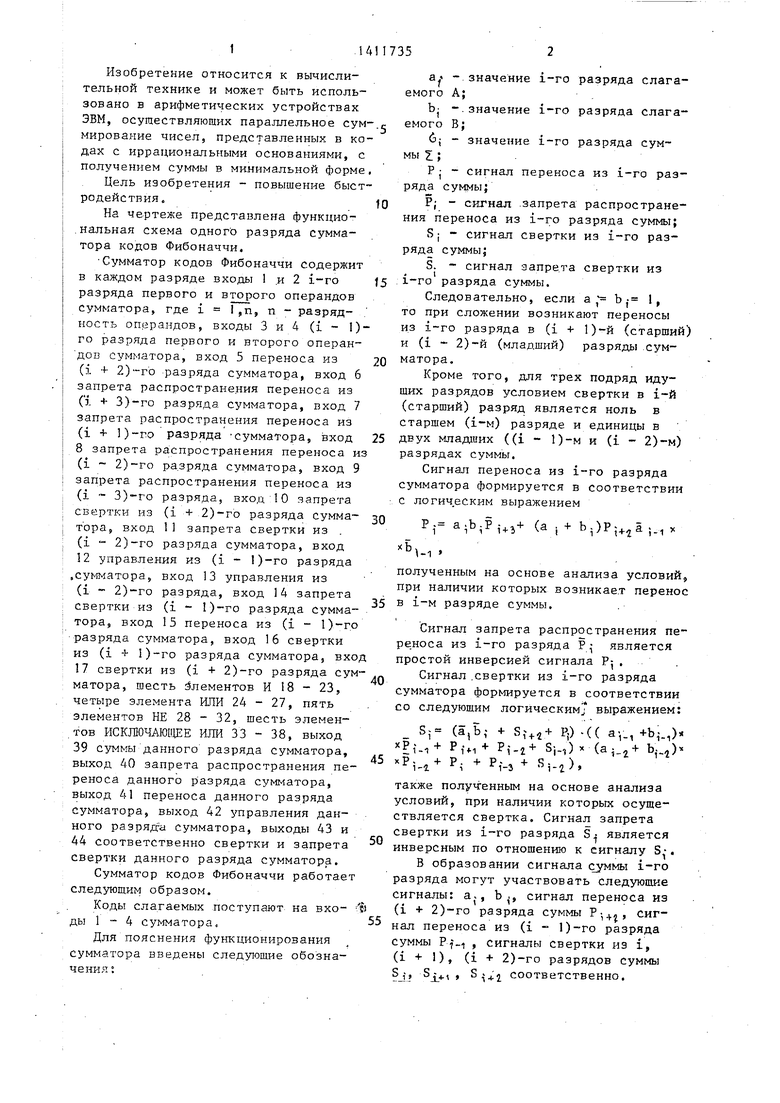

На чертеже представлена функцио- .нальная схема одного разряда сумматора кодов Фибоначчи.

Сумматор кодов Фибоначчи содержит в каждом разряде входы 1 и 2 i-ro разряда первого и второго операндов сумматора, где i 1,п, п - разрядность операндов, входы 3 и 4 (i - I)- го разряда первого и второго операн- дов сумматора, вход 5 переноса из (i + 2)-го разряда сумматора, вход 6 запрета распространения переноса из (1 3)-го разряда сумматора, вход 7 запрета распространения переноса из (1 + 1)го разряда сумматора, вход 8 запрета распространения переноса из (i 2)го разряда сумматора, вход 9 запрета распространения переноса из (i - 3)-го разряда, вход 10 запрета свертки из (i + 2)-го разряда сумма- тора, вход 11 запрета свертки из . (i - 2)-го разряда сумматора, вход 12 управления из (i - 1)-го разряда .сумматора, вход 13 управления из (i - 2)-го разряда, вход 14 запрета свертки из (i - Г)-го разряда сумматора, вход 15 переноса из (i - 1)-го разряда сумматора, вход 16 свертки из (i -I- )-го разряда сумматора, вход 17 свертки из (i + 2)-го разряда сумматора, шесть Элементов И 18 - 23, четыре злемента ИЛИ 24 - 27, пять элементов НЕ 28 - 32, шесть элементов ИСКЛЮЧАЮ1ЦЕЕ ИЛИ 33 - 38, выход

39 суммы данного разряда сумматора, J

выход 40 запрета распространения переноса данного разряда сумматора, выход 41 переноса данного разряда сумматора, выход 42 управления данного разрядка сумматора, выходы 43 и 44 соответственно свертки и запрета свертки данного разряда сумматора.

Сумматор кодов Фибоначчи работает следующим образом.

Коды слагаемых поступают на вхо- Ф ды 1 - 4 сумматора,

Для пояснения функционирования сумматора введены следующие обозначения:

0

5 0 5 : о

... 5

5

0

а. - значение 1-го разряда слагаемого А;

bj .значение i-ro разряда слагаемого В;

6| - значение i-ro разряда суммы Z ;

PJ - сигнал переноса из 1-го разряда суммы;

Р; - сигнал .запрета распространения переноса из i-ro разряда суммы;

Sj - сигнал свертки из i-ro разряда суммы;

S. - сигнал запрета свертки из i-ro разряда суммы.

Следовательно, если а, Ь,- 1, то при сложении возникают переносы из i-ro разряда в (i + 1)-й (старший) и (i - 2)-и (младший) разряды .сумматора.

Кроме того, для трех подряд идущих разрядов условием свертки в i-й (старший) разряд, является ноль в старшем (i-м) разряде и единицы в двух младших ((1 - 1)-м и (i - 2)-м) разрядах суммы.

Сигнал переноса из i-ro разряда сумматора формируется в соответствии с логич.еским выражением

Рр а.Ь.Р,чз+ (а i + b.)P;,ja;., X

.

полученным на основе анализа условий, при наличии которых возникае.т перенос в i-M разряде суммы.

Сигнал запрета распространения переноса из i-ro разряда Р , является простой инверсией сигнала Р|.

Сигнал .свертки из i-ro разряда сумматора формируется в соответствии со следующим логическим; выражением:

S- (a,b,- 4- 8,42+ ф (( а-,., +Ь.,)« хР,-., + Р,.,1+ Р,--2+ Sj-O (ai,j+ b-.j) хР,,+ p. + Р,-.з + 8,,),

также получ енным на основе анализа условий, при наличии которых осуществляется свертка. Сигнал запрета свертки из i-ro разряда §.| является инверсным по отношению к сигналу . В образовании сигнала суммы i-ro разряда могут участвовать следуюпше сигналы: a, Ь, сигнал переноса из (i + 2)-го разряда суммы Р-,.).., сигнал переноса из (i - 1)-го разряда суммы Pf , сигналы свертки из i, (i + ), (i + 2)-го разрядов суммы S,-, соответственно.

.3lAIi

Следовательно, значение i-го разряда суммы определяется значениями перечисленных сигналов (точнее наличием каких-либо из них либо отсут- , ствием).

Таким образом 6,. а, ФЬ; ©Р.,® Р.., ©S; €)

S-,,® S;,, .

Сумматор кодов Фибоначчи позволяет получать сумму кодов Фибоначчи в минимальной форме за один такт.

Формула изобретения

Сумматор код ов Фибоначчи, содержащий в каждом разряде первый, второй, третий, четвертый элементы И, первый, второй, третий, четвертый элементы ИЛИ, первый, второй, третий элементы НЕ, причем входы i-ro разряда перво- го и второго операндов, где i ,п, п - разрядность операндов, сумматора соединены соответственно с первым и вторым входами первого элемента И данного разряда сумматора, вход переноса из (i + 2)-го разряда сумматора соединен с первым входом второго элемента И i-ro разряда сумматора, вход запрета распространения переноса из (i + 1)-го разряда сумматора соединен с первым входом третьего элемента И i-ro разряда сумматора, отличающийся тем, что, с целью повышения быстродействия, в каждый разряд сумматора кодов Фибоначчи вве- дейы пятый, шестой элементы И, четвертый, пятый элементы НЕ, первьй, второй, третий, четвертый, пятый, шестой элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, при- чем третий вход первого элемента И соединен с входом запрета распространения переноса из (i + 3)-го разряда сумматора, второй вход второго элемента И соединен с выходом первого элемента НЕ, вход которого соединен с входом (i - 1)-го разряда, первого операнда сумматора, вход (i - 1)-го разряда второго операнда сумматора соединен с входом второго элемента НЕ, вькод которого соединен с третьим входом второго элемента И, 4eTBeptbrii вход которого соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход которого соединен с первым входом пятого элемента И, выхо

,

0

5

0

5

0

5

0

5

0

5

735

дом запрета распространения переноса данноЬо разряда сумматора и выходом третьего элемента НЕ, вход которого соединен с выходом переноса данного разряда сумматора и выходом второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходом первого элемента И,и выходом второго элемента И, вход разряда первого операнда сумматора соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом первог о элемента ИЛИ, второй вход которого соединен с входом i-ro разряда второго операнда сумматора и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом свертки из (i + 2)-го разряда сумматора, вход переноса из (1 + 2)-го разряда сумматора соединен с вторым входом первого элемента ИСКЛЮЧАЮП1ЕЕ ИЛИ, выход которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с выходом суммы данного разряда сумматора вход переноса из (1 - 1)-го разряда

--Сумматора и вход свертки из (i - O-TO разряда сумматора соедине ны соответственно с первым и вторым входат пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с пеовым входом шестого элемента ИСКЛЮЧАЮ ЦЕЕ 1ЛИ,, второй вход и выход которого соедине-. ны соответственно с выходом второго

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-и.вторым

вхо дом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход запрета свертки ) тора из (i + 2)-го разряда сумматораГ соединен с первым входом шестого элемента И, второй вход которого сое динен с выходом четвертого элемента И и входом четвертого элемента НЕ,, выход которого соединен с выходом управления данного разряда сумматора вход управления из (i -1)-го разряда сумматора, вход здпрета распространения переноса из (i - 2)-го разряда . сумматора, вход запрета свертки из (i - 1)-го разряда сумматора соединены, соответственно с вторьм, третьим, четвертьш входами третьего эле-- мента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И. второй,

5иП7356

третий, четвертый входы котороговетственно с первым и вторым входа- соединены соответственно с входом уп-ми четвертого элемента ИЛИ, выход правления из (i - 2)-го разряда сумма-которого соединен с выходом запрета тора, с входом запрета распростране-свертки данного разряда сумматора и ния переноса из (1 - 3)-го разрядавходом пятого элемента НЕ, выход ко- сумматора и входом запрета сверткиторого соединен с вторым входом тре- из (1 - 2)-го разряда сумматора, вы-тьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход шестого элемента И н выход тре-ходом свертки данного разряда сумма- тьего элемента ИЛИ соединены соот- ютора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для сложения п-разрядных десятичных чисел | 1980 |

|

SU900282A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Сумматор кодов Фибоначчи | 1987 |

|

SU1532915A1 |

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1988 |

|

SU1547073A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

Изобретение относится к области вычислительной техники и может быть использовано для суммирования кодов Фибоначчи с представлением результата суммирования в минимальной форме. Цель изобретения - повышение быстродействия. Сумматор кодов Фибоначчи содержит в каждом разряде шесть элементов И.18 - 23, четыре злемента ИЛИ 24 - 27, пять элементов НЕ 28 - 32, шесть элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 33 - 38. Сумматор кодов Фибоначчи может осуществлять кон яроль суммы, основанный на том, что появление результата суммирования в неминимальной форме свидетельствует о наличии отказа либо в неисправности в схеме. I ил.:

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор кодов с иррациональным основанием | 1982 |

|

SU1083182A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-12—Подача