(/

СП

со to со vl 1

второй счетные триггеры 12, 13, инверторы блока записи 14, 15, первый и второй элементы И-НЕ 16, 17, элемент И 18, триггер 19 индикации окон- чания записи, состоящий из элемента И-ИЛИ-НЕ и инвертора,.МОП-транзисторы 20-22 блока записи, нагрузочные элементы 23, 24 блока записи, вход 25 разрешения чтения, вход 26 раз- решения записи, вход 27 начальной установки, информационный вход 28, выход 29 индикации окончания чтения,j выход 30 индикации окончания записи. Запись и чтение информации могут осуществляться в произвольные моменты времени независимо друг от друга. Условия выполнения этих операций делают невозможным одновременную запись и чтение, информации из одного и того же элемента памяти блока 1 и обеспечивают перед элементом памяти, в который осуществляется запись, как минимум еще один очищенный элемент, памяти, а перед элементом памяти, из которого осуществляется чтение, как минимум еще один элемент памяти с записанной в него информацией. При чтении пустого запоминающего устрой- ства или записи в заполненное устройство переходные процессы чтения или записи не будут завершены до тех пор, пока не пройдет соответственно процессы записи или чтения. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1411823A2 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1658159A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| ИНТЕГРИРОВАННАЯ В СБИС ТЕХНОЛОГИИ КМОП/КНИ С n+ - И p+ - ПОЛИКРЕМНИЕВЫМИ ЗАТВОРАМИ МАТРИЦА ПАМЯТИ MRAM С МАГНИТОРЕЗИСТИВНЫМИ УСТРОЙСТВАМИ С ПЕРЕДАЧЕЙ СПИНОВОГО ВРАЩЕНИЯ | 2012 |

|

RU2515461C2 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1709325A1 |

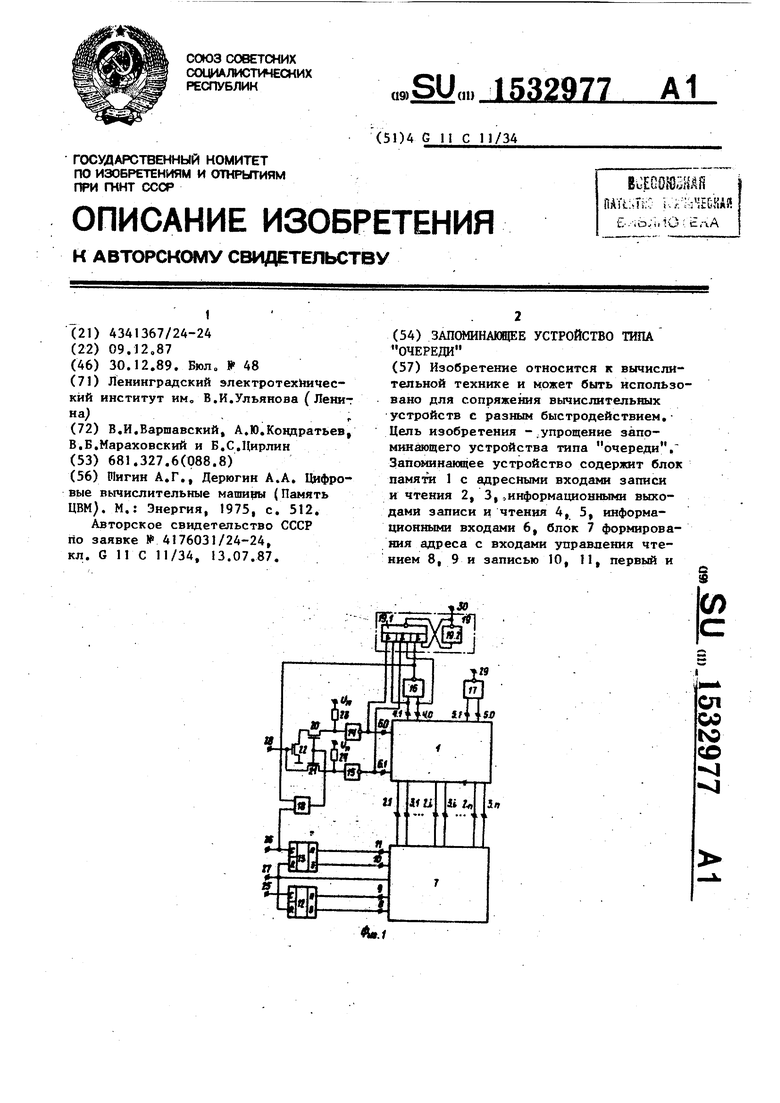

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств с разным быстродействием. Цель изобретения - упрощение запоминающего устройства типа "очереди". Запоминающее устройство содержит блок памяти 1 с адресными входами записи и чтения 2, 3, информационными выходами записи и чтения 4, 5, информационными входами 6, блок 7 формирования адреса со входами управления чтением 8, 9 и записью 10, 11, первый и второй счетные триггеры 12, 13, инверторы блока записи 14, 15, первый и второй элементы И-НЕ 16, 17, элемент И 18, триггер 19 индикации окончания записи, состоящий из элемента И-ИЛИ-НЕ и инвертора, МОП-транзисторы 20-22 блока записи, нагрузочные элементы 23, 24 блока записи, вход 25 разрешения чтения, вход 26 разрешения записи, вход 27 начальной установки, информационный вход 28, выход 29 индикации окончания чтения, выход 30 индикации окончания записи. Запись и чтение информации могут осуществляться в произвольные моменты времени независимо друг от друга. Условия выполнения этих операций делают невозможным одновременную запись и чтение информации из одного и того же элемента памяти блока 1 и обеспечивают перед элементом памяти, в который осуществляется запись, как минимум, еще один очищенный элемент памяти, а перед элементом памяти, из которого осуществляется чтение, как минимум, еще один элемент памяти с записанной в него информацией. При чтении пустого запоминающего устройства или записи в заполненное устройство переходные процессы чтения или записи не будут завершены до тех пор, пока не пройдут соответственно процессы записи или чтения. 4 ил.

Изобретение относится к вычислительной g технике и может быть использовано для сопряжения вычислительных устройств с разным быстродействием.

Цель изобретения - упрощение запоминающего устройства типа очереди.

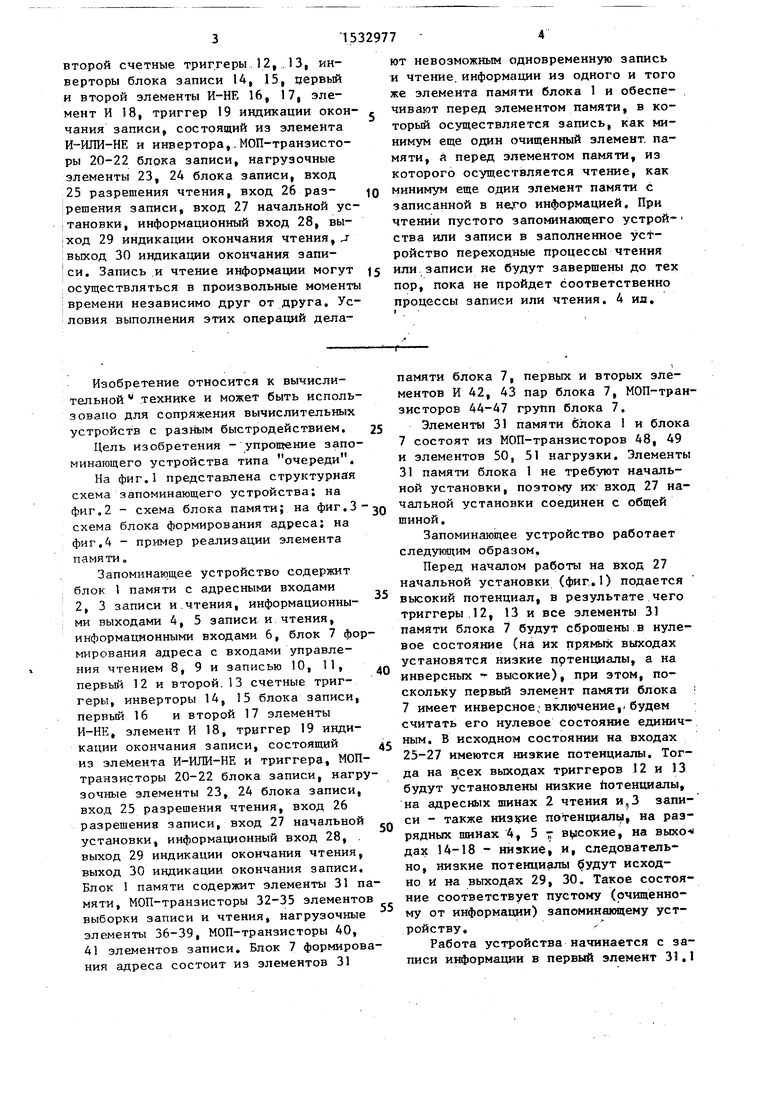

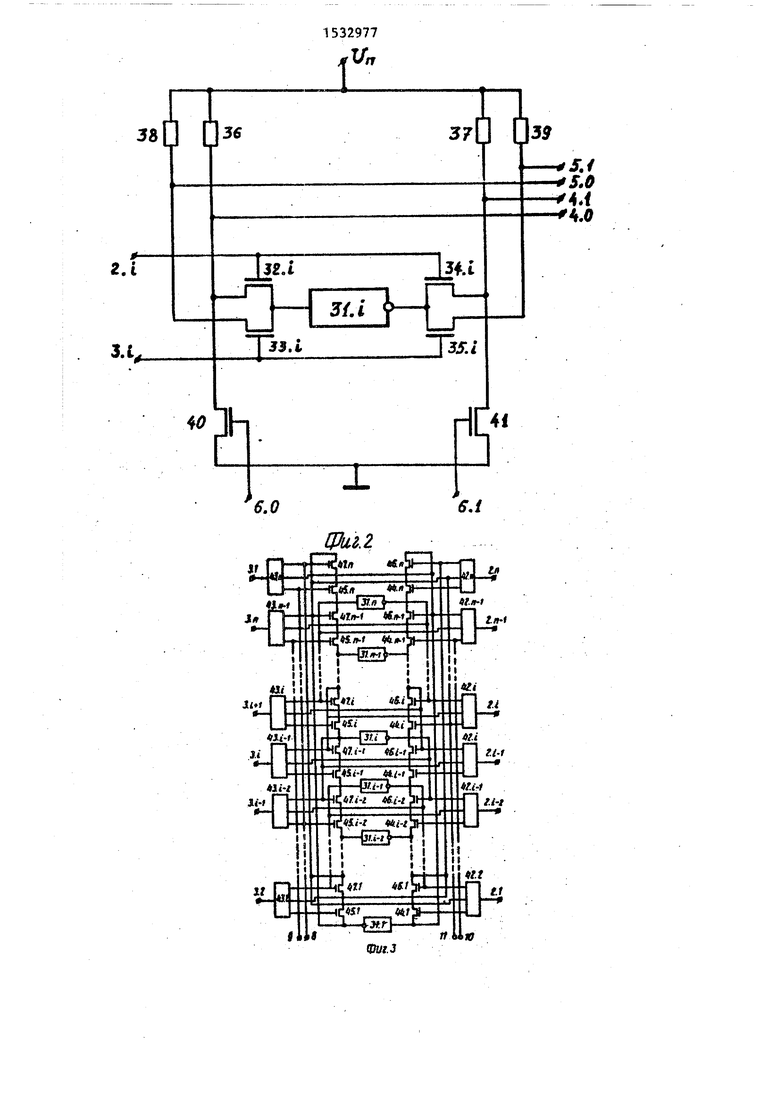

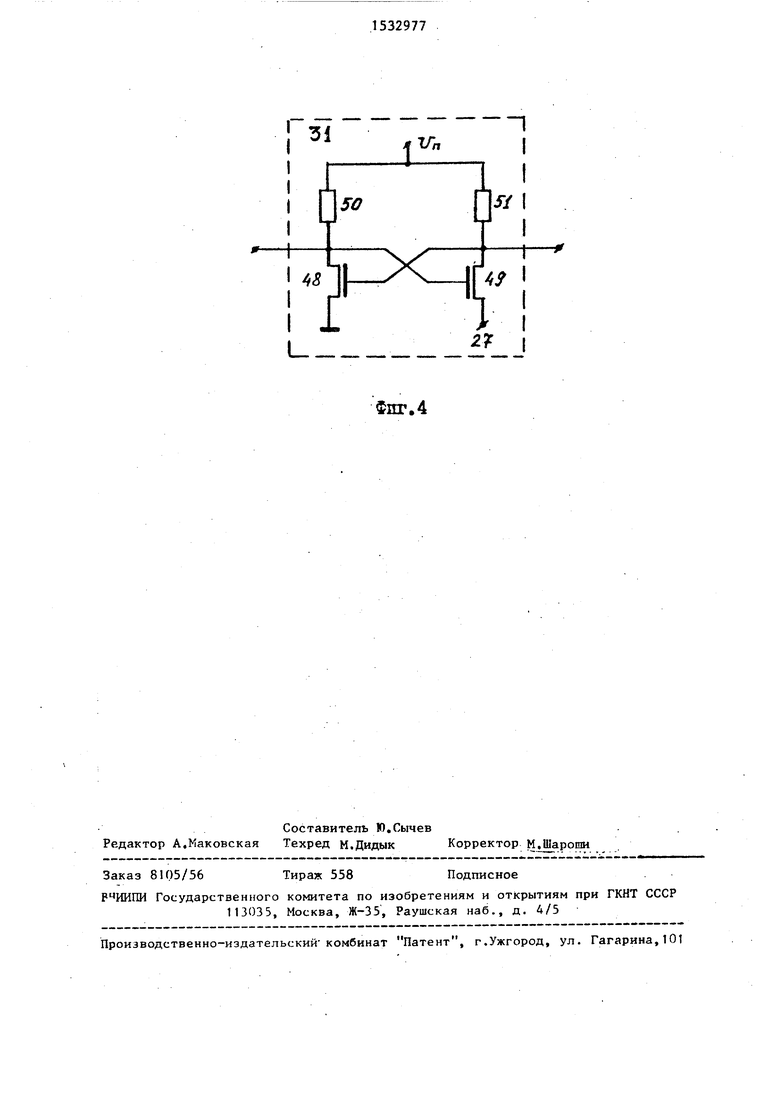

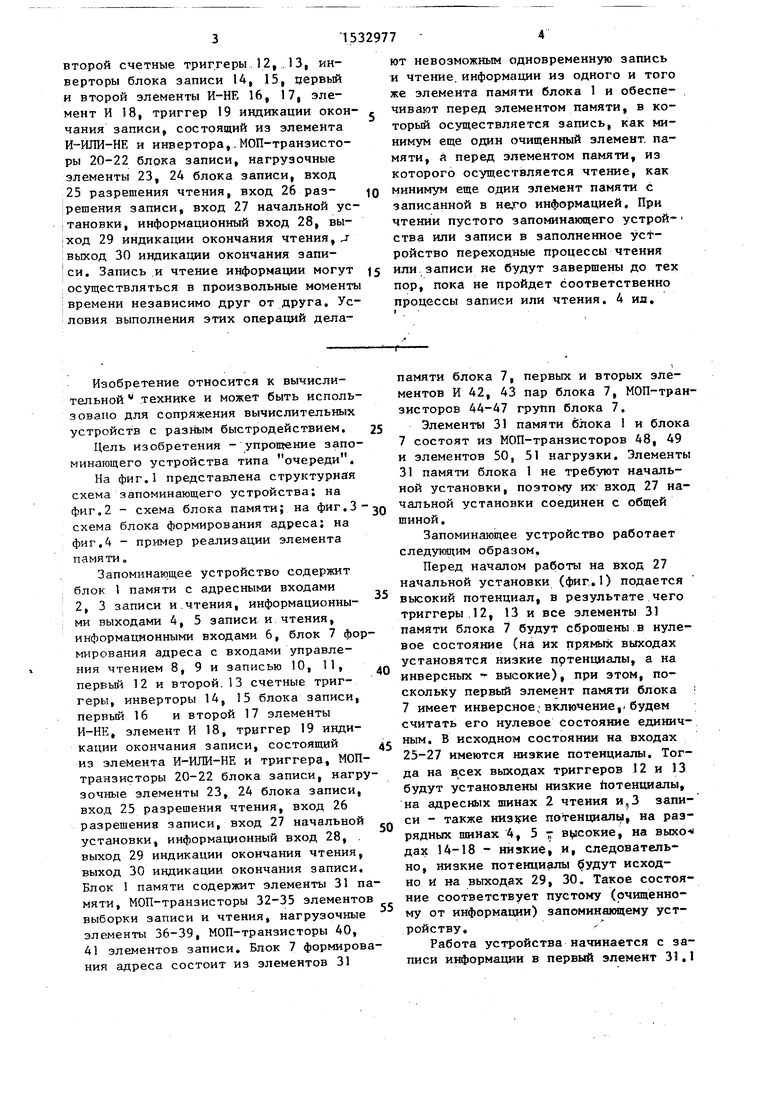

На фиг.1 представлена структурная схема запоминающего устройства; на фиг.2 - схема блока памяти; на фиг.З- схема блока формирования адреса; на фиг.4 - пример реализации элемента памяти.

Запоминающее устройство содержит блок I памяти с адресными входами 2, 3 записи и чтения, информационными выходами 4, 5 записи и чтения, информационными входами 6, блок 7 формирования адреса с входами управления чтением 8, 9 и записью 10, 11, первьй 12 и второй.13 счетные триггеры, инверторы 14, 15 блока записи, первый 16 и второй 17 элементы И-НЕ, элемент И 18, триггер 19 индикации окончания записи, состоящий из элемента И-ИЛИ-НЕ и триггера, МОП- транзисторы 20-22 блока записи, нагрузочные элементы 23, 24 блока записи, вход 25 разрешения чтения, вход 26 разрешения записи, вход 27 начальной установки, информационный вход 28, выход 29 индикации окончания чтения, выход 30 индикации окончания записи. Блок 1 памяти содержит элементы 31 памяти, МОП-транзисторы 32-35 элементов выборки записи и чтения, нагрузочные элементы 36-39, МОП-транзисторы 40, 41 элементов записи. Блок 7 формирования адреса состоит из элементов 31

5

0

5

0

5

0

5

памяти блока 7, первых и вторых элементов И 42, 43 пар блока 7, МОП-транзисторов 44-47 групп блока 7.

Элементы 31 памяти блока 1 и блока 7 состоят из МОП-транзисторов 48, 49 и элементов 50, 51 нагрузки. Элементы 31 памяти блока 1 не требуют начальной установки, поэтому их вход 27 начальной установки соединен с общей шиной.

Запоминающее устройство работает следующим образом.

Перед началом работы на вход 27 начальной установки (фиг.1) подается высокий потенциал, в результате чего триггеры 12, 13 и все элементы 31 памяти блока 7 будут сброшены в нулевое состояние (на их прямых выходах установятся низкие пртенциалы, а на инверсных высокие), при этом, поскольку первый элемент памяти блока 7 имеет инверсноеvвключение,, будем считать его нулевое состояние единичным. В исходном состоянии на входах 25-27 имеются низкие потенциалы. Тогда на всех выходах триггеров 12 и 13 будут установлены низкие потенциалы, на адресных шинах 2 чтения и,3 записи - также низкие потенциалы, на разрядных шинах 4, 5 - высокие, на выхо дах 14-18 - низкие и, следовательно, низкие потенциалы 5удут исходно и на выходах 29, 30. Такое состояние соответствует пустому (очищенному от информации) запоминающему устройству.

Работа устройства начинается с записи информации в первый элемент 31.1

памяти блока I. Для этого информация выставляется на вход 28 (фиг.1), а на вход 26 подается высокий потенциал, в результате чего переключается,/ триггер 13 и на его выходе заема,.. т.е. на входе 10 блока 7, появляется высокий потенциал. Этот потенциал поступает на третий вход элемента Ј2.1, и на затвор МОП-транзистора 44.1, который открывается, при этом низкий. потенциал с выхода элемента 31.1 блока 7 через открытые МОП-транзисторы 41.1 и 46.1 поступит на инверсный

вход выход элемента 31.2 блока 7, что 15 торы 40 и 41 (фиг.2). Низкий потенцивызывст переключение последнего в единичное состояние, и на его прямом входе - выходе установится высокий потенциал, который вызовет появление такого же потенциала на втором входе элемента 42.1. Поскольку на первом- входе этого элемента также находится высокие потенциал, снимаемый с инал на выходе эаема триггера 13, т на входе 10 блока 7, приводит к пе ключению элемента 42.1 (фиг.З) и п лению низкого потенциала на выходе 20 2.1 первого адреса записи. Закрыва ся МОП-транзисторы 32 и 34 первого элемента памяти блока 1 (фиг,2), н разрядных шинах 4 появляются высок

версного выхода триггера 31.3, то эле-- потенциалы, на выходе элемента 16

мент 42.1 сработает и на адресной шине 2.1 появится высокий потенциал, который откроет МОП-транзисторы 32,1 и 34.1 элемента 31.1 памяти блока 1 (фиг.2). При этом низкий потенциал с одного из входов-выходов триггера 31.1 блока 1 поступит на одну из разрядных шин 4 записи, в результате t чего переключится элемент 16 (фиг.1), и высокий потенциал с его выхода, пройдя через элемент 18, откроет МОП-транзисторы 20 и 21, после чего переключится один из инверторов 14 или 15 и на одном из информационных, входов 6 появится высокий потенциал, который откроет один из МОП-транзисторов 40 или 41 (фиг.2). Если информация, записываемая в элемент 31.1 памяти блока 1.совпадает с хранимой в нем до этого, то процесс записи на этом заканчивается, в противном случае происходит переключение элемента 31.1 памяти блока , при котором низкий потенциал появляется сначала на обеих разрядных шинах 4 записи, а потом остается только на одной из них, В любом случае признаком окончания записи информации является совпадение высоких потенциалов на входе 6.1 и шине 4.0 или на входе 6.0 и шине 4,1. После этого произойдет Переключение триггера 19 (фиг.1), в результате которого на выходе 30 появится высокий потенциал, что является признаком окончания переход 25 (фиг.1) - низкий потенциал, в резу тате чего переключается триггер 19 на выходе 30 появляется низкий пот циал, что является признаком оконч ния переходных процессов во второй

30 фазе записи. Таким образом, запоми ющее устройство оказалось в состоя аналогичном исходному, с той лишь ницей что в его первом элементе 31 памяти блока 1 записана информация

35 элемент 31.2 памяти блока 7 и триг 13 находятся в единичном состоянии

Следующая подача высокого потен ала на вход 26 вызовет появление в кого потенциала на выходе переноса

40 триггера 13, т.е. на входе 11 блок 7. Этот потенциал откроет МОП-тран тор 44.2 (фиг.З) и низкий потенциа с инверсного выхода элемента 31.2 блока 7 через открытые МОП-транзи

45 торы 44.2 и 46.2 поступит на инвер ный вход - выход элемента 31.3 бло 7, что вызовет переключение послед го в единичное состояние, которое зовет срабатывание элемента 42.2,

50 на адресной шине 2,2 записи появится высокий потенциал. Далее происхо дит запись информации во.второй эл мент 31.2 памяти блока 1, и переход ный процесс в устройстве завершаетс

55 появлением высокого потенциала на выходе 30 (фиг.1).

После этого на входе 26 вновь во станавливается низкий потенциал и устройство опять возвращается в со

ных процессов писи.

После появления на выходе 30 высо- кого потенциала на входе 26 снова восстанавливается низкий потенциал, в результате чего на выходе элемента 18 и на выходе заема триггера 13 появляются низкие потенциалы. Низкий потенциал на выходе элемента,18 закрывает МОП-транзисторы 20 и 21, на входах инверторов 14 и 15 появляются высокие а на их выходах - низкие потенциалы, которые закрывают входные МОП- транзисал на выходе эаема триггера 13, т,е, на входе 10 блока 7, приводит к переключению элемента 42.1 (фиг.З) и появлению низкого потенциала на выходе 2.1 первого адреса записи. Закрывают ся МОП-транзисторы 32 и 34 первого элемента памяти блока 1 (фиг,2), на разрядных шинах 4 появляются высокие

потенциалы, на выходе элемента 16

(фиг.1) - низкий потенциал, в результате чего переключается триггер 19 и на выходе 30 появляется низкий потенциал, что является признаком окончания переходных процессов во второй

фазе записи. Таким образом, запоминающее устройство оказалось в состоянии, аналогичном исходному, с той лишь разницей что в его первом элементе 31.1 памяти блока 1 записана информация,

элемент 31.2 памяти блока 7 и триггер 13 находятся в единичном состоянии.

Следующая подача высокого потенциала на вход 26 вызовет появление высокого потенциала на выходе переноса

триггера 13, т.е. на входе 11 блока 7. Этот потенциал откроет МОП-транзистор 44.2 (фиг.З) и низкий потенциал с инверсного выхода элемента 31.2 блока 7 через открытые МОП-транзисторы 44.2 и 46.2 поступит на инверсный вход - выход элемента 31.3 блока - 7, что вызовет переключение последнего в единичное состояние, которое вызовет срабатывание элемента 42.2, и

на адресной шине 2,2 записи появится высокий потенциал. Далее происходит запись информации во.второй элемент 31.2 памяти блока 1, и переходный процесс в устройстве завершается

появлением высокого потенциала на выходе 30 (фиг.1).

После этого на входе 26 вновь вое станавливается низкий потенциал и устройство опять возвращается в состояние, аналогичное исходному, однако теперь информация записана уже в первой и втором эдементах памяти блока 1 . в единичном состоянии будут . Триггеры 31.1, 32,2 и 32,3 блока 7, а триггер 13 снова окажется в нулевом состоянии. Признаком завершения Процесса возврата устройства в это . состояние является появление низкого потенциала на выходе 30.

Для чтения информации на вход 25 Додается высокий потенциал, в резуль- ате чего переключается триггер 12 и на его выходе заема, т.е. на входе 8 блока 7, появляется высокий потенциал, который открывает МОП-транзистор 45.п, и низкий потенциал с прямого ыхода элемента 31.п блока 7 через бткрытые МОП-транзисторы 45.п и 47.п поступает на инверсный вход - выход флемента 31.1 блока 7, вызывая переключение триггера 31.1 блока 7. На прямом выходе этого триггера появляется высокий потенциал, который приводит к срабатыванию элемента 43 ,п и появлению высокого потенциала на Адресной шине 3.1. чтения. Условием Переключения триггера 31.1 блока 7 является единичное состояние тригге- ра 31.2 блока 7, высокий потенциал t прямого выхода которого открывает , МОП-транзистор 47,п, т.е. необходимо, чтобы была предварительно записана Информация в элемент памяти 31,1 бло- Ка 1 (без записи не может быть чте- Ния). Высокий потенциал на адресной йшне 3.1 чтения открывает МОП-транзисторы 33.1 и 35.1 (фиг.2), низкий потенциал с одного из выходов элемен- та 31„1 памяти блока 1 поступает на соответствующую шину 5.0 или 5.1, в результате чего на выходе элемента 17 (фиг.1), т.е. на выходе 29 устройства, появляется высокий потенциал, что.является признаком окончания переходных процессов первой фазы чтения.

После этого на входе 25 восстанавливается низкий потенциал, в резуль- тате чего на выходе заема триггера 12 появляется низкий потенциал, который, поступив на вход 8 блока 7, приводит к появлению высокого,потенциала на выходе элемента 43.п, т.е. на адресной шине 3.1 чтения, из-за чего закроются МОП-транзисторы 33.1 и 35.1 (фиг.2) и на обеих разрядных шинах 5 восстановятся высокие потенциалы, что вызовет появление низкого потенциала на выходе элемента 17 (фиг,1), т.е. на выходе 29 устройст- за, последнее является признаком окончания переходных процессов второй фазы чтения. По завершении этой фазы устройство находится в состоянии, аналогичном исходному, причем первый элемент 31.1 памяти блока 1 очищен, а триггер 12 находится в единичном состоянии.

Следующая подача высокого потенциала на вход 25 вызовет появление высокого потенциала на выходе переноса триггера 12, т.е. на входе 9 блока 7, При этом откроется МОП-транзистор 45.1 (фиг.З).и, если открыт транзистор 47.1, что соответствует единичному состоянию элемента 31.3 блока 7, то низкий потенциал с выхода элемента 31.1 блока 7 попадает на прямой вход - выход элемента 31,2 - блока 7 и переводит этот элемент в нулевое состояние, что вызовет чтение из элемента 31.2 памяти блока 1, которое завершится появлением высокого потенциала на выходе 29 устройства.

После этого на входе 25 снова восстанавливается низкий потенциал и устройство переходит в состояние, аналогичное исходному,что завершается появлением низкого потенциала на выходе 29.

Формула изобретения

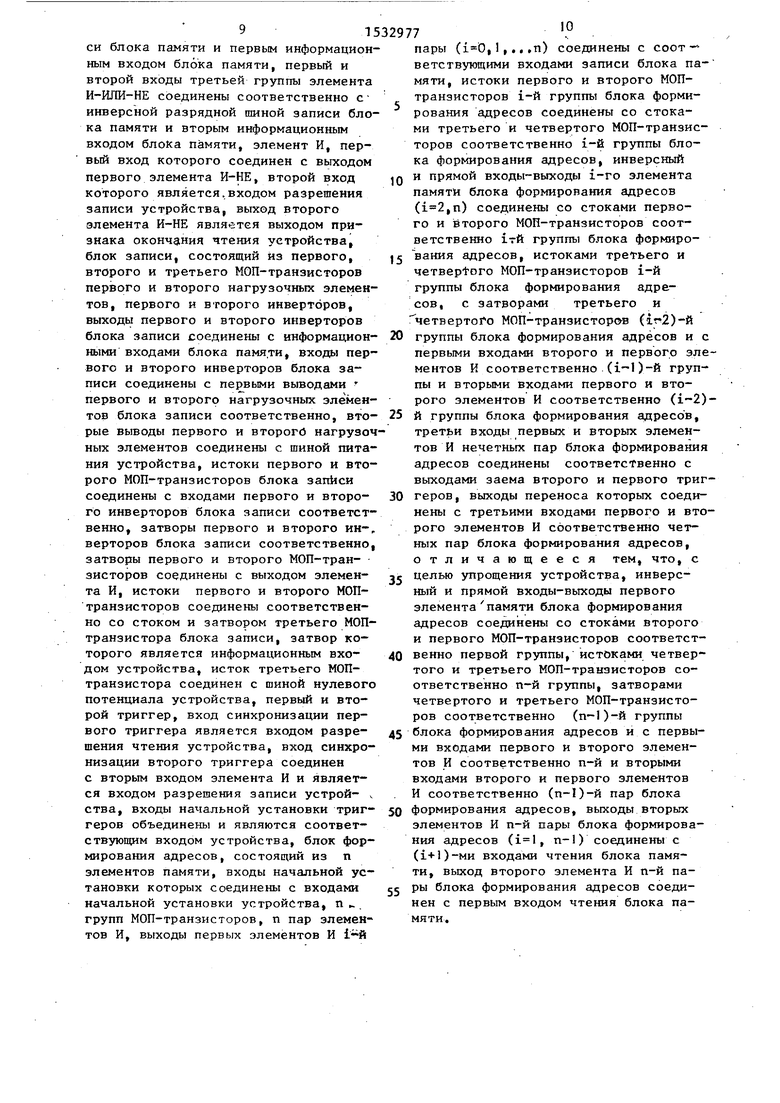

Запоминающее устройство типа очереди, содержащее блок памяти, состоящий из п элементов памяти, где п - информационная емкость устройства, первый и второй элементы И-НЕ, входы первого элемента И-НЕ соединены с прямой и инверсной разрядными шинами записи блока памяти, входы второго элемента И-НЕ соединены с прямой и. инверсной разрядными, шинами чтения блока памяти, элемент И-ИЛИ-НЕ, инвертор, выход которого является выходом признака окончания записи устройства, вход инвертора соединен с выходом элемента И-ИЛИ-НЕ, первый и второй входы первой группы которого соединены соответственно с выходами инвертора и первого элемента И-НЕ, первый и второй входы второй группы элемента И-ИЛИ-НЕ соединены соответственно с прямой разрядной шиной записи блока памяти и первым информационным входом блока памяти, первый и второй входы третьей группы элемента И-ИЛИ-НЕ соединены соответственно с инверсной разрядной шиной записи блока памяти и вторым информационным входом блока памяти, элемент И, первый вход которого соединен с выходом первого элемента И-НЕ, второй вход которого является.входом разрешения записи устройства, выход второго элемента И-НЕ является выходом признака окончания чтения устройстваt блок записи, состоящий из первого, второго и третьего МОП-транзисторов первого и второго нагрузочных элементов, первого и второго инверторов, выходы первого и второго инверторов блока записи соединены с информационными входами блока памяти, входы первого и второго инверторов блока записи соединены с первыми выводами первого и второго нагрузочных элементов блока записи соответственно, вто- 25 и группы блока формирования адресов,

рые выводы первого и второго нагрузочных элементов соединены с шиной питания устройства, истоки первого и второго МОП-транзисторов блока записи соединены с входами первого и второго инверторов блока записи соответственно, затворы первого и второго ин-„ верторов блока записи соответственно, затворы первого и второго МОП-транзисторов соединены с выходом элемента И, истоки первого и второго МОП- транзисторов соединены соответственно со стоком и затвором третьего МОП- транзистора блока записи, затвор которого является информационным входом устройства, исток третьего МОП- транзистора соединен с шиной нулевого потенциала устройства, первый и второй триггер, вход синхронизации первого триггера является входом разрешения чтения устройства, вход синхронизации второго триггера соединен с вторым входом элемента И и является входом разрешения записи устрой- . ства, входы начальной установки триггеров объединены и являются соответствующим входом устройства, блок формирования адресов, состоящий из п элементов памяти, входы начальной установки которых соединены с входами начальной установки устройства, п .. групп МОП-транзисторов, п пар элементов И, выходы первых элементов И 1-й

пары (,l,.,.n) соединены с соот - ветствующими входами записи блока памяти, истоки первого и второго МОП- транзисторов i-й группы блока формирования адресов соединены со стоками третьего и четвертого МОП-транзисторов соответственно i-й группы блока формирования адресов, инверсный и прямой входы-выходы 1-го элемента памяти блока формирования адресов (,п) соединены со стоками первого и второго МОП-транзисторов соответственно 1тй группы блока формирования адресов, истоками третьего и четвертого МОП-транзисторов 1-й группы блока формирования адресов, с затворами третьего и четвертого МОП-транзисторов (1г2)-й группы блока формирования адресов и с первыми входами второго и первого элементов К соответственно (1-1)-и группы и вторыми входами первого и второго элементов И соответственно (i-2)третьи входы первых и вторых элементов И нечетных пар блока формирования адресов соединены соответственно с выходами заема второго и первого триггеров, выходы переноса которых соединены с третьими входами первого и второго элементов И соответственно четных пар блока формирования адресов, отличающееся тем, что, с

целью упрощения устройства, инверсный и прямой входы-выходы первого элемента памяти блока формирования адресов соединены со стоками второго и первого МОП-транзисторов соответственно первой группы, истоками четвертого и третьего МОП-транзисторов соответственно п-и группы, затворами четвертого и третьего МОП-транзисторов соответственно (п-1)-й группы

блока формирования адресов и с первыми входами первого и второго элементов И соответственно n-й и вторыми входами второго и первого элементов И соответственно (п-1)-й пар блока

формирования адресов, выходы вторых элементов И n-й пары блока формирования адресов (, п-1) соединены с (1+1)-ми входами чтения блока памя

ти, выход второго элемента И n-й пары блока формирования адресов соединен с первым входом чтения блока памяти.

1532977

1

€.0

fflui,2

37

U О

6Л

1л

31

5V7

гI 45

1

Vn

П

Я

U I

Фпг. 4

| Шигин А.Г., Дерюгин А.А | |||

| Цифровые вычислительные машины (Память ЦВМ) | |||

| М.: Энергия, 1975, с | |||

| СПОСОБ ПОЛУЧЕНИЯ ТВЕРДЫХ ПРОДУКТОВ УПЛОТНЕНИЯ ФОРМАЛЬДЕГИДА С ФЕНОЛАМИ И ДРУГИМИ ВЕЩЕСТВАМИ | 1925 |

|

SU512A1 |

| Авторское свидетельство СССР по заявке 4176031/24-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-30—Публикация

1987-12-09—Подача