(Л

С

IS

Изобретение относится к вычислительной технике, может быть использовано для построения оперативных запоминающих устройств, и является усовершенствованием устройства по авт.сво № 1365129.

Целью изобретения является повышение быстродействия устройства.

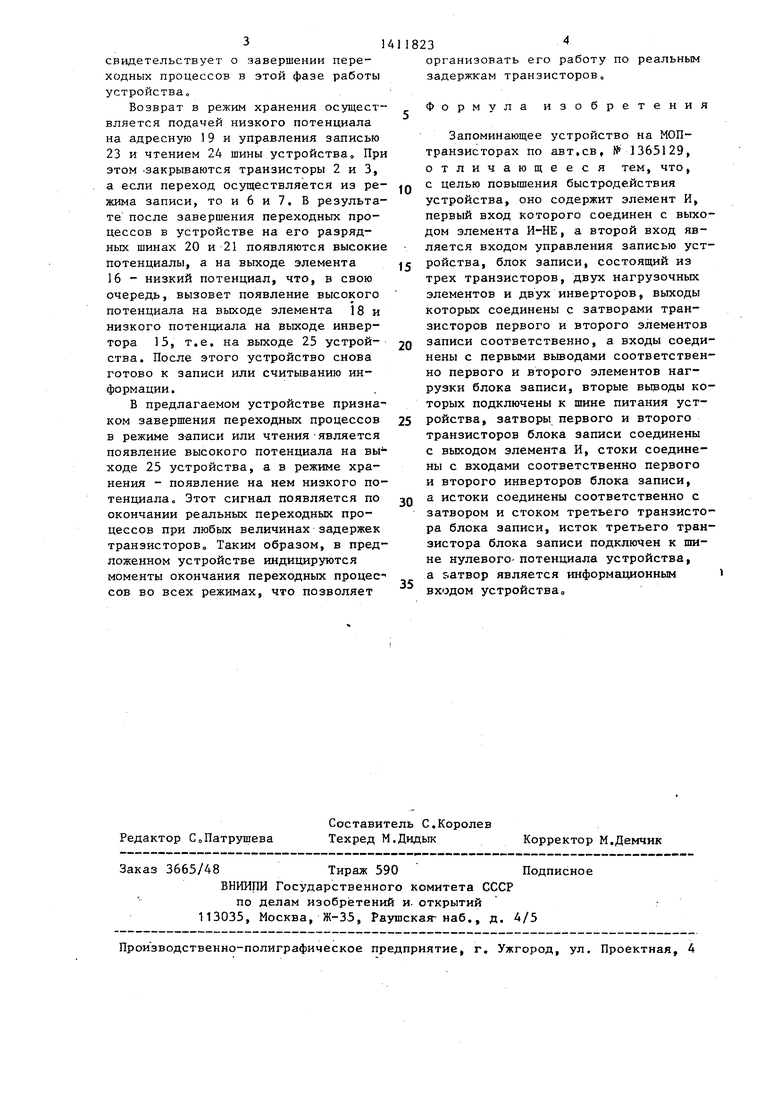

На чертеже представлена схема за- 10 поминающего устройства.

Устройство содержит элементы 1 памяти, МОП-транзисторы п-типа 2-8 и нагрузочные элементы 9 - 12, инверторы 13 - 15, элементы И-НЕ 16 и 15 И 17 и И-ИЛИ-НЕ 18, адресные шины 19, ра зрядные шины 20 и 21 , информационный вход 22 устройства, вход 23 управления записью устройства, вход 24 управления чтением устройства, выход 20

25 индикации окончания переходных процессов устройства. Запоминающее устройство работает следующим образом,

Б режиме хранения на адресные ши- ны 19 всех элементов 1 и на входы 23 и 24 управления записью и чтением подаются низкие потенциалы. В результате закрыты транзисторы 2 и 3, на выходе элемента 17 также имеется низ- 30 кий потенциал, который закрывает

транзисторы б и 7 и на входе инвер- торов 13 и 14 будут высокие потенциа-. лы, а на их выходе - низкие потенциалы, которые закрывают 35 .транзисторы 4 и 5, т.е. на разрядных шинах 20 и 21 уст- ройства имеются высокие потенциалы, на выходе элемента 16 - низкий потенциал, на выходе элемента 18 - 40 высокий потенциал, а на выходе 25 устройства (выходе инвертора 15) - низкий потенциал.

Б режиме чтения информации из элемента 1 на соответствующую адресную дд шину 19 подается высокий потенциал, который открьшает транзисторы 2 и 3, связанные с этим элементом 1 и низкий потенциал с ее нулевого или единичного выхода (в зависимости от тояния ячейки 1) поступает через один из них на одну из разрядных шин 20 и 2 устройства, в результате чего на выходе элемента 16 появляется высокий потенциаЛо Одновременно с этим ее высокий потенциал подается на вход 24 jTipaBЛенин чтением устройства и на выходе элемента 18 появляется низкий потенциал, который вызьшает появление высокого поте-нциала на выходе инвертора 15, т.е. на выходе 25 устройства, что свидетельствует о завершении переходных процессов в этой фазе работы устройства.

В режиме записи информации в элемент 1 на соответствующую адресную шину 19 подается высокий потенциал, который открьшает транзисторы 2 и 3, связанные с этим элементом 1, и низкий потенциал с ее нулевого или единичного выхода (в зависимости от состояния элемента 1) поступает через один из них на одну из разрядных шин 20 и 21 устройства, в результате чего на выходе элемента 16 появляется высокий потенциал. Одновременно с этим высокий потенциал подается на вход 23 управления записью устройства и на выходе элемента I7 появляется высокий потенциал, которы открывает транзисторы 6 и 7, через которые на вход инвертора 13 поступает сигнал с информационного входа 22 устройства, а на вход инвертора 14 - его инверсия.

Если информации, поступающая на вход 22 устройства, совпадает с ранее записанной в элемент 1, то изменения состояния последней не происходит и после того, как сработает- один из инверторов 13 или 14 и на его выходе появится высокий потенциал, на выходе элемента 18 появится низкий потенциал, который вызовет появление высокого потенциала на выходе инвертора 15, т.е. на выходе 25 устройства, что свидетельствует о завершении переходных процессов в этой фазе работы устройства

Если же информация, поступающая на вход 22 устройства, противоположна ранее записанной в элемент 1, то после того, как сработает один из инверторов 13 или 14 и на его выходе появится высокий потенциал, произойдет переключение элемента 1, При этом появление низкого потенщ ала на выходе элемента 18 произойдет только после того, как завершится это переключение, потому, что в его процессе на обоих разрядных шинах 20 и 21 будут низкие потенциалы. Появление низкого потенциала на выходе элемента 18, как и в предьщущих случаях, вызовет появление высокого потенциала на выходе инвертора 15, т.е, на выходе 25 устройства, что

3

свидетельствует о завершении переходных процессов в этой фазе работы устройства

Возврат в режим хранения осуществляется подачей низкого потенциала на адресную 19 и управления записью 23 и чтением 24 шины устройства. При этом Закрываются транзисторы 2 и 3, а если переход осуществляется из режима записи, то и 6 и 7. В результате после завершения переходных процессов Б устройстве на его разрядных шинах 20 и 21 появляются высокие потенциалы, а на выходе элемента 16 - низкий потенциал, что, в свою очередь, вызовет появление высокого потенциала на выходе элемента 18 и низкого потенциала на выходе инвертора 15, т.е. на выходе 25 устройства. После этого устройство снова готово к записи или считьшанию информации.

Б предлагаемом устройстве признаком завершения переходных процессов в режиме з-аписи или чтения-является появление высокого потенциала на выходе 25 устройства, а в режиме хранения - появление на нем низкого потенциала , Этот сигнал появляется по окончании реальных переходных процессов при любых величинах задержек транзисторов. Таким образом, в предложенном устройстве индицируются моменты окончания переходных процес сов во всех режимах, что позволяет

11823

организовать его работу по реальным задержкам транзисторов.

Формула изобретения

o

5

Запоминающее устройство на МОП- транзисторах по авт.ев, № 1365129, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элемент И, первый вход которого соединен с выходом элемента И-НЕ, а второй вход является входом управления записью устройства, блок записи, состоящий из трех транзисторов, двух нагрузочных элементов и двух инверторов, выходы которьк соединены с затворами транзисторов первого и второго элементов записи соответственно, а входы соединены с первыми вьюодами соответственно первого и второго элементов нагрузки блока записи, вторые выводы которых подключены к шине питания устройства, затворы первого и второго транзисторов блока записи соединены с выходом элемента И, стоки соединены с входами соответственно первого и второго инверторов блока записи, а истоки соединены соответственно с затвором и стоком третьего транзистора блока записи, исток третьего транзистора блока записи подключен к шине нулевого- потенциала устройства, а г-атвор является информационным входом устройствао

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1365129A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оператив- ньк запоминающих устройств, Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит элемент И 17 и блок записи, состоящий из трех транзисторов 6-8, двух элементов нагрузки 11,12, двух инверторов 13,14 с соответствующими связями. Элемент И 17 вырабатьшает в блок записи сигнал разрешения записи сразу после окончания переходных процессов на разрядных шинах 20 21 устройства. 1 ил.

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1365129A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-23—Публикация

1986-11-17—Подача