Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения высокопроизводительных многопроцессорных вычислительных систем.

Известно устройство сопряжения двух ЭВМ, содержащее соответствующим образом соединенные центральный процессор, оперативное запоминающее устройство, арифметико-логический блок, блок обмена, блок коммутации, блок формирования микрокоманд, регистр приема-передачи, триггеры готовности приема и информации и элемент И.

Недостатками устройства являются низкая производительность обмена информацией и большие аппаратные затраты на

реализацию обмена информацией в устройстве.

Известна также система доступа к памяти, содержащая соответствующим образом соединенные между собой блоки центральных процессоров, блоки обработки запросов, запоминающие устройства, блоки и.ндивидуального управления, регистра адреса, буферные регистры данных, мультиплексоры данных и мультиплексоры записываемых данных.

Недостатком устройства является сложность его реализации и большие аппаратные затраты для организации обмена данными между процессорами и за поминающими устройствами. Кроме того, принятая в системе синхронизация обращения i-x процессоров к J-M запоминающим устройствам

посредством блоков обработки запросов приводит к снижению быстродействия как отдельных процессоров, так и системы в целом.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому устройству является устройство для сопряжения двух процессоров через общую память, содержащее соединенные между собой и с входами, выходами и входами-выходами устройства блок оперативной памяти, мультиплексор адреса, регистр, блок синхронизации, триггер обращения к памяти, элемент И, двунаправленный шинный формирователь и видеоконтроллер (процессор ввода-вывода).

К недостаткам устройства следует отнести низкую производительность, обмена и большие аппаратные затраты на реализацию оборудования для обмена информацией между процессорами.

Низкая производительность устройства обусловлена двойными затратами времени на обмен данными через посредство общей для двух процессоров памяти. При этом обмен заключается в записи информации в общую память из одного и считывание этой информации из общей памяти в другой процессор. При этом быстродействие процессоров должно быть вдвое меньше быстродействия общей для них памяти, что дополнительно снижает производительность устройства.

Большие аппаратные затраты на реализацию устройства вызваны обязательностью для его работоспособности блока общей оперативной памяти и блока синхронизации для этой общей памяти, а также необходимостью регистра для временного хранения информации. Кроме того, принятия в устройстве организация обмена кроме удвоения времени обмена требует удвоения оборудования для формирования микроопераций взаимодействия процессоров с общей памятью, т. е. эти микрооперации должны формироваться в каждом из двух процессоров.

Цель изобретения - сокращение аппаратных затрат и повышение производительности обмена данными между процессорами.

Поставленная цель достигается тем, что в устройство для сопряжения двух процессоров, содержащее блок оперативной памяти, двунаправленный шинный формирователь, включающий первую и вторую группы информационных шинных формирователей, триггер обращения к памяти, первую и вторую группы адресных шинных

формирователей, первый элемент И, причем группы входов адресных магистралей от центрального процессора и от процессора ввода-вывода соединены с группами информационных входов соответственно первой и второй групп адресных шинных формирователей, группы выходов которых соединены между собой и с группой адресных входов блока оперативной памяти, группа информационных входов-выходов блока оперативной памяти соединена с первой группой входов-выходов двунаправленного шинного формирователя, подключенной к группе информационных входов первой и к группе

5 выходов второй групп информационных шинных формирователей, группа входоввыходов магистрали данных от центрального процессора соединена с второй группой входов-выходов двунаправленного шинного формирователя, подключенной к группе выходов первой и к группе информационных входов второй групп информационных шинных формирователей, вход обращения от центрального процессора соединен с

5 первым установочным входом триггера обращения к памяти, первый, третий и второй синхровходы группы синхровходов устройства соединены соответственно с вторым установочным входом и входом сброса триггера обращения к памяти и с первым входом первого элемента И, дополнительно введены триггер синхронизации, второй элемент И, шинные формирователи обращения и записи процессора ввода-вывода и обращения и записи центрального процессора, первый - третий элементы И-НЕ, элемент ИЛИ, элемент НЕ и первый и второй регистры, причем входы обращения и записи от процессора ввода-вывода соединены с информационными входами шинных формирователей обращения и записи процессора ввода-вывода, вход блокировки процессора ввода-вывода соединен с управляющими входами второй группы адресных шинных

5 формирователей и шинных формирователей обращения и записи процессора ввода-вывода, группа информационных входов-выходов блока оперативной памяти соединения с группой входов-выходов магистрали данных процессора ввода-вывода, вход обращения от центрального процессора соединен с вторым входом первого элемента И и первым входом третьего элемента И-НЕ, выход которого подключен к управляющим входам первой группы адресных шинных формирователей и шинных формирователей обращения и записи центрального процессора, вход записи от центрального процессора соединен с входом элемента НЕ, третьим входом первого элемента И,

информационным входом шинного формирователя записи центрального процессора и с первым входом первого элемента И-НЕ, выход которого через первый управляющий вход двунаправленного шинного формирователя соединен с управляющим входом второй группы информационных шинных формирователей, выход элемента НЕ соединен с третьим установочным входом триггера обращения к памяти и с первым входом второго элемента И-НЕ, выход которого через второй управляющий вход двунаправленного шинного формирователя соединен с управляющим входом первой группы информационных шинных формирователей, выходы триггера обращения к памяти и первого элемента И соединены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И-НЕ и информационным входом шинного формирователя обращения центрального процессора, выходы шинных формирователей обращения процессора ввода-вывода и центрального процессора и первый вход первого резистора соединены между собой и с входом обращения блока оперативной памяти, выходы шинных формирователей записи процессора ввода-вывода и центрального процессора и первый вход второго резистора соединены между собой и с входом записи блока оперативной памяти, вторые входы первого и второго резисторов подключены к шине питания, вход запроса от центрального процессора является выходом запроса для процессора ввода-вывода и соединен с первым входом второго элемента И, вторым входом первого элемента И-НЕ, третьим входом второго элемента И-НЕ и вторым входом третьего элемента И-НЕ, вход разрешения обмена от процессора ввода-вывода соединен с информационным входом триггера синхронизации, синхровход которого соединен с вторым синхровходом группы синхровходов устройства, выход триггера синхронизации соединен с третьим входом третьего элемента И-НЕ и вторым входом второго элемента И, выход которого соединен с выходом разрешения обмена устройства для центрального процессора.

Сущность изобретения состоит в сокращении времени обмена информацией между процессорами, поскольку из устройства исключен блок оперативной памяти межпроцессорного обмена, т. е. процедура обмена заключается в непосредственной передаче данных между центральным процессором и процессором ввода-вывода (оперативной памятью процессора вводавывода), что позволяет исключить передачу

путем заполнения двух процедур - загрузки и выгрузки памяти межпроцессорного обмена, как это делается в устройстве-прототипе. Кроме того, устройство для своей

работы не требует двукратного уменьшения быстродействия процессоров по отношению к быстродействию памяти межпроцессорного обмена, которая исключена в предлагаемом устройстве. Кроме того, сущность изобретения состоит в сокращении аппаратных затрат, заключающихся в исключении упомянутого блока,оперативной памяти межпроцессорного обмена, исключения информационного регистра и, кроме

того, упрощении процессора ввода-вывода по связи с предлагаемым устройством. Все это позволяет упростить само устройство и повысить его производительность.

Сущность изобретения реализуется

введением в устройство соответствующим образом соединенных между собой триггера синхронизации, второго элемента И, трех элементов И-НЕ, элементов ИЛИ и НЕ, шинных формирователей обращения и записи

процессора ввода-вывода и центрального процессора и подключения попарно их выходов к шине питания через резисторы.

Положительный эффект достигается при осуществлении изобретения, так как обмен информацией без буферизации вдвое сокращает время на перемещение-информации из одного процессора в другой. Двукратное увеличение производительности обмена обеспечивается даже без учета снятия в предлагаемом устройстве требования двукратного снижения быстродействия процессоров по отношению к быстродействию используемого в прототипе блока оперативной памяти межпроцессорного обмена. С

учетом данного требования в предлагаемом устройстве производительность увеличивается более чем в два раза.

Кроме того, положительный эффект при реализации изобретения достигается за

счет исключения блока оперативной памяти межпроцессорного обмена (оперативная память процессора ввода-вывода, расположенная в соответствующем блоке прототипа - видеоконтроллере, т. е. процессора

ввода-вывода, а не блок оперативной памяти межпроцессорного обмена) и информационного регистра, оборудование которых во много раз больше вновь введенных элементов - триггера, элементов И,И-НЕ,ИЛИ,,

НЕ и шинных формирователей сигналов обращения и записи с резисторами.

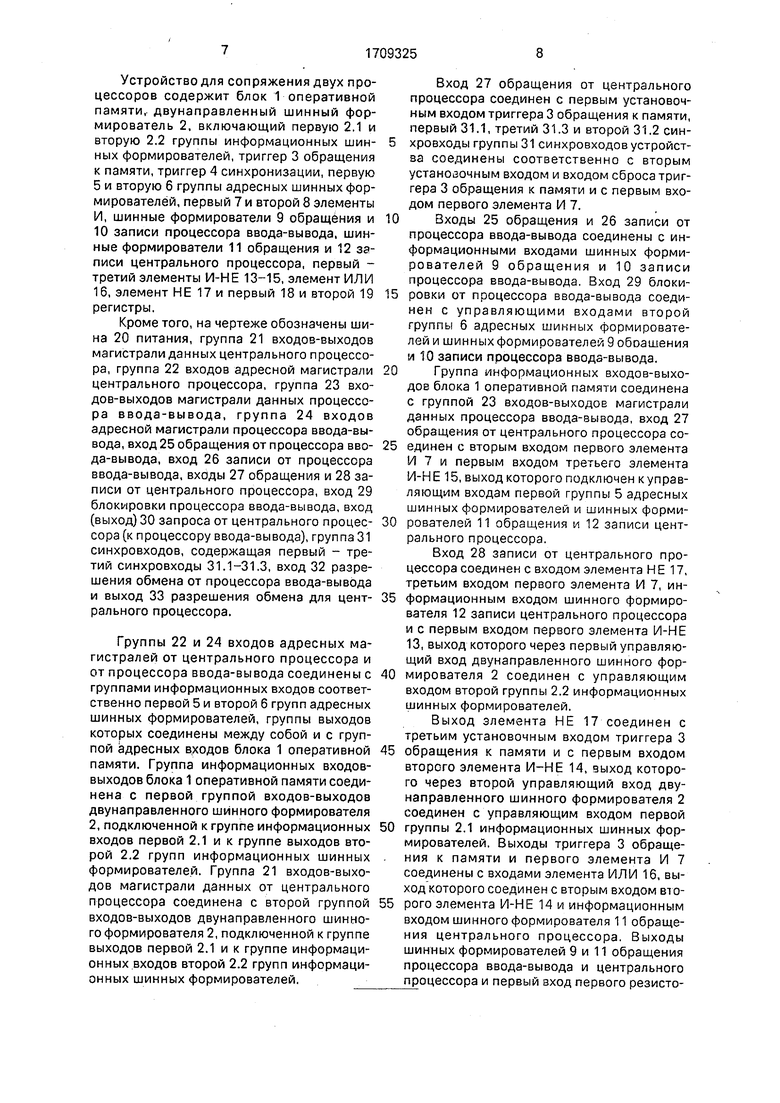

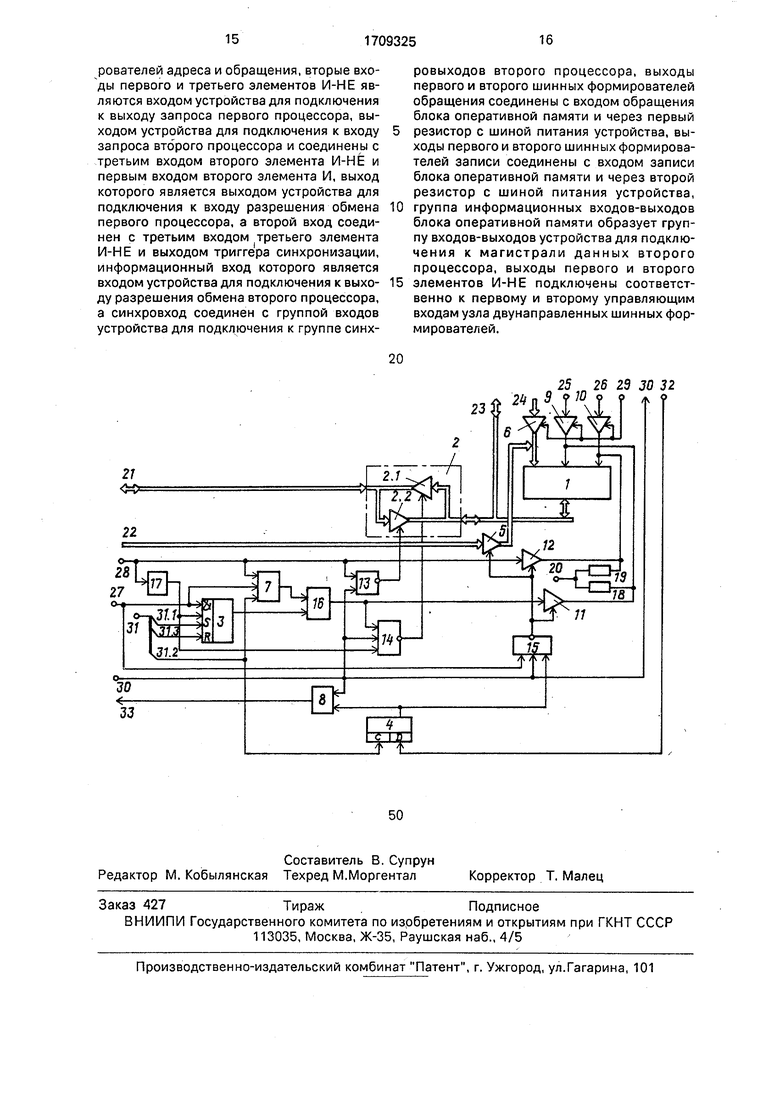

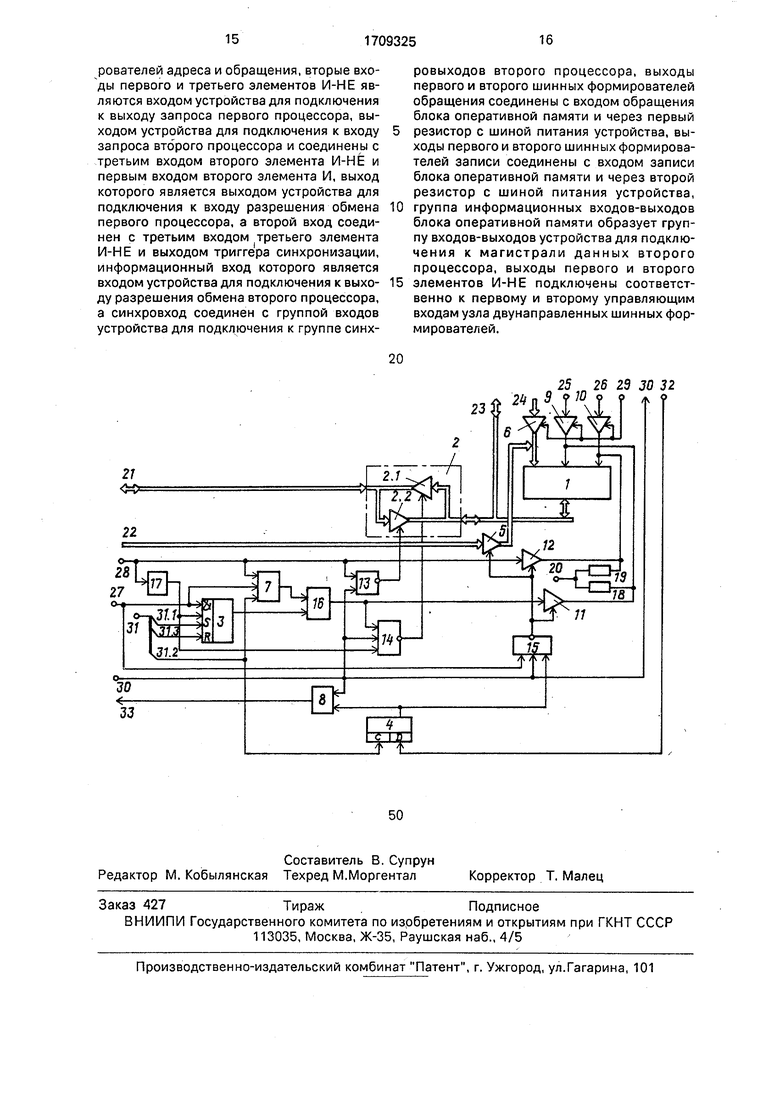

На чертеже изображена функциональная схема устройства для сопряжения двух процессоров.

Устройство для сопряжения двух процессоров содержит блок 1 оперативной памяти, двунаправленный шинный формирователь 2, включающий первую 2.1 и вторую 2.2 группы информационных шинных формирователей, триггер 3 обращения к памяти, триггер 4 синхронизации, первую 5 и вторую 6 группы адресных шинных формирователей, первый 7 и второй 8 элементы И, шинные формирователи 9 обращения и 10 записи процессора ввода-вывода, шинные формирователи 11 обращения и 12 записи центрального процессора, первый третий элементы И-НЕ 13-15, элемент ИЛИ 16, элемент НЕ 17 и первый 18 и второй 19 регистры.

Кроме того, на чертеже обозначены шина 20 питания, группа 21 входов-выходов магистрали данных центрального процессора, группа 22 входов адресной магистрали центрального процессора, группа 23 входов-выходов магистрали данных процессора ввода-вывода, группа 24 входов адресной магистрали процессора ввода-вывода, вход 25 обращения от процессора ввода-вывода, вход 26 записи от процессора ввода-вывода, входы 27 обращения и 28 записи от центрального процессора, вход 29 блокировки процессора ввода-вывода, вход (выход) 30 запроса от центрального процессора (к процессору ввода-вывода), группа 31 синхровходов, содержащая первый - третий синхровходы 31.1-31.3, вход 32 разрешения обмена от процессора ввода-вывода и выход 33 разрешения обмена для центрального процессора.

Группы 22 и 24 входов адресных магистралей от центрального процессора и от процессора ввода-вывода соединены с группами информационных входов соответственно первой 5 и второй 6 групп адресных шинных формирователей, группы выходов которых соединены между собой и с группой адресных в.ходов блока 1 оперативной памяти. Группа информационных входоввыходов блока 1 оперативной памяти соединена с первой группой входов-выходов двунаправленного шинного формирователя 2, подключенной к группе информационных входов первой 2.1 и к группе выходов второй 2.2 групп информационных шинных формирователей. Группа 21 входов-выходов магистрали данных от центрального процессора соединена с второй группой входов-выходов двунаправленного шинного формирователя 2, подключенной к группе выходов первой 2.1 и к группе информационных входов второй 2.2 групп информационных шинных формирователей.

Вход 27 обращения от центрального процессора соединен с первым установочным входом триггера 3 обращения к памяти, первый 31.1, третий 31.3 и второй 31.2 синхровходы группы 31 синхровходов устройства соединены соответственно с вторым установочным входом и входом сброса триггера 3 обращения к памяти и с первым входом первого элемента И 7.

0 Входы 25 обращения и 26 записи от процессора ввода-вывода соединены с информационными входами шинных формирователей 9 обращения и 10 записи процессора ввода-вывода. Вход 29 блокировки от процессора ввода-вывода соединен с управляющими входами второй группы б адресных шинных формирователей и шинных формирователей 9 обоашения и 10 записи процессора ввода-вывода.

0Группа информационных входов-выходов блока 1 оперативной памяти соединена с группой 23 входов-выходов магистрали данных процессора ввода-вывода, вход 27 обращения от центрального процессора соединен с вторым входом первого элемента И 7 и первым входом третьего элемента И-НЕ 15, выход которого подключен куправляющим входам первой группы 5 адресных шинных формирователей и шинных формирователей 11 обращения и 12 записи центрального процессора.

Вход 28 записи от центрального процессора соединен с входом элемента НЕ 17, третьим входом первого элемента И 7, информационным входом шинного формирователя 12 записи центрального процессора и с первым входом первого элемента И-НЕ 13, выход которого через первый управляющий вход двунаправленного шинного формирователя 2 соединен с управляющим входом второй группы 2.2 информационных шинных формирователей.

Выход элемента НЕ 17 соединен с третьим установочным входом триггера 3

5 обращения к памяти и с первым входом второго элемента И-НЕ 14, выход которого через второй управляющий вход двунаправленного шинного формирователя 2 соединен с управляющим входом первой

0 группы 2.1 информационных шинных формирователей. Выходы триггера 3 обращения к памяти и первого элемента И 7 соединены с входами элемента ИЛИ 16, выход которого соединен с вторым входом вю5 рого элемента И-НЕ 14 и информационным входом шинного формирователя 11 обращения центрального процессора. Выходы шинных формирователей 9 и 11 обращения процессора ввода-вывода и центрального процессора и первый вход первого резистоpa 18 соединены между собой и с входами обращения блока 1 оперативной памяти. Выходы шинных формирователей 10 и 12 записи процессора ввода-вывода и центрального процессора и первый вход второго резистора 19 соединены между собой и с входом записи блока 1 оперативной памяти. Вторые входы первого 18 и второго 19 резисторов подключены к шине 20 питания.

Вход 30 запроса от центрального процессора является выходом 30 запроса для процессора ввода-вывода и соединен с первым входом второго элемента И 8, вторым входом первого элемента И-НЕ 13. третьим входом второго элемента И-НЕ 14 и вторым входом третьего элемента И-НЕ 15. Вход 32 разрешения обмена от процессора ввода-вывода соединен с информационным входом D-триггера 4 синхронизации, синхровход С которого соединен с вторым синхровходом 31.2 группы 31 синхровходов устройства. Выход триггера 4 синхронизации соединен с третьим входом третьего элемента И-НЕ 15 и вторым входом второго элемента И 8, выход которого соединен с выходом 33 разрешения обмена устройства для центрального процессора.

Назначение элементов и узлов устройства следующее.

Блок 1 оперативной памяти является памятью процессора ввода-вывода и в те моменты времени, когда не производится обмен информацией между центральным процессором и процессором ввода-вывода, последний осуществляет работу с этим блоком оперативной памяти, взаимодействуя с ним по сигналам обращения и записи на входах 25 и 26 устройства, адресам на группе 24 входов устройства и информации, передаваемой в блок оперативной памяти или считываемой с него через шину 23 входоввыходов.

Двунаправленный шинный формирователь 2 предназначен для передачи информации от центрального процессора через вторую группу 2.2 информационных шинных формирователей на входы-выходы блока 1 оперативной памяти, если поступает разрешающий сигнал низкого уровня с выхода первого элемента И-НЕ 13, или из блока 1 оперативной памяти в центральный процессор через первую группу 2.1 информационных шинных формирователей, если поступает разрешающий сигнал низкого уровня с выхода второго элемента И-НЕ 14. Поскольку элемент НЕ 17 делает невозможным одновременную выработку низкого уровня сигналов на выходах первого 13 и второго 14 элементов И-НЕ, то двунаправленный шинный формирователь в один и тот

же момент времени допускает передачу информации только в одном направлении. При отсутствии сигналов низкого уровня на выходах элементов И-НЕ 13 или 14 выходы

двунаправленного шинного формирователя 2 находятся в высокоимпедансном (третьем) состоянии.

Триггер 3 обращения к памяти предназначен для формирования сигнала обращения к блоку 1 оперативной памяти в режиме считывания информации для передачи ее в центральный процессор. Данному режиму считывания соответствует отсутствие сигнала на входе 28 записи и наличие сигнала

5 на входе 27 обращения. Включение и выключение триггера 3 производится по синхросигналам на первом 31.1 и третьем 31.3 синхровходах устройства, причем включение производится условно по приведенным

0 сигналам, а выключение безусловно.

Первый элемент И 7 предназначен для формирования сигнала обращения к блоку 1 оперативной памяти в режиме записи в него информации от центрального процессора.

5 когда на входах 27 обращения и 28 записи присутствуют сигналы. Момент формирования сигнала обращения в этом случае определяется моментом подачи синхросигнала на синхровход 31.2 устройства.

0 Сигналы с выходов триггера 3 и первого элемента И 7 объединяются элементом ИЛИ 16 для подачи его через шинный формирователь 11 на вход обращения блока 1 памяти.

5 Такая организация сигнала обращения для блока 1 памяти в режимах считывания и записи информации позволяет реализовать блок 1 оперативной памяти на различной элементной базе (например, биполярные

0 статические асинхронные или статические синхронные, изготовленные, например, по КМОП-технологии БИС ОЗУ) с различной временной диаграммой их работы, так как статические асинхронные ОЗУ допускают

5 работу по временной диаграмме статических синхронных ОЗУ, но не наоборот.

Для доступа к блоку 1 оперативной памяти процессора ввода-вывода от центрального процессора последний формирует

0 сигнал запроса на одноименном входе 30. В ответ на этот сигнал процессор ввода-вывода прерывает свою работу с блоком 1 памяти и разрешает центральному процессору работу с ним. При этом процессор ввода-вы5 вода формирует сигнал на входе 29 устройства, блокирующий (переводит в третье состояние) выходы шинных формирователей 6, 9 и 10, и формирует для центрального процессора сигнал разрешения на входе 32 устройства.

Поскольку работа двух процессоров протекает независимо и, как следствие, асинхронно, то триггер 4 синхронизации осуществляет привязку данного сигнала разрешения к тактовой сетке центрального процессора.

Второй элемент И 8 предназначен для передачи сигнала разрешения с выхода триггера 4 на выход 33 устройства для центрального процессора. Применение второго элемента И 8, управляемого сигналом запроса от центрального процессора, позволяет не сокращать функциональных возможностей процессора ввода-вывода, поскольку при организации связей процессора ввода-вывода более чем с одним центральным процессором его сигнал разрешения будет поступать только в запросивный процессор.

Первая (вторая) группа 5 (6) адресных шинных формирователей предназначена для передачи на группу адресных входов блока 1 оперативной памяти кодов адресов с группы 22 (24) входов адресной магистрали центрального процессора (процессора ввода-вывода) при выработке низкого уровня сигнала на выходе третьего элемента ИНЕ 15 (на входе 29 устройства).

Шинные формирователи 9(11) обращения и 10(12)записи процессора ввода-вывода (центрального процессора) предназначены для передачи на входы обращения и записи блока 1 оперативной памяти одноименных сигналов от процессора ввода-вывода (центрального процессора) по входам 25 (27) и 26 (28) устройства при формировании сигнала низкого уровня на входе 29 устройства (выходе третьего элемента ИНЕ 15).

Для построения шинных формирователей 2.1 и 2.2,5и 6(9 и 10,11 и 12) могут быть использованы например, стандартные микросхемы 571ХЛ5(4).

Подключение одного вывода регистра 18 (19) к выходам попарносоединенных между собой шинных формирователей 9 и 11 (10 и 12), а другим - к шине 20 питания увеличивает помехозащищенность и соответственно надёжность устройства в моменты времени одновременного нахождения этих элементов в высокоимпедансном состоянии (в эти моменты времени соответствующие входы блока 1 оперативной памяти обладают минимальной помехозащищенностью).

Первый 13 (второй 14) элемент И-НЕ предназначен для управления передачей информации от центрального процессора (блока 1 оперативной памяти) к блоку 1 оперативной памяти (центральному процессору) через вторую (первую) группу 2,2 (2.1) информационных шинных формирователей двунаправленного шинного формирователя 2 в режиме записи (считывания) информации из центрального процессора (блока 1 памяти) в блок оперативной памяти (центральный процессор).

Третий элемент И-НЕ 15 предназначен для перевода шинных формирователей 5, 11

0 и 12 из третьего состояния в активное при обмене информацией между центральным процессором и блоком 1 оперативной памяти.

Элемент НЕ 17 предназначен для бло5 кировки включения триггера 3 обращения и

срабатывания второго элемента И-НЕ 14 в

режимах записи информации центрального

процессора в блок 1 оперативной памяти.

Устройство работает следующим обра0 зом.

Устройство используется в двух состояниях работоспособности. Состоянию независимой работы процессоров соответствует отсутствие сигналов на входах 27, 28, 30 и

5 32 устройства, при котором шинные формирователи 2.1, 2.2, 5, 11 и 12 закрыты (выходы установлены в третье высокоимпендансное состояние). В этом случае блок 1 оперативной памяти, являющийся запоминающим

0 устройством процессора ввода-вывода, работает под управлением его сигналов.

Сигналы обращения и записи поступают в блок 1 памяти от процессора ввода-вывода через входы 25 и 26 устройства и

5 шинные формирователи 9 и 10. Коды адресов поступают на группу адресных входов блока 1 памяти через группу 6 шинных формирователей, а данные между процессором ввода-вывода и его блоком 1 оперативной

0 памяти передаются через группу 23 входоввыходов магистрали данных процессора ввода-вывода.

В состояние обмена информацией между центральным процессором и блоком 1

5 оперативной памяти процессора ввода-вывода (и функционирование в этом состоянии) устройство переходит следующим образом.

На вход 30 устройства поступает сигнал

0 от центрального процессора, запрашивающий разрешения процессора ввода вывода на обмен. По готовности последнего к обмену (либо при работе последнего без обращения к блоку 1 оперативной памяти) он

5 формирует сигнал на входе 32 устройства. Данный сигнал синхронизируется с работой центрального процессора с помощью триггера 4 и передается в центральный процессор через элемент И 8 в качестве сигнала, разрешающего обмен.

Далее работа устройства может проходить в двух режимах.

При считывании информации из блока 1 памяти в центральный процессор сигнал вырабатывается на входе 27 и не вырабатывается на входе 28 устройства. При этой комбинации сигналов триггер 3 обращения формирует сигнал обращения к памяти, поступающий на вход обращения блока 1 памяти через злемент ИЛИ 16 и шинный формирователь 11. Одновременно срабатывает второй элемент И-НЕ 14 и открывает группу 2.1 шинных формирователей, через которую информация передается с группы входов-выходов блока 1 памяти на группу 21 входов-выходов магистрали данных центрального процессора.

При записи информации в блок 1 оперативной памяти процессора ввода-вывода из центрального процессора сигналы поступают на входы 27 и 28, поэтому сигнал записи поступает в блок 1 памяти с входа 28 через шинный формирователь, а сигнал обращения, формируемый на выходе элемента И 7, поступает на соответствующий вход блока 1 памяти через элемент ИЛИ 16 и шинный формирователь 11. Адрес поступает от центрального процессора на группу адресных входов блока 1 памяти через группу 5 шинных формирователей, а информация - с группы 21 входов-выходов магистрали данных центрального процессора на группу информационных входов-выходов блока 1 памяти через группу 2.2 шинных формирователей.

Таким образом, передача информации между центральным процессором и процессором ввода-вывода передается не в два этапа, как в прототипе (запись в память межпроцессорного обмена и считывание из памяти межпроцессорного обмена), а за один сеанс обмена информация передается от центрального процессора к процессору ввода-вывода и наоборот, что вдвое сокращает время межпроцессорного обмена. При этом сокращаются аппаратные затраты на реализацию устройства (исключаются специальный блок памяти межпроцессорного обмена и регистр для временного хранения информации). Дополнительный выигрыш обеспечивается упрощением одного из двух процессоров (процессора ввода-вывода), так как в нем исключаются временные и аппаратные затраты, связанные с формированием массивов информации Для центрального процессора (связь соответствующего процессора прототипа с памятью межпроцессорного обмена).

Формула изобретения

Устройство для сопряжения двух процессоров, содержащее два узла адресных

шинных формирователей, группы информационных входов которых являются соответствующими группами входов для подключения к магистралям адреса первого

и второго процессоров, а группы выходов соединены с группой адресных входов блока оперативной памяти, группой информационных входов-выходов подключенного к первой группе информационных входов0 выходов узла двунаправленных шинных формирователей, вторая группа информационных входов-выходов которого является группой входов-выходов устройства для подключения к магистрали данных первого

5 процессора, первый элемент И и триггер обращения к памяти, первый установочный вход которого является входом устройства для подключения к выходу обращения первого процессора, второй установочный вход

0 и вход сброса триггера обращения к памяти и первый вход первого элемента И образуют группу входов устройства для подключения к группе синхровходов первого процессора, отличающееся тем, что, с целью

5 сокращения аппаратных затрат устройства, в него введены триггер синхронизации, три элемента И-НЕ, второй элемент И, элемент ИЛИ, два шинных формирователя обращения, два шинных формирователя записи,

0 элемент НЕ и два резистора, причем информационные входы первых шинных формирователей обращения и записи являются соответствующими входами устройства для подключения к выходам обращения и записи второго процессора, а управляющие входы являются входом устройства для подключения к выходу блокировки второго процессора и соединены с управляющим входом второго узла адресных шинных формирователей, информационный вход второго шинного формирователя записи является входом устройства для подключения к выходу записи первого процессора и соединен с первым входом первого элемента И-НЕ,

5 вторым входом первого элемента И и через элемент НЕ с третьим установочным входом триггера обращения к памяти к первому входу второго элемента И-НЕ, вторым входом подключенного к выходу элемента ИЛИ и

0 информационному входу второго шинного формирователя обращения, первый и второй входы элемента ИЛИ соединены соответственно с выходами триггера обращения к памяти и первого элемента ИЛИ, третий

5 вход которого соединен с входом для подключения выхода обращения первого процессора и первым входом третьего элемента И-НЕ, выходом подключенного к управляющим входам первого узла адресных шинных формирователей и вторых шинных формирователей адреса и обращения, вторые входы первого и третьего элементов И-НЕ являются входом устройства для подключения к выходу запроса первого процессора, выходом устройства для подключения к входу запроса второго процессора и соединены с третьим входом второго элемента И-НЁ и первым входом второго элемента И, выход которого является выходом устройства для подключения к входу разрешения обмена первого процессора, а второй вход соединен с третьим входом третьего элемента И-НЕ и выходом триггера синхронизации, информационный вход которого является входом устройства для подключения к выходу разрешения обмена второго процессора, а синхровход соединен с группой входов устройства для подключения к группе синхровыходов второго процессора, выходы первого и второго шинных формирователей обращения соединены с входом обращения блока оперативной памяти и через первый резистор с шиной питания устройства, выходы первого и второго шинных формирователей записи соединены с входом записи блока оперативной памяти и через второй резистор с шиной питания устройства, группа информационных входов-выходов блока оперативной памяти образует группу входов-выходов устройства для подключения к магистрали данных второго процессора, выходы первого и второго элементов И-НЕ подключены соответственно к первому и второму управляющим входам узла двунаправленных шинных формирователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1762309A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Устройство для сопряжения двух процессоров через общую память | 1990 |

|

SU1758647A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Устройство обработки информации | 1989 |

|

SU1631549A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения высокопроизводительных малогабаритных вычислительных систем. Цель изобретения - сокращение аппаратных затрат и повышение производительности обмена данными между процессорами. Цель достигается тем, что в устройство, содержащее блок оперативной памяти, узел двунаправленных шинных формирователей, триггер обращения к памяти, два узла адресных шинных формирователей и первый элемент И. введены шинные формирователи обращения и записи от второго процессора (ввода-вывода), шинные формирователи обращения и записи от первого (центрального; процессора, три элемента И-НЕ, элемент ИЛИ, элемент НЕ, два резистора, триггер синхронизации и второй элемент И. 1 ил.^^ ^^^^

25 „ 26 29 30 32 24f п 5 70 о о о

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-22—Подача