Изобретение относится к вычислительной технике и может быть использовано при создании надежных быстродействукмдих систем памяти на базе больших интегральных микросхем памяти со словарной организацией.

Известно запоминающее устройство, в котором для автоматического исправления ошибок, возникающих из-за отказов интегральных микросхем памяти (ПМП), данные кодируются помехоустойчивым кодом 1 .

Однако эти устройства требуют большого числа дополнительных разрядов элементов памяти при коррекции 4, 8 отказов в слове, а также сложных кодирующих и декодирующих схем. .

Наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее накопитель, первые входы которого соединены с выходами адресного блока, вторые входы накопителя соединены с шинами записи и входами блока кодирования, третьи входы накопителя соединены с выходами блока кодирования, первые и вторые выходы накопителя соединены с входами блока контроля и первыми входами сумматоров по модулю два, выходы блока контроля соединены с входами элемента ИЛИ и первыми входами первых элес ментов И, вторыми входами соединена ных с выходами элемента ИЛИ, выходы первых элементов И соединены с вторыми входами сумматоров по модулю два, выходами соединенных с 0 выходами устройства 23.

Такое устройство позволяет исправить одиночный блок ошибок длины 8, однако требует при обнаружении ошибки повторной записи в накопитель инвертированного слова и повторного

15 считывания информации. Это снижает быстродействие устройства. Кроме, , того, при коррекции ошибок из-за отказа НМЛ не учитывается тот факт, что отказ приводит к появлению еди20ничных сигналов на выходах .

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что запоминающее устройство с.

25 самоконтролем, содержгицее накопитель, входы первой группы которого подключейы к. выходам адресного Сло-. ка, входы второй группы накопителя подключены ко входам шифратора и

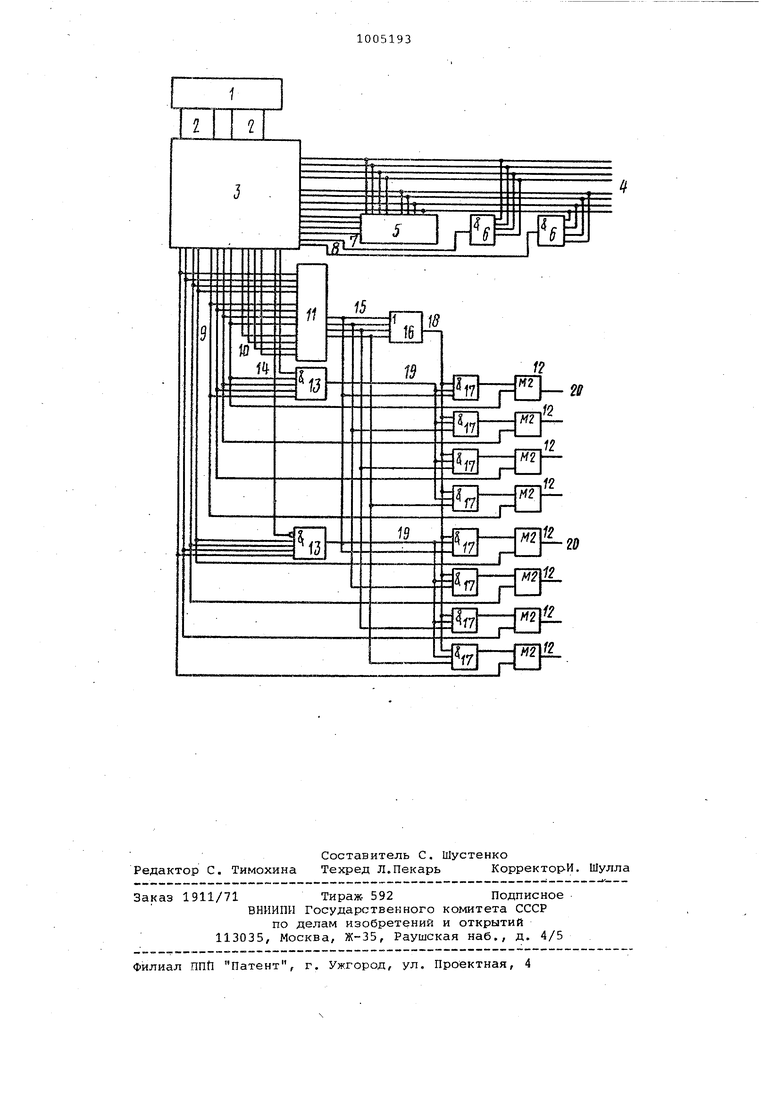

30 являются входами устройства,- выходы имфратора noflKJnoqeHfcj ко входам третьей группы накопителя, выходы первой к /второй групп которого подключены к входам блока контроля выхо,цы блока контроля подключены ко входам элемента ИЛИ и к первым входам соответствующих элементов И первой группы, выход элемента ИЛИ подключен ко вторым входам элементов И первой группы, выходы которы подключены к первым входам соответ ствующих сумматоров по модулю два, вторые входы сумматоров по модулю два подключены к соответствующим выходам первой группы накопителя, выходы сумматоров по модулю два яв ляются выходами устройства, дополнительно содержит вторую группу эл ментов И, входы которых подключены к соответствующим входам первой гр пы накопителя, выходы элементов И второй группы подключены ко входам четвертой группы накопителя, и третью группу элементов И, одни вх ды которых подключены к соответств ющим выходам первой группы накопителя, другие входы элементов И третье группы подключены к соответствующим выходам третьей группы накопителя, выходы элементов И третьей группы подключены к третьим входам соответствующих элементов И первой груп пы. На чертеже приведена структурная схема запоминающего устройства с самоконтролем. Запоминающее устройство с самоконтролем содержит адресный блок 1 первую группу входов 2 накопителя, накопитель 3, входы 4 устройства, шифратор 5, вторую группу элементов И б, третью группу входов 7 и четвертую группу входов 8 накопителя, первую группу выходов 9 и вторую группу выходов 10 накопителя, блок контроля, сумматоры 12 по модулю два, первую группу элементов И 13, третью группу выходов 14 накопителя выходы 15 блока контроля, элемент ИЛИ 16, элементы И 17 первой группы выход 18 элемента ИЛИ, выходы 19 элементов И первой группы и выходы 20 устройства. Шифратор 5 и блок 11 контроля состоит из сумматоров по модулю два. Устройство позволяет исправить одиночные в кратные отказы в каждом слове накопителя из-за отказа ИМП с единичными сигналами на выходах при наличии b -f е дополнительных разряд и высоком быстродействии устройства,где - число информационных разрядов в слове. В режиме записи информации устройство работает следующим образом. Двоичное кодовое слово длины К + Ь , ервые ( п - число микросхем амяти) разрядов которого являются нформационным, а последние Ь разядов контрольными, через входы 4, помещается в накопитель 3 по адесу , поступающему через шины 2 из дресного блока 1. В шифраторе 5 роисходит вычисление контрольных имволов путем суммирования по модую два и блоков по b разрядов в кажом. Одновременно по этому же адреу в накопитель по входам 8 заноситя для хранения информация с выходов лементов И 6. Эта информация указыает подлежит ли хранению в какойибо микросхеме памяти данного слова диничный блок информации. Пример ; Пусть 1с 16, b 4, п 16, е п 4, т.е. -4-4, при построении накопителя с длиной слова в 1,6 ;разрядов используется четыре ИМП с четырьмя шинами записи-считывания каждая и пусть в накопитель записывается информация 1000 1100 0010 1111. Тогда в контрольные разряды записывается информация 1001, так как 1000 1100 0010 1111 1001 по модулю два, ав контрольные разряды записывается информация 0001, так как только в четвертом блоке записи подлежит единичное слово. Таким образом, в накопитель заносится слово 1000 1100 0010 1111 1001 0001. В режиме считывания информации выходные данные по шинам 9, 10, 14 подаются на блок 11 контроля и одновременно на элементы И 13. Блоком 11 вырабатывается признак (синдром), который равен нулю, если ошибок нет в (Js + b) разрядах, и не равен нулю в противном случае. Если в считываемом слове ошибок нет, то на выходе 18 элемента ИЛИ 16 будет нулевой сигнал, который установит на выходг1х элементов И 17 нулевые сигналы. Тем самым на выходы 20 устройства поступят сигналы с 1с информационных разрядов с выходов 9 накопителя через сумГ аторы 12 без изменения. Если в считываемом слове в (k-t+ Ъ } разрядах имеются ошибки в b разрядах из-за отказа, любой одной ИМП, что приводит к появлению на выходах отказавший НМЛ единичных с налов, то на выходах 15 блока 11 б дет ненулевой сигнал, а на выходе 18элемента ИЛИ 16 - единичный сиг нал. Кроме того, единичный сигнал появится на одном из выходов 19 элемента И 13, поскольку на выхода 9 у отказавшей НМЛ накопителя 3 будут единичные сигналы, а на инвертирующем входе элемента И 13 нулевой сигнал. Единичный сигнал с выхода 19 элемента И 13 откроет со ответствующие элементы И 17, относящиеся к отказавшим разрядам. Эти же элементы И 17 будут открыты по другому входу единичным сигналом с выхода 18 элемента ИЛИ 16, на выхо дах соответствующих элементов И 17 появятся сигналы, отображающие ненулевой синдром. При сложении на с маторах 12 по модулю два этого син рома с информацией, относящейся к этому блоку {единичной информацией ), происходит коррекция считываемой информации из искаженного блока (отказавшей ИИП ). Если же искаженными являются b контрольные разряды, то на выходах 19элементов И 13 будут нулевые сиг налы, так как все информационные разряды исправны (корректируется только один дефектный блок разрядо и следовательно, элементы И 17 буд закрыты. Информация, считываемая с информационных разрядов накопителя поступит через сумматоры 12 на вых ды 20 устройства без изменения. Если же искаженными являются 2 контрольные разряды, то на выходе блока 11 будет нулевой синдрс. Тог да на выходе 18 элемента ИЛИ 16 появится нулевой сигнал, который закроет элементы И 17. Тем самым информация, считываемая с информационных разрядов накопителя поступит- через сумматоры 12 на выходы 20 устройства без изменения. П р и м е р 2 . Пусть для вышеприведенного примера информация искажена в первом блоке из-за отказа ИМП, т.е. с выходом 9, 10, 14 накопителя 3 считывается число 1111 1100 0010 1111 1001 0001. Тогда на выходе 15 блока 11 будет 0111, так как 1111 1 1100 2 00103 1111 4 1001 5 0111 Кроме того, поскольку первый блок содержит единичные символы, а первый из Е контрольных символов нулевой,.то на одном из выходов эле ментов И 13 будет единичный сигнал котррый откроет соответствующие элементы И 17. Тем самым на выходе этих элементов выделится синдром. Тогда на сумматорах 12 произойдет суммирование синдрома и информации из искаженного блока, т-.е. ОЩ + 1 1000, что соответствует исходной подлежащей .хранению информации в этом блоке. .. Таким образом, в предлагаемом устройстве отсутствует необходимость проведения записи инвертированного слова и контрольного считывания при обнаружении отказов, что позволяет повысить быстродействие устройства. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, зходы первой группы которого подключены к выходам адресного блока, входы второй группы накопителя подключены ко входам шифратора и являются входами устройства, выходы шифратора подключены ко входам третьей группы накопителя, выходы первой и второй групп которого подключены ко входам блока контроля, выходы блока контроля подключены ко входам элемента ИЛИ и к первым входам соответствующих элементов И первой группы, выход элемента ИЛИ подключен ко вторым входам элементов И первой группы, выходы которых подключены к первым входам соответствующих сумматоров по модулю два, вторые входы сумматоров по модулю два подключены к соответствующим выходам первой группы накопителя , выходы сумматоров по модулю два являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит вторую группу элементов И, входы которых подключены к соответствующим входам первой группы накопителя, выходы элементов И второй группы подключены ко входам четвертой группы накопителя, и третью группу элементов И, одни входы которых подключены к соответствующим выходс м первой группы накопителя, другие входы элементов И третьей группы подключены к соответствующим выходам третьей группы накопителя, выходы элементов И третьей группы подключены к третьим входам соответствующих элементов И первой группы. : Источники информации, принятые во внимание при экспертизе 1. Самофалов К.Г., Корнейчук В.И., Городний А.В. Структурно-логические методы повышения надежности запоминающих устройств. М., Машиностроение, 1976, с. 101 - 106.. 2 i Авторское свидетельство СССР по заявке 3256760/18-24, кл.( 11 С 29/00, 1981 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1988 |

|

SU1532979A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU964736A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ВЫХОДНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2006971C1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1361624A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

Авторы

Даты

1983-03-15—Публикация

1981-11-26—Подача