а

СП

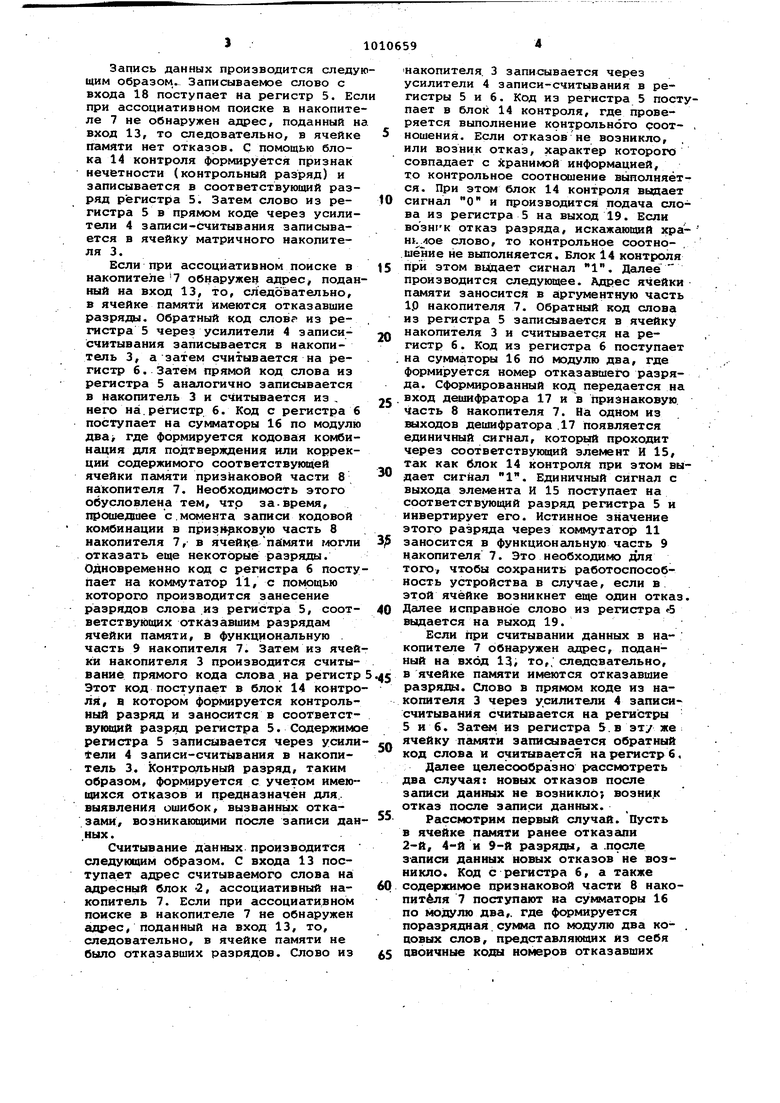

со Изобретение относится к запомин щим устройствам. По основному авт. св. 936033 известно устройство, содержащее асс циативный накопитель, одни информационные входы которого подключены к выходам первого коммутатора, выходы к одним из входов второго коммутатора, а другие информационные входы ассоциативного накопителя подключен к входам адресного блока и являются адресными входами устройства, матри ный накопитель, адресные.входы кото рого подключены к выходам адресного блока, а информационные входы и выходы - к одним из выходов и входо усилителей записи-считывания соответственно, первый регистр слова , входы и выходы которого подключены к другим выходам и входам усилителей записи-считывания, второй комму татор, одни из выходов которого подключены к одним из входов первог регистра слова, другие входы которо го являются информационными входами устройства, одни входы первого комм татора подключены к одним из выходов первого регистра слова, другие выходы которого являются выходами устройства/ второй регистр слов.а, входы которого подключены к выходам усилителей записи-считывания, а выходы - к другим входам первого и второго коммутаторов С В этом устройстве при записи и считывании данных производится ко.нт роль работоспособности ячеек памяти При загУиси разряды кодовой комбинации, соответствующие отказавшим разрядам ячейки памяти, заносятся .в ассоциативный накопитель. При счи тывании кодовой комбинации отказавшие разряды ячейки подменяются данными из ассоциативного накопителя. Однако, если после записи кодовой комбинации возникает отказ, то рабо тоспособность такого устройства нарушается. Таким образом, недостатком данно устройства является низкая достовер ность считываемых данных. Цель изобретения - повышение надежности устройства за счет повышен достоверности считывания данных. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем введены элементы И, сумматоры по модулю два, дешифратор и блок контроля, вход ко торого соединен с выходом первого р гистра слова, один выход - с одним из входов первого регистра слова, а другой выход - с первыми входами эл ментов И, вторые входы которых подключены к выходам дешифратора, а выходы - к другим входам первого регистра слова, первые входы сумматоров по модулю два соединены с выходом второго регистра слова, вторые входы - с одними из выходов ассоциативного накопителя, выходы сумматоров по модулю два подключены соответственно к одному из входов ассоциативного накопителя, входам дешифратора и одним из входов второго коммутатора. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит адресный блок i памяти, состоящийиз гщресного блока 2, матричного накопителя 3, усилителей 4.записи-считывания и первого регистра 5 слова, второй регистр 6 слова и ассоциативный накопитель 7, который имеет признаковую часть 8 для хранения поразрядной суммы по модулю два кодовых слов,, представляющий из себя двоичный код номеров отказавших разрядов,, функциональную часть 9для подмены отказавших разрядов и аргументную часть 10 для запоминания адреса отказавших ячеек адресного блока 1 памяти. Устройство также содержит первый 11 и второй 12 коммутаторы, адресный вход 13, блок 14 контроля, элементы И 15, сумматоры 16 по модулю два, дешифратор 17, Устройство имеет вход 18 и выход 19. Устройство работает следующим образом. В паузах между внешниь й обращениями производится контроль работоспособности ячеек памяти адресного блока 1 памяти. При обнаружении отказов в какой-либо ячейке памяти определяется кратность ошибки и адрес неработоспособной ячейки памяти записывается в аргументную часть 10 накопителя 7, причем кратность ошибки соответствует количеству разрядов функциональной части 9 накопителя 7. Обнаружение отказов производится с помощью регистра 6, на который последовательно считывается. из ячейки памяти прцсмой и обратный код числа. Одновременно с записью адреса в накопитель 7 код с регистра 6 поступает на сумматоры 16 по модулю два, где формируется поразрядная сумма по модулю два кодовых слов, представляющих из себя двоичный код номеров отказавших разрядов. Например, если отказали 2-й, 4-й, 9-й разряды ячейки памяти, то на выходе сумматоров 16 сформируется код 1111, т.ак как ppl0301000@1001 1111. Этот код записывается в признаковую часть 8 соответствующей ячейки памяти накопителя 7. Приобращении к запоминающему устройству по адресу, установленному на входе 13, происходит одновременное обращение как к адресному блоку 1, так и к ассоциативному накопителю 7. Запись данных производится следу щим образом. Записываемое слово с входа 18 поступает на регистр 5. Ес при ассоциативном поиске в накопите ле 7 не обнаружен адрес, поданный н вход 13, то следовательно, в ячейке памяти нет отказов. С помощью блока 14 контроля формируется признак нечетности (контрольный разряд) и записывается в соответствующий разряд регистра 5. Затем слово из регистра 5 в прямом коде через усилители 4 записи-считывания записывается в ячейку матричного накопителя 3. Если при ассоциативном поиске в накопителе 7 обнаружен адрес, подан ный на вход 13, то, следовательно, в ячейке памяти имеются отказавшие разряды. Обратный код словг из регистра 5 через усилители 4 записисчитывания записывается в накопитель 3, а затем считывается на регистр 6. Затем прямой код слова из регистра 5 аналогично записывается в накопитель 3 и считывается из него на.регистр б. Код с регистра 6 поступает на сумматоры 16 по модулю два где формируется кодовая комбинация для подтверждения или коррекции содержимого соответствукицей ячейки памяти признаковой части 8 накопителя 7. Необходимость этого обусловлена тем, чтр за-время, прешедшее с.момента записи кодовой комбинации в призн|1кову|р часть 8 накопителя 7, в ячейкепоЕмяти f/югли отказать еще некоторые разряды. Одновременно код с регистра 6 посту пает на коммутатор 11, с помощью которого производится занесение разрядов слова .из регистра 5, соответствующих отказавшим разрядам ячейки памяти, в функциональную . часть 9 накопителя 7. Затем из ячей ки накопителя 3 производится считыванне прямого кода слова на регистр Этот код поступает в блок 14 контр ля, в котором формируется контроль ный разряд и заносится в соответст вующий разряд регистра 5. Содержим регистра 5 записывается через усил тели 4 записи-считывания в накопитель 3. Контрольный разряд, таким образом, формируется с учетом имею щихся отказов и предназначен для., выявления ошибок, вызванных отказами, возникающими после записи да ,ных. Считывание данных производится следующим образом. С входа 13 поступает адрес считываемого слова на адресный блок -2, ассоциативный накопитель 7. Если при ассоциативном поиске в накопктеле 7 не обнаружен адрес, поданный на вход 13, то, следовательно, в ячейке памяти не было отказавших разрядов. Слово из накопителя. 3 записывается через усилители 4 записи-считывания в регистры 5 и 6. Код из регистра 5 поступает в блок 14 контроля, где проверяется выполнение контрольного роот- , ношения. Если отказов не возникло, или возник отказ, характер которого совпадает с хранимой информацией, то контрольное соотношение выполняется. При этом блок 14 контроля вьщает сигнал О и производится подача слова из регистра 5 на выход 19. Если возник отказ разряда, искажающий храш.лов слово, то контрольное соотношение не выполняется. Блок 14 контроля при этом выдает сигнал 1. Далее производится следующее. Адрес ячейки памяти заносится в аргументную часть IP накопителя 7. Обратный код слова из регистра 5 записывается в ячейку накопителя 3 и считывается на регистр 6. Код из регистра 6 поступает на сумматоры 16 по модулю два, где формируется номер отказавшего разряда. Сформированный код передается на вход дешифратора 17 и в признаковую, часть 8 накопителя 7. На одном из выходов дешифратора .17 появляется единичный сигнал, которь1й проходит через соответствукмций элемент И 15, так как блок 14 контроля при этом выдает сигнал 1. Единичный сигнал с выхода элемента И 15 поступает на соответствующей разряд регистра 5 и инвертирует его. Истинное значение этого разряда через коммутатор 11 заносится в функциональную часть 9 накопителя 7. Это необходимо для того, чтобы сохранить работоспособность устройства в случае, если в этой ячейке возникнет еще один отказ. Далее исправное слово из регистра 5 выдается на выход 19. Если гфи считывании данных в на копителе 7 обнаружен адрес, поданный на вход 13, то,, следсвательно, в ячейке памяти имеются отказавшие разряды. Слово в прямом коде из накопителя 3 через усилители 4 записи считывания считывается на регистры 5 и 6. Затем из регистра 5.в эту же ячейку пгьмяти записывается обратный код слова и считывается на регистр 6, Далее целесообразно рассмотреть два случая: новых отказов после записи данных не возникло; возни.к отказ после зешиси даиных. Рассмотрим первый случай. Пусть в ячейке памяти ранее отказгши 2-й, 4-й и 9-й разряды, а .после записи данных новых отказов не возникло. Код с регистра 6, а также содержимое признаковой части В накопителя 7 поступают на сумматоры 16 по модуто два,, где формируется поразрядная сумма по модулю два ко- . цовых слов, представляющих из себя авоичные коды номеров отказавших , разрядов, и .содержимого признаковой части 8 накопителя 7. Для рассматриваемого примера сформируется код ,роро, так как G01-0®0100©flOO @llll 0000 . Код 0000 свидетельствует о том, что новых отказов не возникло. При этом код с регистра 5 поступает в блок 14 контроля, который выдает сигнал О. Содержимое функциональной части 9 (для рассматриваемого примера истинные значения 2-го,4-го и 9-го разрядов) через коммутатор 12 посту ,пает на регистр 5, Далее исправленно слово из регистра 5 выдается на выход 19. Рассмотрим второй случай. Пусть ячейке памяти ранее отказали 2-й, 4-й и 9-йразряды, а после записи данных отказал 7-й разряд. .Код с ре гистра б, а также содержимое призна ковой части 8 накопителя 7 поступают на сумматоры 16 по модулю два, где формируется код 0111, так как 0010@0100@0111@1003@1-111 0111- Код 0111 указывает на то, что после записи данных 7-й разряд отказал. Далее может возникнуть две ситуации: либо отказавший после записи данных разряд согласован с хранимой информацией, либо нет. Если имеет место первая ситуация то, следовательно, искажения записанного слова не произошло и блок 1 контроля при этом, вьщает сигнал О Код 0111 с сумматоров 16 по модулю два поступает на коммутатор 12, обе печивая блокировку выдачи в 7-й раз .ряд регистра 5 содержимого функциональной части 9 накопителя 7. Тем самым обеспечивается правильная подмена отказавших ранее разрядов. т.е. 2-го, 4-го и 9-го. Истинные значения этих разрядов из функциональной части 9 накопителя 7 передаются в регистр 5 через коммутатор 12. ЗатемСЛОВО из регистра 5 выдается на выход 19. Кроме того, как и при считывании слова из ячейки памяти, где ранее не было отказа, а после записи данных возник, производится подмена всех отказавших разрядов. При этом выбирается свободная ячейка памяти наКопителя 7, в которой функциональная часть на один разряд больше,.чем у используемой ранее. Если имеет место вторая группа, то блок 14. контроля при этом выдает сигнал 1, так как произошло искажение записанного слова. Аналогично предыдущей ситуации, через коммутатор 12 .из функциональной части 9 накопителя 7 передаются в регистр 5 истинные значения 2-го, 4-го и 9-го разрядов. Кроме того, код 0111 из сумматоров 16 по модулю два поступает на дешифратор 17. Это приводит к появлению единичного сигнала на соответствующем выходе дешифратора 17 , который через один из элементов И 15 поступает на 7-ой разряд регистра 5 и инвертирует его. Далее слово из регистра 5 поступает на выход 19 и как и в предыдущей ситуации производится подмена отказавших разрядов ячейки памяти с учетом разряда, который отказал после записи слова. - Таким образом, предлагаемое устройство в отличие от известного fl сохраняет работоспособность в томслучае, если после записи данных в ячейку памяти отказывает один раз ряд. Это приводит к повышению достоверности считывания данных и, следовательно, надежности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

ЗАПОМИНАНЯДЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ по авт. ев, 936033, отличающее с я тем, что,.,с целью повышения надежности устройства, оно содержит элементы И, сумматоры по модулю два, дешифратор и блок контроля, вход которого соединен с выходом первого регистра слова, один выход -с одним из входов первого регистра слова, а другой выход - с первыми входами элементов И, вторые входы которых подключены к выходам дешифратора, а выходы - к другим входам первого регистра слова, первые входы сумматоров по Модулю два соедшнены с выходом второго регистра слова, вторые входы - с одними из выходов ассоциа- ивного накопителя, эыходы сумматоров по модулю два подключены соответственно кодному КЗ входов ассоциативного накопителя, входам;дешифратора и.одним из входов второго коммутатора. л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| . | |||

Авторы

Даты

1983-04-07—Публикация

1981-10-16—Подача