Изобретение относится к вычислительной технике и может найти применение при построении универсальных и специализированных ЭВМ высокой производительности .

Цель изобретения - повышение надежности путем сокращения числа внешних выводов.

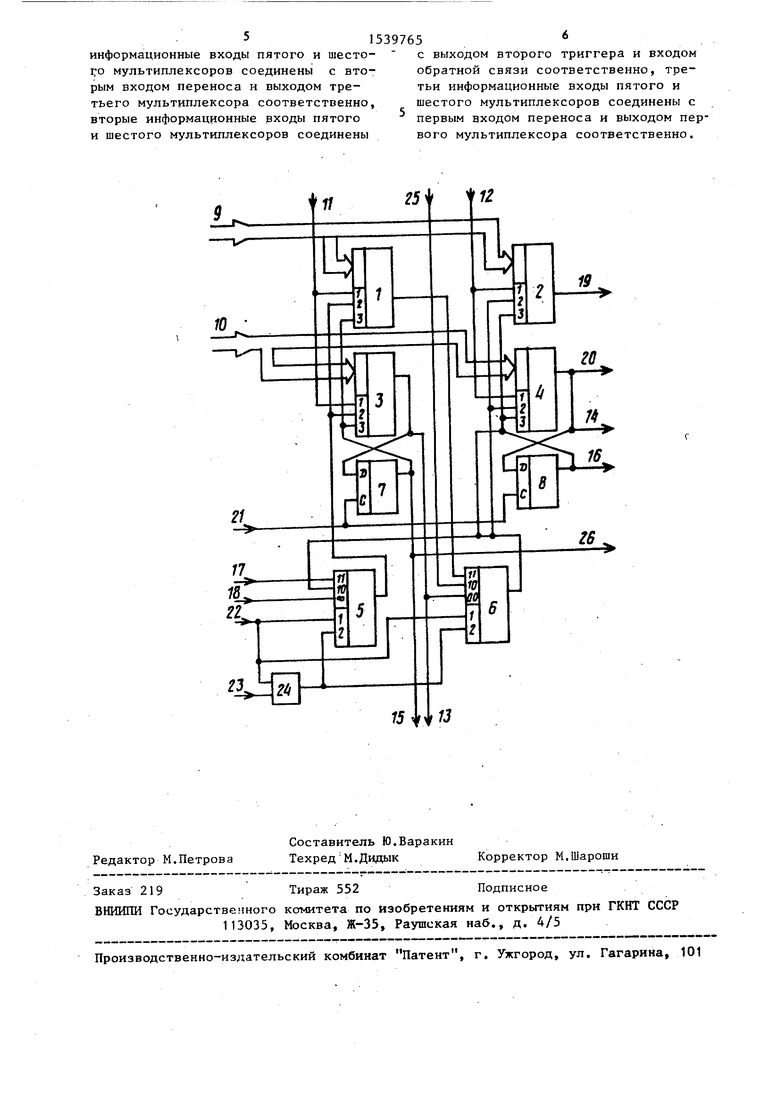

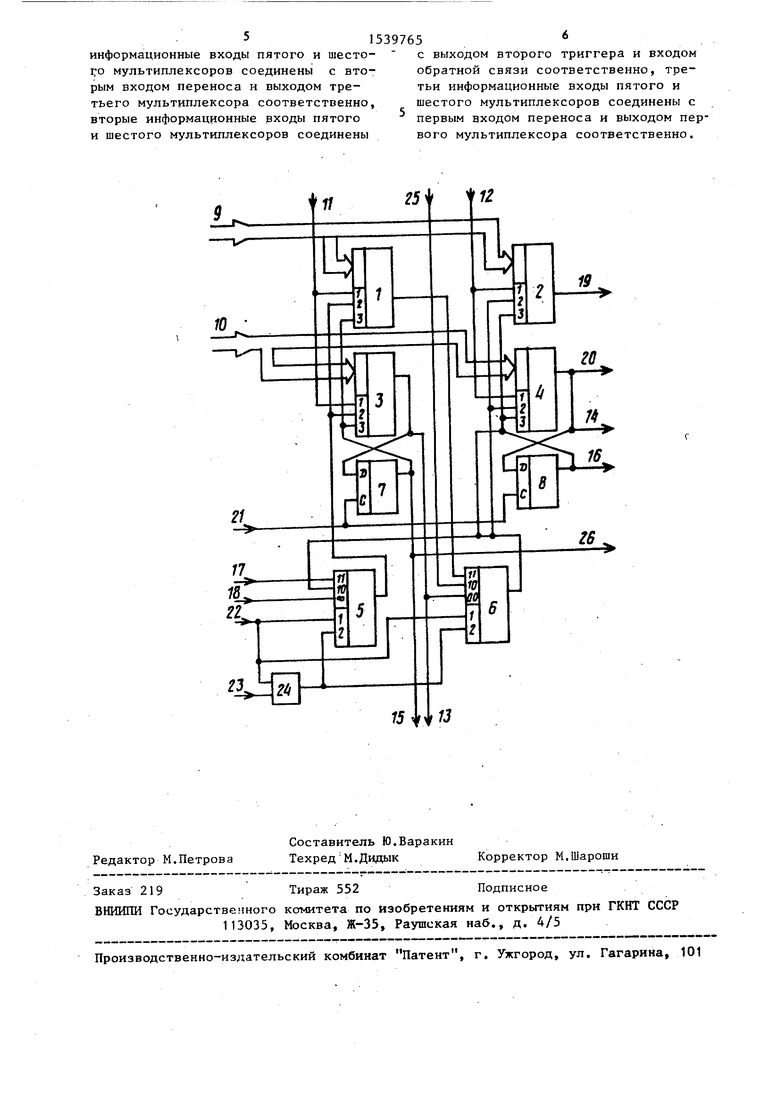

На чертеже приведена функциональная схема арифметико-логического модуля.

Арифметико-логический модуль содержит мультиплексоры 1-6, триггеры 7 и 8, шины 9 и 10 управления, входы 11 и 12 данных нулевого и первого разрядов, асинхронные выходы 13 и 14 нулевого и первого разрядов, нулевой и первый выходы 15 и 16 данных, входы 17 и 18 переноса, выходы 19 и 20 переноса, шину 21 тактовых импульсов, шину 22 выбора режима и дополнительную шину 23 выбора режима, элемент И 24, вход 25 обратной связи, выход 26 обратной связи.

Арифметико-логический модуль работает следующим образом.

Двоичный код, подаваемый по восьмиразрядным шинам 9 и 10 управления, задает вид реализуемой операции над двумя операндами, один из которых записан в триггерах 7 и 8, а другой установлен на входах 11 и 12 данных

нулевого и первого разрядов. На выходах мультиплексоров 3 и 4 формируются нулевой и первый разряды результата операции соответственно. При этом i-й разряд результата (нулевой или первый) в зависимости от уровня сигналов на шине 22 выбора режима и дополнительной шине 23 выбора режима является переключательной функцией трех аргументов; сигнала на входе

СЛ

СО СО

О5 СЛ

данных i-го разряда, сигнала на i-м выходе данных и сигнала на входе 18 переноса или с выхода мультиплексора 3 при уровне сигнала на шине 22 выбора режима, равном лог. О, либо первых двух аргументов, указанных выше, и сигнала на входе 17 первого переноса или на выходе мультиплексора 1 при уровнях сигналов на шине 22 выбора режима и дополнительной шине 23 выбора режима, равных лог. 1, либо первых двух аргументов, указанных выше, и сигнала с выхода мультиплексора 4 или на входе 25 обратной связи при уровне сигнала на шине выбора режима, равном лог. 1, а на дополнительной шине 23 выбора режима - лог. О. Вид этой операции определяется двоичным кодом, подаваемым по шине 10 управления .

Одновременно на выходах мультиплексоров 1 и 2 формируются сигналы первого переноса из нулевого и первого разрядов, которые являются переключательными функциями тех же аргументов, что и разряды результата операции, в зависимости от уровней сигналов на шине 22 выбора режима и дополнительной шине 23 выбора режима. Вид этой функции определяется двоичным кодом, подаваемым по шине 9 управления .

По фронту тактового импульса, поступающего по шине 21 тактовых импуль-35 pbIM выходами переноса соответственно,

Код, записанный в триггеры 7 и 8, остается неизменным до прихода фронта следующего тактового импульса.

Формула изобретения

Арифметико-логический модуль, содержащий шесть мультиплексоров, два триггера, две шины управления, входы данных нулевого и первого разрядов асинхронного выхода нулевого и первого разрядов, нулевой и первый выход данных, первый и второй выходы пере- г носа, первый и второй входы переноса, шину тактовых импульсов, вход и выход обратной связи, шину выбора режима, причем входы данных нулевого и первого разрядов соединены с первыми управляющими входами первого, третьего и второго, четвертого мультиплексоров соответственно, вторые управляющие входы первого, третьего и второго, четвертого мультиплексоров соединены с выходами пятого и шестого мультиплексоров соответственно, третьи управляющие входы первого, третьего и второго, четвертого мультиплексоров соединены с выходами данных соответственно выходы третьего и четвертого мультиплексоров соединены с асинхронными выходами нулево- . го и первого разрядов соответственно, выходы второго и четвертого мультиплексоров соединены с первым и вто0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Микропроцессорная секция | 1979 |

|

SU842789A1 |

| Многофункциональное устройство | 1988 |

|

SU1520503A1 |

| Арифметико-логический модуль | 1988 |

|

SU1501032A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Многофункциональный модуль | 1984 |

|

SU1238098A1 |

| Устройство линейного кодирования | 1990 |

|

SU1783544A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных ЭВМ в качестве арифметико-логического модуля. Цель изобретения - повышение надежности устройства за счет сокращения числа внешних выводов. Арифметико-логический модуль содержит шесть мультиплексоров, два D-триггера, элемент И, две шины управления, входы данных, входы переноса, вход обратной связи, шину тактовых импульсов, шину выбора режима, дополнительную шину выбора режима, выходы нулевого и первого разрядов, выходы данных, выходы переноса, выход обратной связи. 1 ил.

сов на синхронизирующие входы триггеров 7 и 8, происходит запись кода результата операции с асинхронных выходов 13 и 14 нулевого и первого разрядов в триггеры 7 и 8. Одновременно сигнал с выхода триггера 7 поступает на выход 26 обратной связи, сигнал с выхода триггера 8 - на второй информационный вход мультиплексора 5, сигнал с входа 25 обратной связи - на второй информационный вход мультиплексора 6. При этом начинается формирование нового кода результата операции, нулевой разряд которого посту- пает на первый информационный вход мультиплексора 6, а первый - на выход 20 переноса, причем на второй информационный вход мультиплексора 5 поступает сигнал с входной шины 18 переноса. Одновременно происходит формирование сигнала первого переноса, который с выхода мультиплексора 2 поступает на выход 19 переноса.

0

5

входы первого и второго триггеров соответственно соединены с выходами третьего и четвертого мультиплексоров, синхронизирующие входы первого и второго триггеров соединены с шиной тактовых импульсов, первая и вторая шины управления соединены с информационными входами первого, второго и третьего, четвертого мультиплексоров соответственно, отличающийся тем, что, с целью повышения надежности путем сокращения числа внешних выводов, в него введены элемент И и дополнительная шина выбора режима, причем шина выбора режима соединена с первыми управляющими входами пятого и шес.того мультиплексоров, а также с первым входом элемента И, второй вход которого со- 5 единен с дополнительной шиной выбора режима, выход элемента И соединен с вторыми управляющими входами пятого и шестого мультиплексоров, первые

0

.1

информационные входы пятого и шестого мультиплексоров соединены с вторым входом переноса и выходом третьего мультиплексора соответственно, вторые информационные входы пятого и шестого мультиплексоров соединены

1

,

1539765

с выходом второго триггера и входом обратной связи соответственно, третьи информационные входы пятого и шестого мультиплексоров соединены с первым входом переноса и выходом первого мультиплексора соответственно.

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1988-02-01—Подача