(54) МИКРОПРОЦЕССОРНАЯ СЕКЦИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Устройство для обучения микропрограммированию | 1983 |

|

SU1243011A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при- построении универсальных

ЭВМ.

Известна микропроцессорная секция содержащая О-триггеры и элементы И

Недостаток ее - ограниченные функциональные возможности.

Известна также микропроцессорная секция, содержащая регистр-аккумулятор и группы шин f2.

Недостаток этой секции - ограниченный набор переключательных функций .

Наиболее близкой по технической сущности к предлагаемой является микропроцессорная секция, содержащая регистр-аккумулятор, группы шин управления, шины данных функционального переноса и шину тактовых импульсов. f2 .

Недостаток известной секции - ограниченные функциональные возможности, обусловленные тем,, что каждый разряд результата и функ циональный перенос влево описываются ограниченным набором переключательных функций трех аргументов: разрядов операндов и функционапьного переноса влево з

предыдущего разряда. Это позволяет реализовать лишь шесть основных операций, выполняемых за один такт синхронизации: арифметическое сложение в дополнительных кодах, поразрядные логические сложение, умножение и инверсия суммы по mod 2 сдвиг влево и вправо на один разряд. Функциональный перенос вправо сводится к одной

операции - сдвигу вправо на один разряд.

Цель изобретения - расширение функциональных возможностей микропроцессорной секции.

Поставленная цель достигается

тем, ч:то в микропроцессорную секцию, содержащую триггеры нулевого и первого разрядов группы шин управления, входные и выходные шины дайных, входную и выходные шины функционального переноса влево, входную и первую выходную шины функционального переноса вправо и шину тактовых импульсов, соединенную с синхронизирующими входами

триггеров нулевого и первого разрядов, дополнительно введены вторая выходная шина функционального переноса вправо и первый, второй третий, четвертый, Jпятый, шестой, седьмой и восьмой муль,типлексоры, причем первая, вторая.

третья и четвертая группы шин управления соединены с информационными входами соответственно первого, второго, третьего и четвертого мультиплексоров, первые управляющие входы которых соединены с входнойшиной данных а вторые управляющие входы первого, второго и третьего мультиплексоров соединены с первой входной тиной функционального переноса влево, третий управляющий вход первого мультиплексора соединен с выходом триггера нулевого разряда, первый выходной шиной данных и вторым управляющим входом четвертого мультиплексора, выход которого соединен с первой выходной шиной .функционального переноса вправо, а третий управляющий вход четвертого мультиплексора - со второй выходной шиной функционального переноса вправо, с третьими управляющими входами второго и третьего мультиплексоров, вторая входная шина данных соединена с первыми управляющими входами пятого, шестого, седьмого и восьмого мультиплексоров, информационные входы которых соединены соответственно с первой, второй,третьей и четвертой группами шин управления, вторые управляющие входы пятого, шестого и седьмого мультиплексоров соединены с выходами первого мультиплексора и с первой выходной шиной функционального переноса влево, третий управляющий вход пятого мультиплексора соединен с выходом триггера первого разряда, со второй выходной шиной данных и со вторым управляющим входом восьмого мультиплексора, третий управляющий вход которого соединен с третьими управляющими входами шестого и седьмого мультиплексоров и со входной шиной функционального переноса вправо, Выход пятого мультиплексора соединен со второй выходной шиной функционального переноса влево, выход шестого мультиплексора соединен с шестым J-входом триггера первого разряда, к вход которого соединен с инверсным выходом седьмого мультиплексора, выход восьмого мультиплексора соединен со второй выходной шиной функционального переноса вправо, выход второго мультиплексора соедине с J-входом триггера нулевого разряда к-вход которого соединен с инверсным выходом третьего мультиплексора.

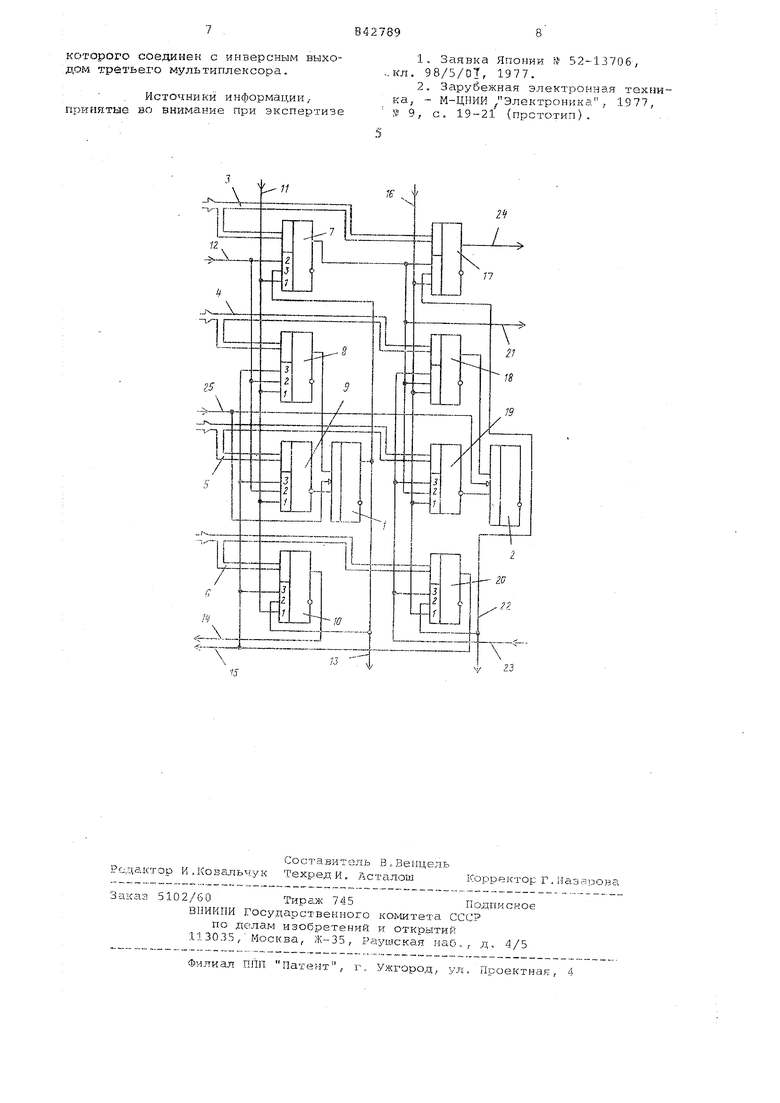

На чертеже представлена функциональная схема микропроцессорной секции .

Схема содержит, триггеры 1 и 2 нулевого и первого разрядов, первую, вторую, третью и четвертую группы шин 3-6 управления, первый, втсфой, третий и четвертый .мультиплексоры 7-10, первую входную ишну 11 данных и входную шину 12 функционального переноса влево, первые выходные шины данных 13 и функционального переноса

вправо 14, вторую выходную шину 15 функционального переноса вправо, вторук) входную шину 16 данных, пятый, шестой, седьмой и восьмой мультиплексоры 17-20, первую выходную шину 21 функционального переноса влево,,вторую выходную шину 22 данных, входную шину 23 функционального переноса вправо, вторую выходную шину 24 функционального переноса влево и шину 25 тактовых импульсов.

Микропроцессорная секция работает следукяцим образом.

Двоичный код, подаваемый по группам шин 3-6 управления задает вид реализуемой операции над Двумя оперендами, один из ко.торых записан в триггер 1 и 2, а второй установлен на входных шинах 11 и 16 данных. На выходах мультиплексоров 8,9 и18 и 19 формируются сигналы, определяющие нулевой и первый соответственно разряды кода результата операции. При этом i-тый разряд результата (нулевой или первый является переключательной функцией четырех аргументов: сигнала на i-той выходной шине данных первой 13 или второй 22, сигнала на i-тойвходной шине данных (первой 11 .или второй 16) сигнала функционального переноса влево, поступающего по входной шине 12 функционального переноса влево или непосредственно с выхода мультиплексора 7 и сигнала функционального переноса вправо, поступающего непосредственно с выхода мультиплексора 20 или по входной шине 23 функционального переноса вправо. Вид этой функции определяется двоичным кодом, подаваемым по группам шин 4 и 5 управления. Одновременно на выходах мультиплексоров 7 и 10 формируются сигналы функциональных переносов из нулевого разряда влево и вправо, которые, поступают на первые выходные шины функционального переноса влево 21 и вправо 14 соответственно. Аналогично на выходах мультиплексоров 17 и 20 форг шруются сигналы функционального переноса из первого разряда лево и вправо, которые поступают на вторые выходные шины функционального переноса влево 24 и вправо 15соответственно. Сигналы функционального перенса влево i -того разряда являются преключательными функциями трех аргументов: сигнала на i-той выходной шине данных (первой 13 или второй 22) сигнала на i-той входной шине данных (первой 11 или второй 16) и сигнала функционального переноса влево из (i-l)-ro разряда, поступающего по входной шине функционального переноса влево 12 или непосредственно с выхода мультиплексора 7. Сигналы функционального переноса вправо из i-того разряда являются переключательными функциями трех аргументов: сигнала на i-той выходной шине данных (первой 13 или второй 22), сигнгша на I:ТОй входной шине данных (первой 11 . или второй 16) и сигнала функциональ ного переноса вправо из {i+l)-ro разряда, поступающего непосредственно с выхода мультиплексора 20 или по входной шине 23 функционального пере носа вправо. Вид этих функций определяется двоичными кодами, подаваемы ми по rpiynnaM шин 3 и 6 управления. По фронту тактового импульса, пос упающего по шине 25 тактовых импул сов на вход синхронизации триггеров 1 и 2, происходит запись кода резуль тата операции в разряды триггеров 1 и 2. Этот код подается на первую 13 и вторую 22 выходныешины данных. Код, записанный в триггерах 1 и 2 ос тается неизменным до прихода фронта, следующего тактового имПульса. Эффективность изобретения заключа ется в расширении функциональных воз можностей микропроцессорной секции, за счет обеспечения реализации 2 4,294 (количество возможных кодовых комбинаций на четырех группах шин управления) различных арифметико-логических операций с дву мя операндами, каждая из которых выполняется за один такт синхронизации. Это обусловлено тем, что каждый разряд результата описывается полным набором всех возможных переключатель ных функций четырех аргументов: разрядов операндов и функциональных переносов влево и вправо. А каждый фун циональный перенос влево и вправо описывается полным набором всех возможных переключательных функций трех аргументов: разрядов операндов и фун кционального переноса влево из преды дущего разряда или вправо из последующего, соответственно. Предлагаемая секция позволяет реализовать 16 пора.зрядных логических операций , из которых лишь 3 выполняются известной секцией, а также совмещенныеоперации, например арифметичес1$ое сложение в дополнительных кодах с одновре менным инвертированием или другим . преобразованием кода результата и т.п. Реализация за один такт совмещенных арифметико-логических операций позволяет повысить быстродействие микропроцессорной секции. Формула изобретения Микропроцессорная секция, содержащая триггеры нулевого .и первого разряда, группы шин управления, входные и выходные шины данных, вводную и выходные шины функционального переноса влево, входную и первую выходную ши- ну функционального переноса вправо и ,шину тактовых импульсов,соедиЕщнную с синхронизирую1дими входами триггеров нулевого и первого разряда, о тличающаяся тем, что, с целью расширения функциональных возможностей за счет увеличения числа арифметико-логических операций с операндами, в нее дополнительно введены вторая выходная шина функционального переноса вправо, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой мультихгпексоры, причем первая, вторая, третья и четвертая группы шин управления соединены с информационными входами соответственно первого, второго, третьего и четвертого мультиплексоров, первые управляющие входы которых соединены с пергвой входной шиной данных, а вторые управляющие входы первого,, второго и третьего мультиплексоров соединены с входной шиной функционального переноса влево, третий управляющий вход Первого мультиплексора соединен с выходом триггера нулевого разряда первой выходной шиной данных и вторым управляющим входом четвертого мультиплексора, выход которого соединен с первой выходной шиной функционального переноса вправо, а третий управляющий вход четвертого мультиплексора - со второй выходной шиной функционсшьного переноса вправо, и с третьими управляющими входами второго и третьего мультиплексоров, вторая входная шина данных соединена с первыми управляющими входами пятого, шестого, седьмого и восьмого мультиплексоров, информационные входы которых соединены соответственнос первой , второй, третьей и четвертой группами шин управления, вторые управляющие входы пятого, шестого и седьмого мультиплексоров соединены с выходами первого мультиплексора и с первой выходной шиной функционального переноса влево, третий управляющий вход пятого мультиплексора соединен с выходом триггера первого разряда, со второй выходной шиной данных и со вторым управляющим входом восьмого мультиплексора, третий управляклций вход которого соединен с третьими управляющими входами шестого и седьмого мультиплексоров и со входной шиной функционального переноса вправо, выход пятого мультиплексора соединен со второй выходной шиной функционального переноса влево, выход шестого мультиплексора соединен с J-входом триггера, первого разряда, К-вход которого соедине.н с инверсньич выходом седьмого мультиплексора, выход восьмого мультиплексора соединен со второй выходной шиной функционального переноса вправо, выход второго мультиплексора соединен с J-входом шриггера нулевого разряда, к-вход которсэго соединен с инверсным выходом третьего мультиплексора. Источники информации, принятые во внимание при экспертизе ; . ; . 5 . 1.Заявка Японии № 52-13706, кл. 98/5/ОТ, 1977. 2.Зарубежная электронная техника, - М-ЦНИИ Электроника, 1977, № 9, с. 19-21 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-04-12—Подача