Лад задания шГ координат

ВХОд TfZf

упраЬлвниь ДЛХ

Взюд адреса

J/VT-V5

Изобретение относится к вычислительной технике и может быть применено з специализированных вычислителях.

Цель изобретения - расширение класса решаемых задач за счет возможности выполнения перспективных преобразований путем масштабирования координат X,Y в зависимости от значения координаты Z имитируемого объекта.

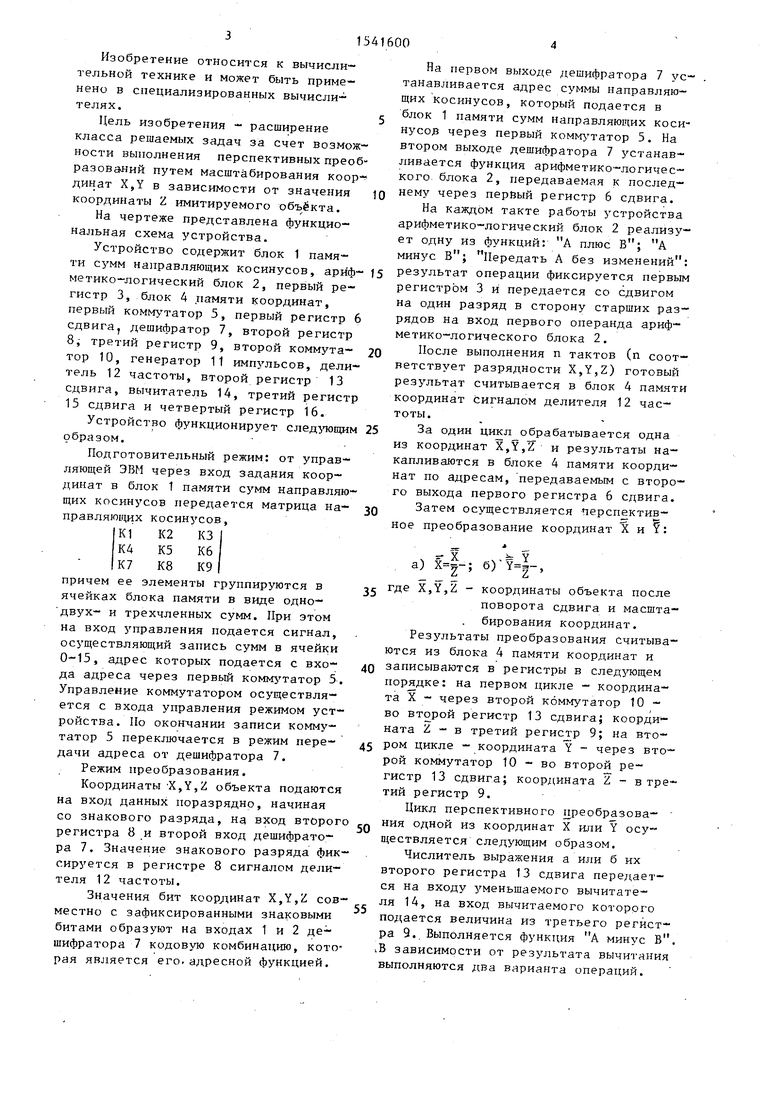

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 памяти сумм направляющих косинусов, арифметико-логический блок 2, первый регистр 3, блок 4 памяти координат, первый коммутатор 5, первый регистр 6 сдвига, дешифратор 7, второй регистр 8, третий регистр 9, второй коммутатор 10, генератор 11 импульсов, делитель 12 частоты, второй регистр 13 сдвига, вычитатель 14, третий регистр 15 сдвига и четвертый регистр 16.

Устройство функционирует следующим образом.

Подготовительный режим: от управляющей ЭВМ через вход задания координат в блок 1 памяти сумм направляющих косинусов передается матрица направляющих косинусов, К1 К2 КЗ К4 К5 Кб К7 К8 К9

причем ее элементы группируются в ячейках блока памяти в виде одно- двух- и трехчленных сумм. При этом на вход з правления подается сигнал, осуществляющий запись сумм в ячейки 0-15, адрес которых подается с входа адреса через первый коммутатор 5. Управление коммутатором осуществляется с входа управления режимом устройства. Но окончании записи коммутатор 5 переключается в режим передачи адреса от дешифратора 7.

Режим преобразования.

Координаты X,Y,Z объекта подаются на вход данных поразрядно, начиная со знакового разряда, на вход второго регистра 8 и второй вход дешифратора 7. Значение знакового разряда фиксируется в регистре 8 сигналом делителя 12 частоты.

Значения бит координат X,Y,Z совместно с зафиксированными знаковыми битами образуют на входах 1 и 2 дешифратора 7 кодовую комбинацию, которая является его.адресной функцией.

0

5

0

5

Q

0

5

0

5

5

На первом выходе дешифратора 7 устанавливается адрес суммы направляющих косинусов, который подается в блок 1 памяти сумм направляющих косинусов через первый коммутатор 5. На втором выходе дешифратора 7 устанавливается функция арифметико-логического блока 2, передаваемая к последнему через первый регистр 6 сдвига.

На каждом такте работы устройства арифметико-логический блок 2 реализует одну из функций: А плюс А минус Передать А без изменений : результат операции фиксируется первым регистром 3 и передается со сдвигом на один разряд в сторону старших разрядов на вход первого операнда арифметико-логического блока 2.

После выполнения п тактов (п соответствует разрядности X,Y,Z) готовый результат считывается в блок 4 памяти координат сигналом делителя 12 частоты.

За один цикл обрабатывается одна из координат X,Y,1T и результаты накапливаются в блоке 4 памяти координат по адресам, передаваемым с второго выхода первого регистра 6 сдвига.

Затем осуществляется перспектив- ное преобразование координат X и Y:

Л

а) 6),

где X,Y,Z - координаты объекта после поворота сдвига и масштабирования координат.

Результаты преобразования считываются из блока 4 памяти координат и записываются в регистры в следующем порядке: на первом цикле - координата X - через второй коммутатор 10 - во второй регистр 13 сдвига; координата Z - в третий регистр 9; на втором цикле - координата Y - через второй коммутатор 10 - во второй регистр 13 сдвига; координата Z - в третий регистр 9.

Цикл перспективного преобразования одной из координат X или Y осуществляется следующим образом.

Числитель выражения а или б их второго регистра 13 сдвига передается на входу уменьшаемого вычитате- ля 14, на вход вычитаемого которого подается величина из третьего регистра 9. Выполняется функция А минус В. ;В зависимости от результата вычитания выполняются два варианта операций.

515

I.Если А-В 0; с выхода переноса вычитателя 14 в третий регистр 15

сдвига передается сдвигаемый бит 1, остаток А-В через второй коммутатор Ш со сдвигом на один бит в сторону старших разрядов передается во второй регистр 13 сдвига.

II.Если А-1ХО, с выхода переноса вычитателя 14 в третий регистр 15 сдвига передается сдвигаемый бит О, остаток А-В системой игнорируется, первый операнд во втором регистре сдвига удваивается сдвигом на один бит в сторону старших разрядов.

Алгоритм повторяется в цикле п раз, где п - количество разрядов координат X,Y.;Z. По завершению цикла в третьем регистре- 15 сдвига накапливается результат перспективного преобразования координаты X или Y, который подается на первый вход четвертого регистра 16 и фиксируется на выходе данных устройства.

Координата Z без преобразования передается из блока 4 памяти на выход устройства через второй вход четвертого регистра 16.

Формула изобретения

Устройство для преобразования координат, содержащее три регистра, первый регистр сдвига, блок памяти сумм направляющих косинусов, арифметико-логический блок, первый коммутатор, дешифратор и делитель частоты, причем вход задания координат устройства соединен с информационным входом Ьлока памяти сумм направляющих косинусов, вход записи которого и управляющий вход первого коммутатора объединены и соединены с входом управления режимом устройства, первый и второй информационные входы первого коммутатора соединены с адресным входом устройства и первым выходом дешифратора соответственно, второй выход дешифратора соединен с информационными входами первого регистра сдвига, первый выход которого соединен с входом операции арифметике-логического блока, входы первого и второго операндов которого соединены с выходами первого регистра и блока памяти сумм направляющих косинусов со6006

О1вртствент-, пыхоч, арифм тико-логи- ческого блока соединен с информ цион- ными входами первого регистра, вход сброса которого объединен с с ыхрони1

зирующим входом второго регмстра и соединен с выходом делителя частоты, вход которого объединен с синхронизирующими входами первого регистQ ра и первого регистра сдвига и соединен с тактовым входом устройства, информационный вход и выход второго регистра соединены с входами данных устройства и первым входом дешифра5 соответственно, выход первого коммутатора соединен с адресным входом блока памяти сумм направляющих косинусов, отличающееся тем, что, с целью расширения класса

0 решаемых задач за счет возможности выполнения перспективных преобразований путем масштабирования координат X,Y в зависимости от значения координаты Z имитируемого объекта,

5 в него дополнительно введены блок памяти координат, второй коммутатор, второй и третий регистры сдвига и вы- читатель, причем выход первого регистра соединен с информационным входом

0 блока памяти когрнинат, выход кото рого соединен с информационным входом третьего регистра и первым информационным входом второго коммутатора, выход которого соединен с информационным входом регистра сдвига, выход которого соединен с входом уменьшаемого вычитателя, выход которого соединен с вторым информационным входом второго коммутатора, управляющий вход которого объединен с адресным входом блока памяти координат и соединен с вторым выходом первого регистра сдвига, выход переноса вычичягеля соединен с входом третьего регист

Ј ра сдвига, выход которого и выход блока памяти координат соединены с выходами результата устройства, выход делителя частоты соединен с входом записи- блока памяти координат и синхронизирующим входом третьего регистра, тактовый вход устройства соединен с синхронизирующими входами второго и третье о регистров- сдвига, вход данных устройства соединен с информационным входом второго ре-

5

0

0

5

гистра и вторым входом дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1986 |

|

SU1405051A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислителей, осуществляющих имитацию преобразования координат в трехмерном пространстве. Целью изобретения является расширение класса решаемых задач за счет возможности выполнение перспективных преобразований путем масштабирования координат X,Y в зависимости от значения координаты Z имитируемого объекта. Устройство содержит блок 1 памяти сумм направляющих косинусов, арифметико-логический блок 2, первый регистр 3, блок 4 памяти и координат, первый коммутатор 5, первый регистр 6 сдвига, дешифратор 7, второй регистр 8, третий регистр 9, второй коммутатор 10, генератор 11 импульсов, делитель 12 частоты, второй регистр 13 сдвига, вычитатель 14, третий регистр 15 сдвига, четвертый регистр 16. 1 ил.

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования координат | 1986 |

|

SU1405051A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-02-08—Подача