Изобретение относится к запомина ющим устройствам.

Известно запоминающее устройство с автономным контролем, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один из входов которого соединен с первым входом адресного блока памяти, блок управления, выходы которого подключены к управляющим входам ассоциативных блоков памяти 1 Недостатками этого устройства являются сложность и малая информационная емкость.

Наиболее близким техническим решением к изобретению является запоминающее устройство с автономным контролем, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один из входов которого соединен с первым входом адресного блока памяти, блок управле}ния, выходы которого подключены к управляющим входам ассоциативных блоков памяти, первый коммутатор, входы которого подключены соответственно к первому выходу блока дешифратора и к выходу адресного блока памяти, а виходы - к другим входам второго ассоциативного блока памяти, выходы которого- соединены со входом блока дешифратора и одним из входов второго коммутатора, другой вход которого подключен к выходу блока дешифраторов, а выход - ко входу адресного блока памяти 2.

Недостатком этого устройства явля10ется то, что при отказах разрядов ячеек адресного блока памяти необходимо запоминать во втором ассоциативном блоке памяти номера отказавших разрядов и значения соответствующих

15 им информационных сигналов, что приводит к увеличению объема второго , ассоциативного блока памяти, т.е. к усложнению устройства и снижению его информационной емкости.

20

Цель изобретения - упрощение устройства. ,

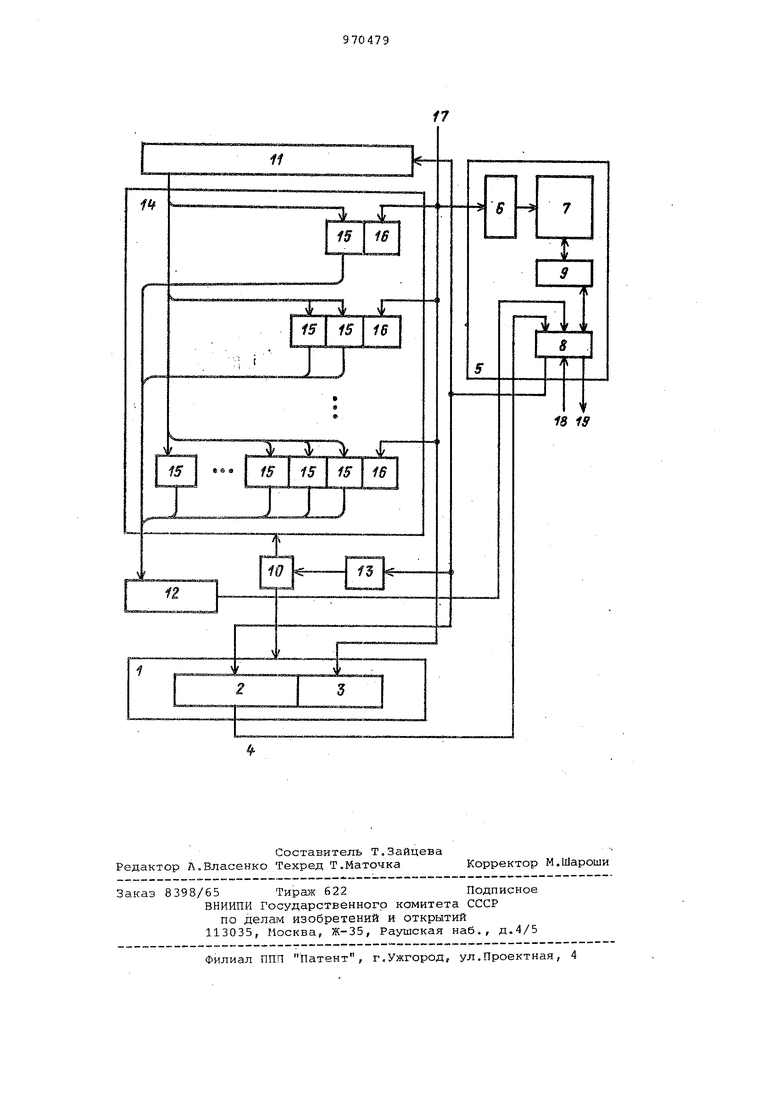

Поставленная цель достигается тем, что в запоминающее ycTpoiicTBO с автономным контролем, содержащее ад25ресный накопитель, усилители, регистр Слова, регистр адреса, дешифраторы, блок управления и ассоциативные накопители, управляющие которых соединены с выходами блока управли30 .ния, а адресные входы - с входами регистра адреса, выходы которого под ключены к адресным входам адресного накопителя, информационные входы и выходы которого соединены с одними и выходов и входов усилителей, другие входы и выходы которых подключены к одним из информационных выходов и входов регистра слова, первый управляющий вход которого соединен с выхо дом первого ассоциативного накопите ля, выходы второго ассоциативного на копителя подключены н входам дешифра тора , вход блока управления является управлянядам входом устройства, введены шифраторы и пороговый элемент, входы которых соединены с другими ин фо эмационными йыходами регистра елова и информационными входами первого ассоциативногЬ накопителя, причем вы Ходы шифраторов подключены к .информа ционным входам второго ассоциативног накопителя, выходы дешифраторов соединены с -вторым упраЕляющим входом регистра слова, а выход порогового элемента является управляющим выходом устройства. на приведена электрическая схема устройства. Устройство содержит первый ассоци тивный накопитель 1 с информационной :частью 2, адресной частью 3, выходов 4 и управляющим входом, 5 регистр 6 адреса, адресный наксйитель 7, ре гистр 8 слова, выполненный на триггерах со счетным входом, усилители 9 блок 10.управления, шифраторы 11, деишфраторы 12, пороговый элемент 13, второй ассоциативный накопитель 14 с признаковой частью 15 и адресной частью 16, предназначенных соответственно для записи номеров отказавших разрядов и адресов отказавших ячеек памяти адресного накопителя. На чертеже обозначены адресные 17 и .информационные 18 входы и информационные выходы 19 устройства, Устройство работает еледукнцим образом. Выявление разрядов, в которых записываемая информация не совпадает с характером отказа, производится ВО время записи информации в адресный накопитель 7. При этом адрес, поступакиций на вход 17, записываемся .в адресную часть 3 накопителя 1. 3aписываемое слово со входа 18 поступа в регистр 8 и заносится в накопитель 7 через усилители 9 и в информа ционную часть 2 накопителя 1. Затем производится считывание записанного слова (с-восстановлением информации) из накопителя 7 на регистр 8. Если в ячейке накопителя 7 по адресу, ycTctновленному на входе 17, нет отказов, или характер всех отказов совпадает с записываемой информацией, то во всех разрядах регистра 8 будет нуле-вой код. При зтом содержимое информа ционной части 2 накопителя 1, соот ветствующее гшресу на входе 17, и сам адрес из адресной части 3 стира ются. На вход 17 подается адрес следующей ячейки, аналогично производит-.ся запись нового слова. Если в ячейке накопителя 7 по адг ресу, установленному на входе 17, есть отказь, характер которых не совпадает с зсшисываемой информаци ей, то в соответствующих разрядах регистра В будет единичный код, Кол чество таких разрядов назовем крат ностью ошибки и обозначим через : ; Далее возможны два случая. ; Если (где п - количество разрядов слова, записываемого в адрерный накопитель 7), то на выходе порогового элемента 13 выдается еди1ничный сигнал., поступающий в блок 10, :который блокирует стирание содержи- ; мого в накопителе 1, соответствующего ,;адресу, установленному на входе 17, т.е. в накопителе 1 хранятся адрес ячейки накопителя 7, в которой имет- ютсяаотказы, и слово, предназначенное для записи в эту ячейку. Боли y, г- то на выходе эле-ч мента 13 выдается нулевой сигнал, поступакаций в блок 10. При этом бло1Й 10вырабатывает управлянлдий сигигш, :по которому содержимое информацион йой .части 2, соответствующее адресу |на входе 17, и сам адрес из адресно гчасти 3 накопителя 1, стираются. Од:новременно S адресную часть 16 накопителя 14 записывается адрес, посту;пающий на вход 17, а через шифраторь4 11в Признаковую часть 15 заносятся .номера отказавших разрядов накопите-; ля 7, характер отказов в которых не , совпадает с записываемой в них информацией. При считывании информации из запоминающего устройства по адресу, ус.тановленному на входе 17, происходит .одновременное обращение как к накопителю 7, так и к ассоциативным нагкопителям 1 и 14. Если адрес считы;Ваемого слова х;одер5жится в накопите-, ле 1, то передача информации в регистр 8 из накопителя 7 не произвол дится. При этом содержимое информационной части 2, соответствующее уста:новленному на входе 17 адресу, выдается на выход 4 и записывается в регистр В. После этого считываемое слово поступает на выход 19. Если адрес считываемого слова соцержится в накопителе 14, то в регистр 8 считывается информация из накОпителя 7 через усилители 9. Затем содержимое признаковой части 15 на;копителя 14, соответствующее адресу на входе 17, передается в дешифратор ры 12. При этом на выходах дешифраторов 12 формируется единичный код в тех разрядах, характер отказов в к6 TopLix не совпадаетс записываемой в них информацией. Этот код поступает на вход регистра 8 и инвертирует соответствунлцие разряды. После этого на выход 19 поступает неискаженное слово. При отсутствии в накопителях 14 и 1 адреса, поданного на вход 17, производится считывание э регистр -8 .информгщии из накопителя 7 через усЦ лители 9 с последующей шздачей на вы ход 19 устройства. В предлагаемом устройствге сокращается объем памяти ассоциативного накопителя. Необходимый объем признг ковой части накопителя более чем в д&а раза меньше, чем в известном. Таким образом, технике-экономическое преимущество предлагаемого устройства заключается в его упрощеНИИ по сравнению с известным. Формула изобретения Запоминающее устройство с автоном ным контролем, содержащее адресный накопитель, усилители, регистр слова регистр адреса, дешифраторы, блок yi .равления и ассоциативные накопители .управляющие входы которых соединены с выходами блока управления, а адрес ные входы - с входами регистра гщрегса, выходы которого подключены к адрес1Шм входам адресного накопителя, информационные входы и выходы которого соединены с одними и-з выходов и входов усилителей, другие входы и обходы которых подключены к одним из информационных выходов и входов регистра слова, перВЕ1й управляющий вхсщ которого соединен с выходом первого ассоциативного накопителя, выходы второго ассоциативного накопителя подключены к входам доиифратора, блока управления является управлявощй входом устройства, отличаю Щ е е с я тем, что, с целыо упрощения, в него введены шифраторы и поро говый элемент, входфл которых соеди;нены с другими информгщнонньо н выходами регистра слова и информгщионными входами первого ассоциативного накопителя, причем выходы шифраторов по«дкяючены к информационным входам второго ассоциативного накопителя,, выходы дешифраторов соединены с вторым управлятцим входом регистра слова, а выход порогового элемента является управляквдим выходсм устройства. Источники информации, принятые во внимание при экспертизе 1.Автогюкое свидетельство СССР 529490, кл. G И С 29/00, 1976. 2.Авторское свидетельство. СССР 744738, кл. G 11 С 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-20—Подача