Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и диагностики цифровых блоков радиоэлектронной аппаратуры.

Целью изобретения является расширение функциональных возможностей устройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу.

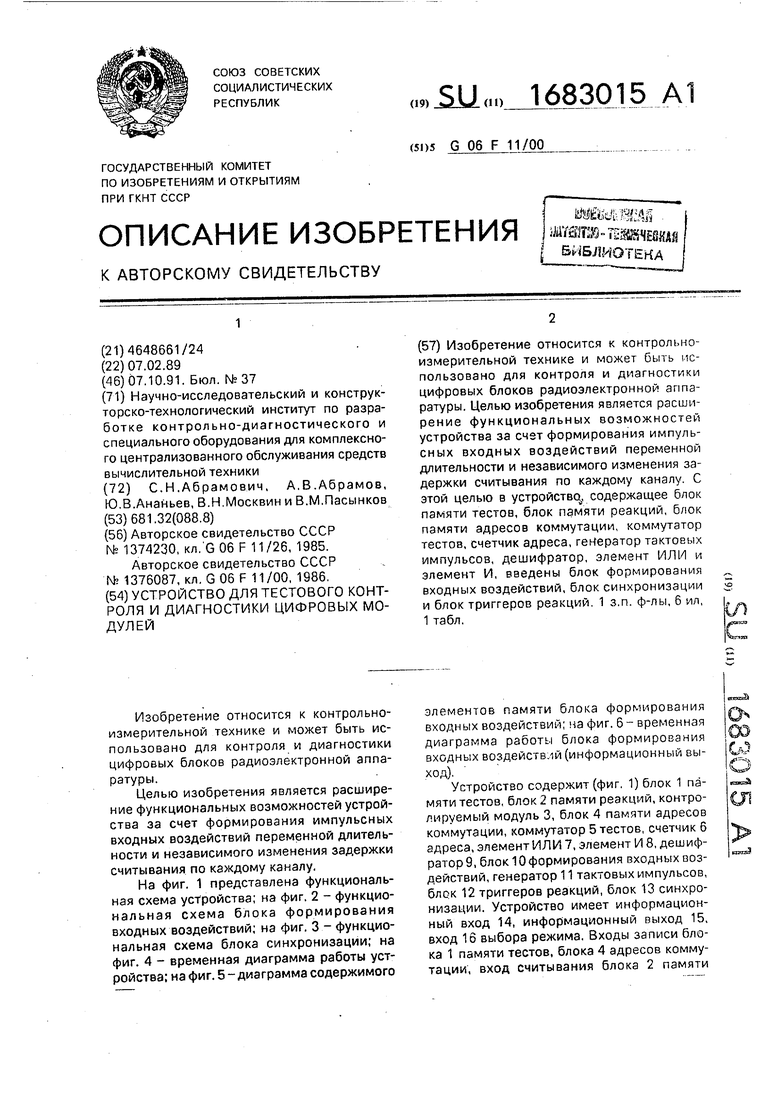

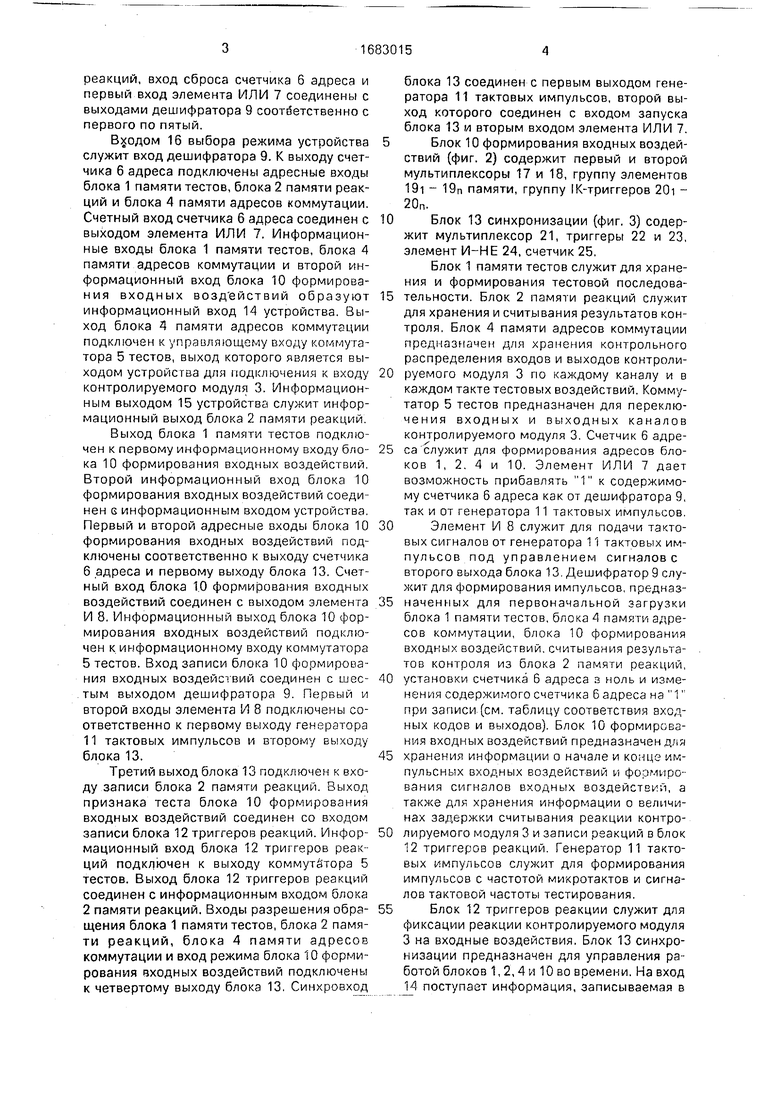

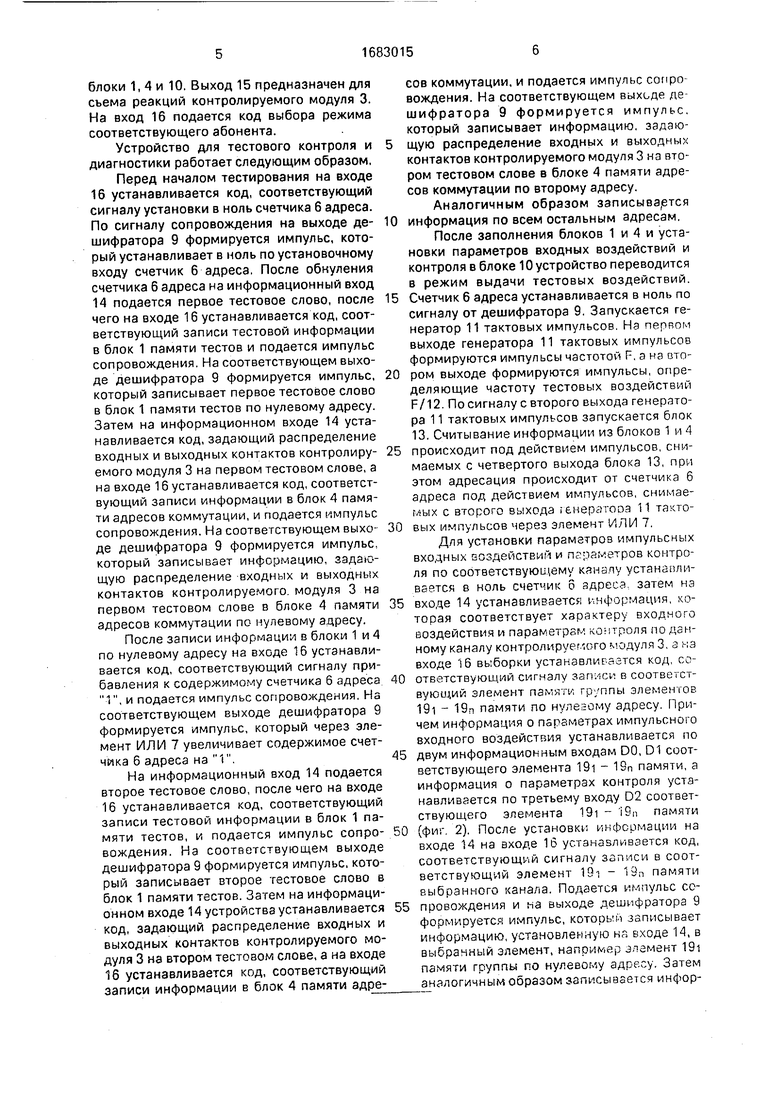

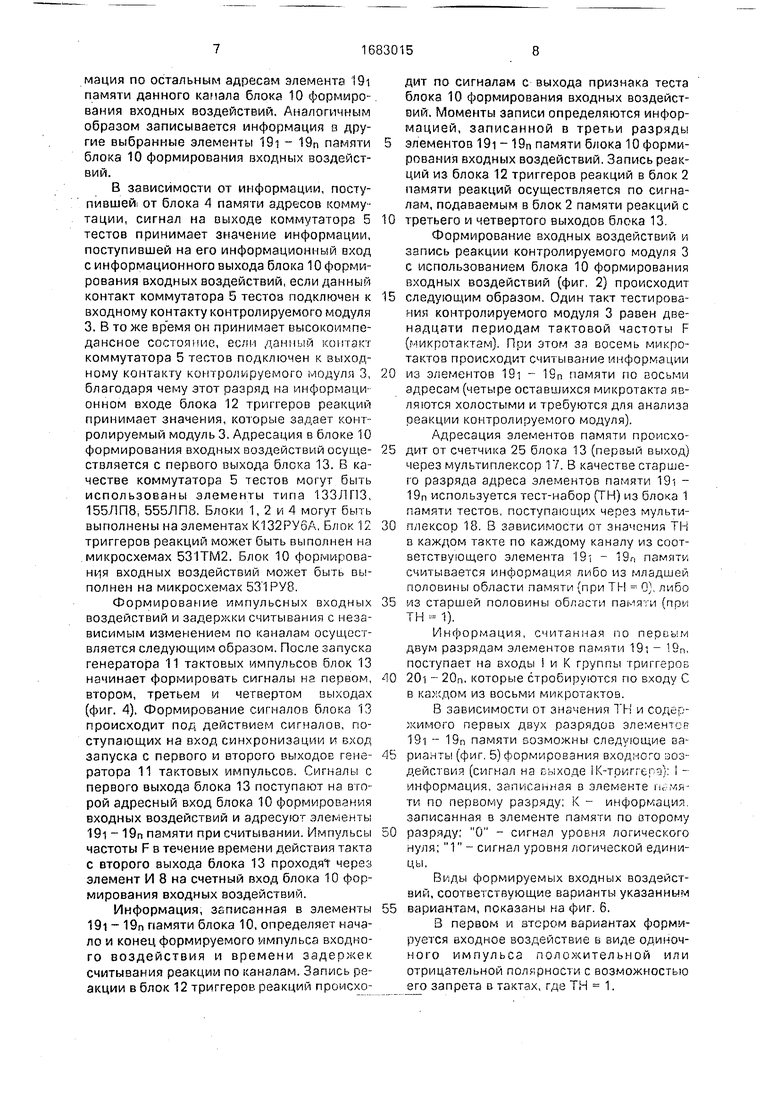

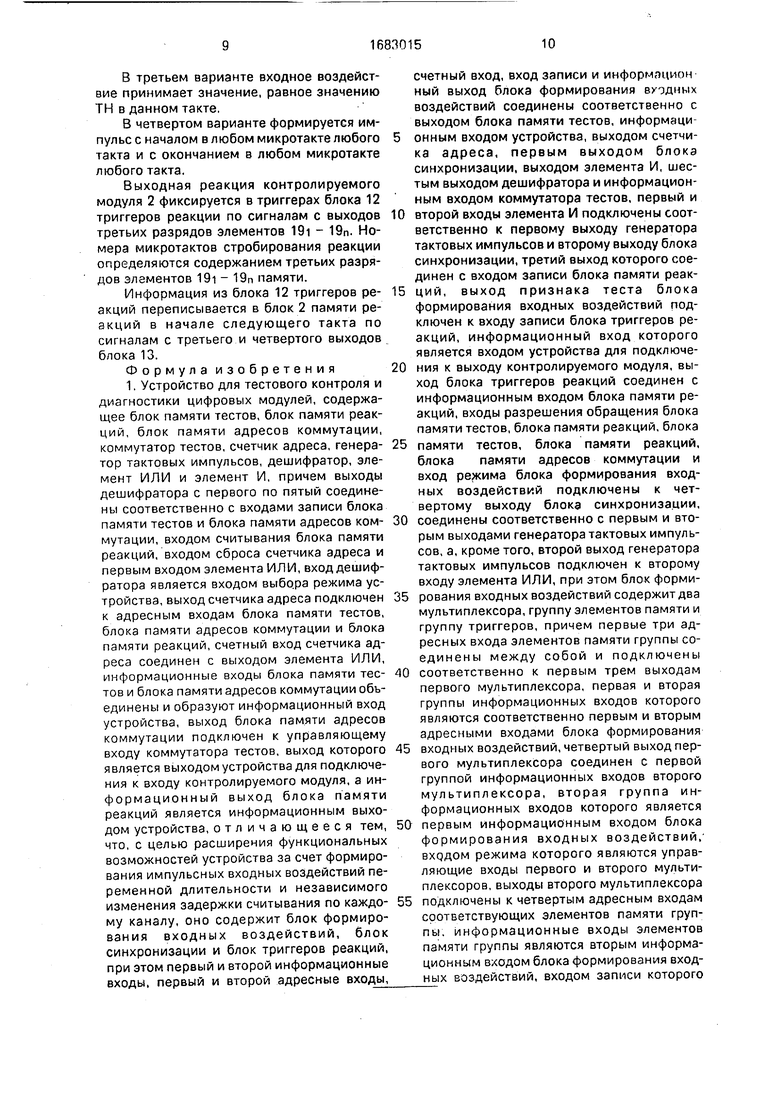

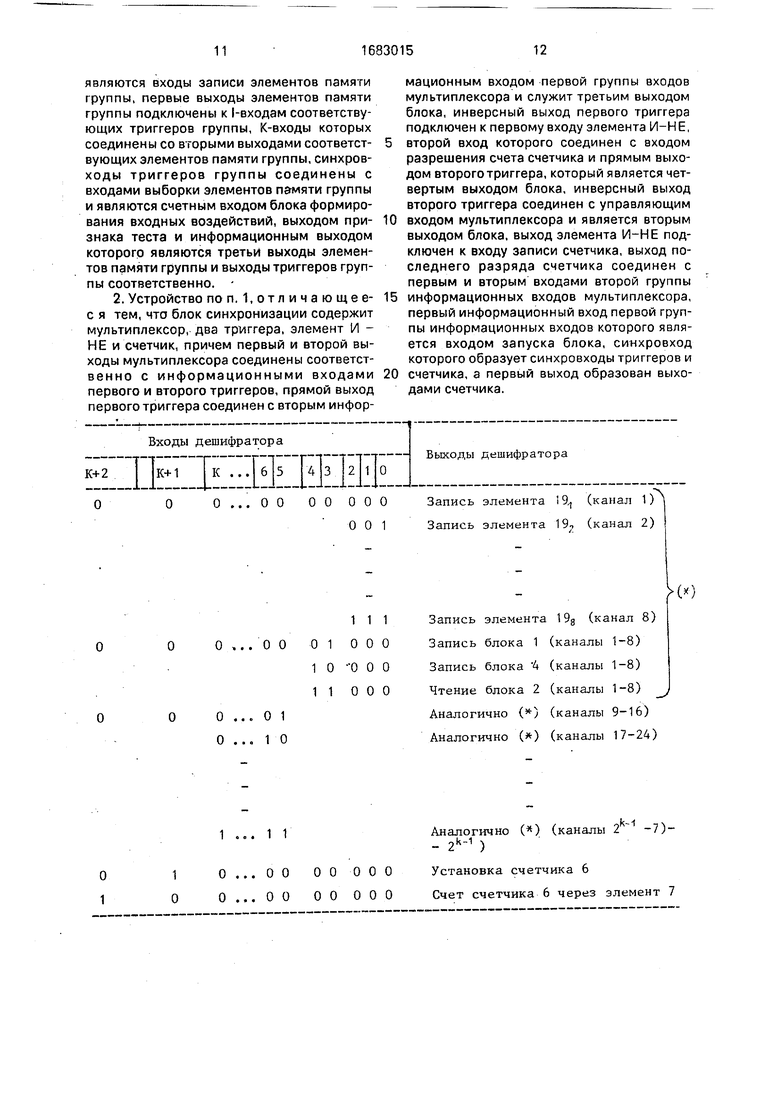

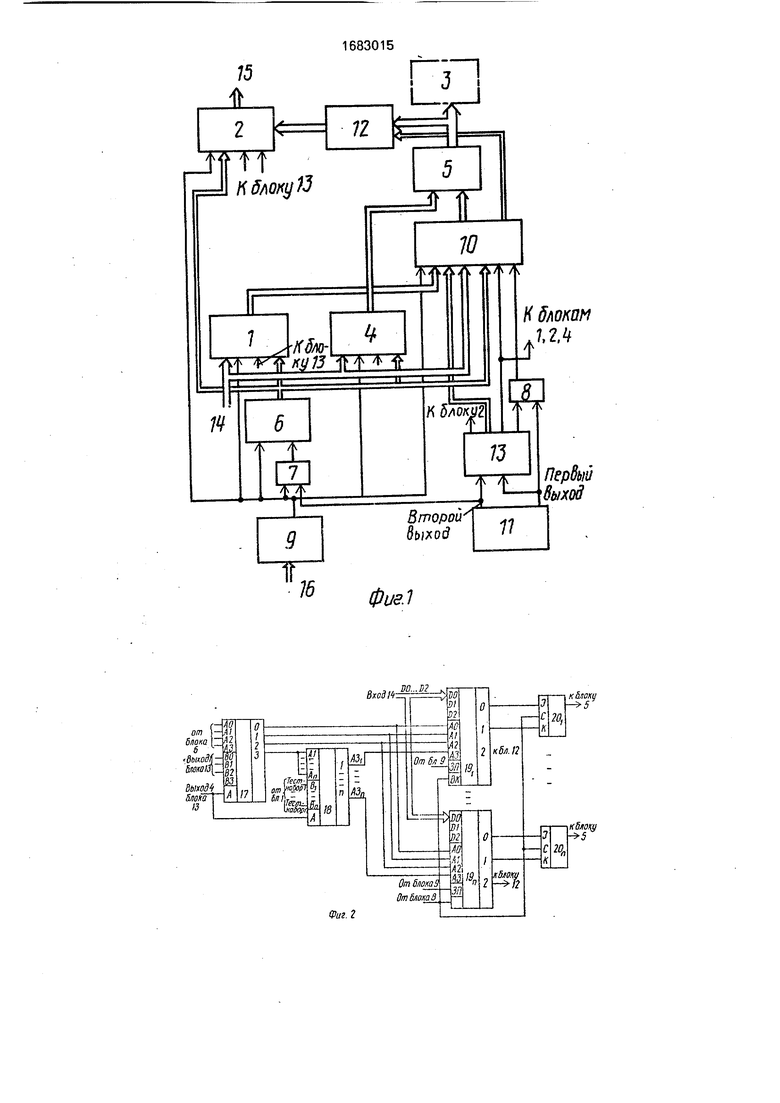

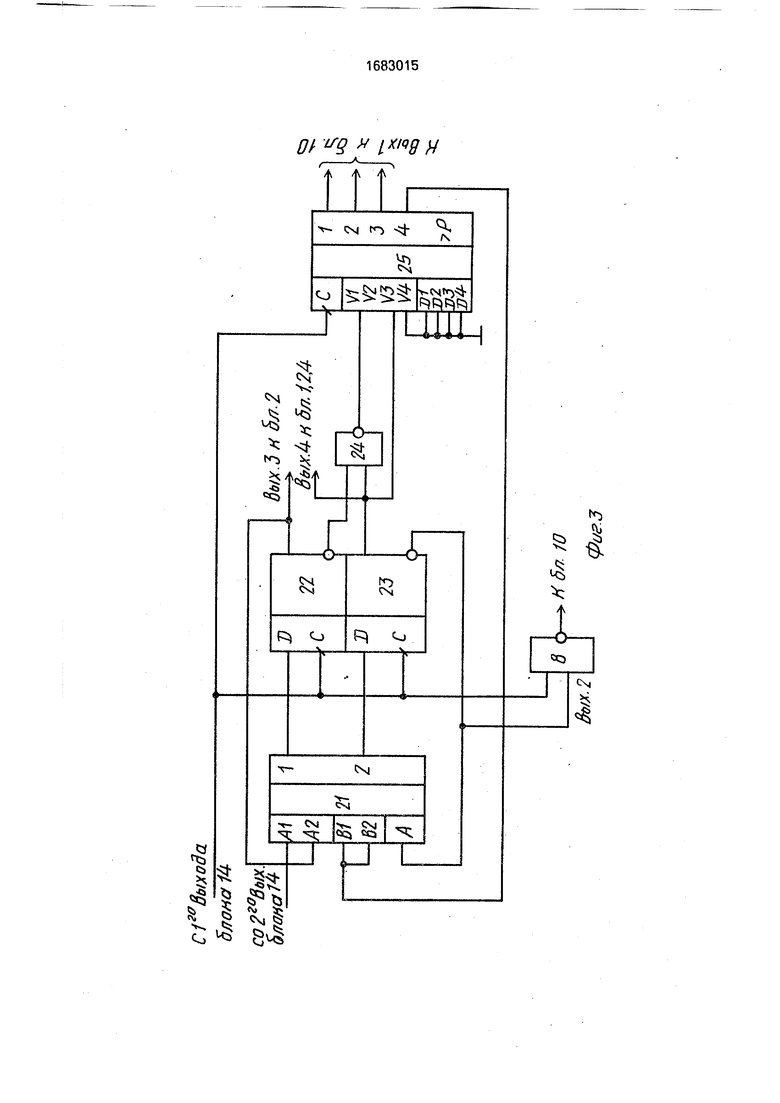

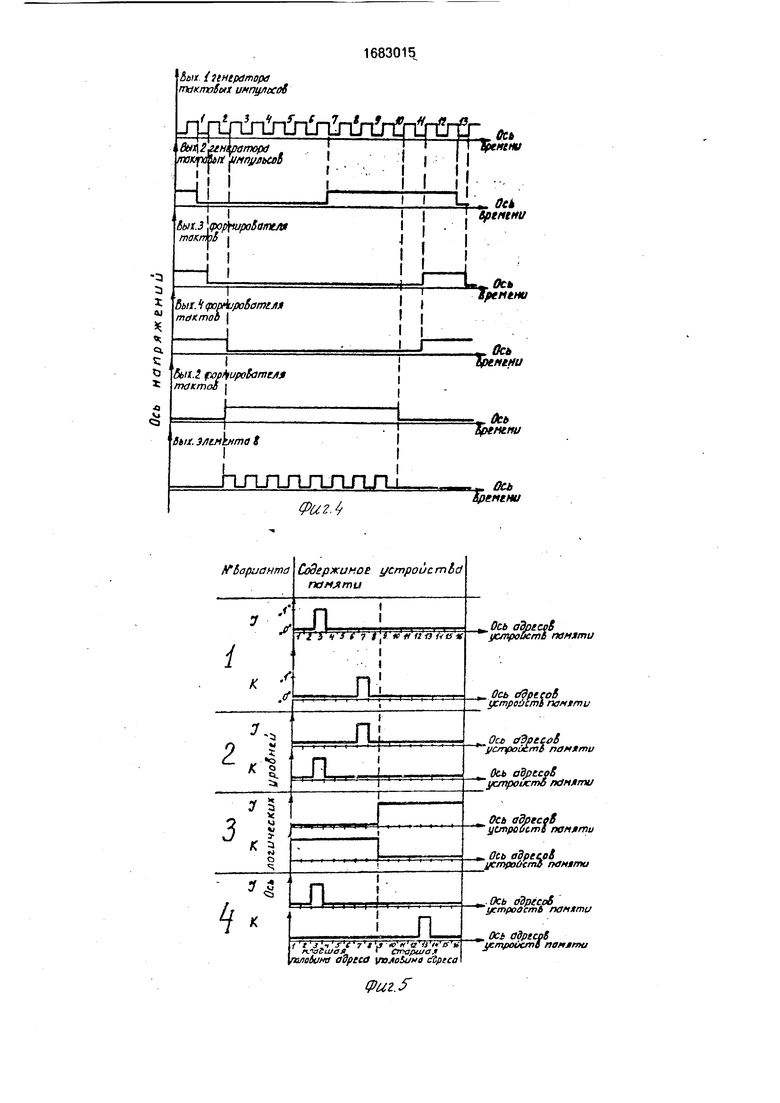

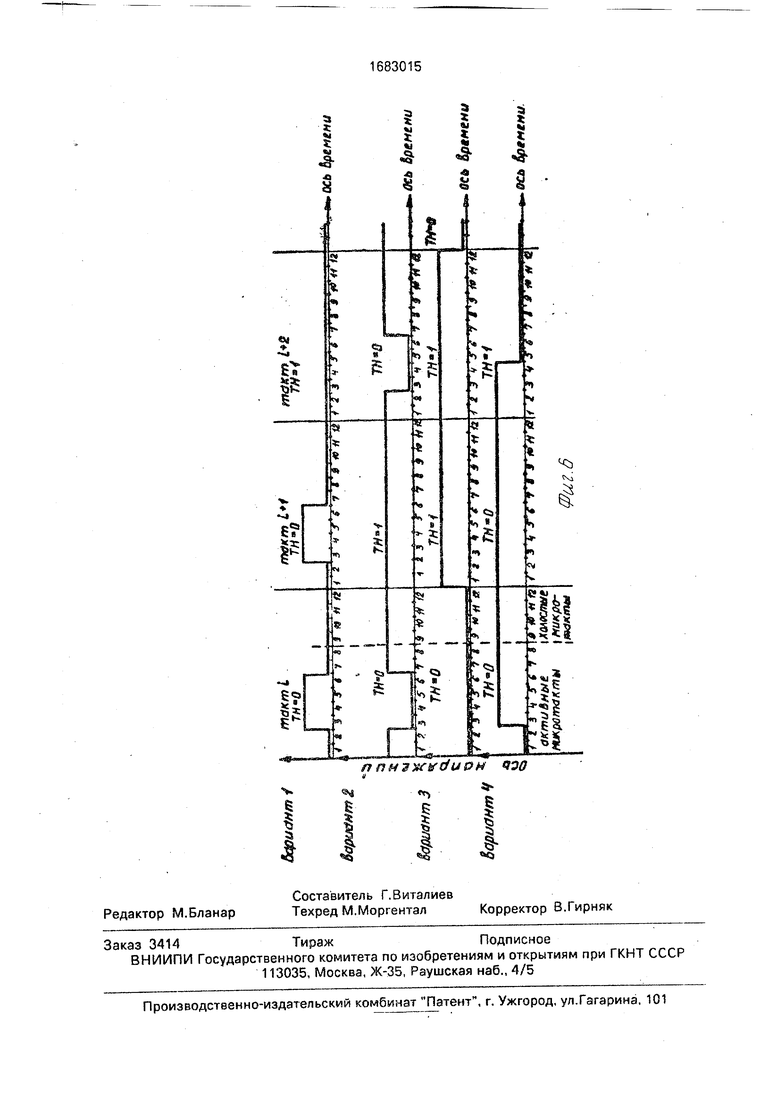

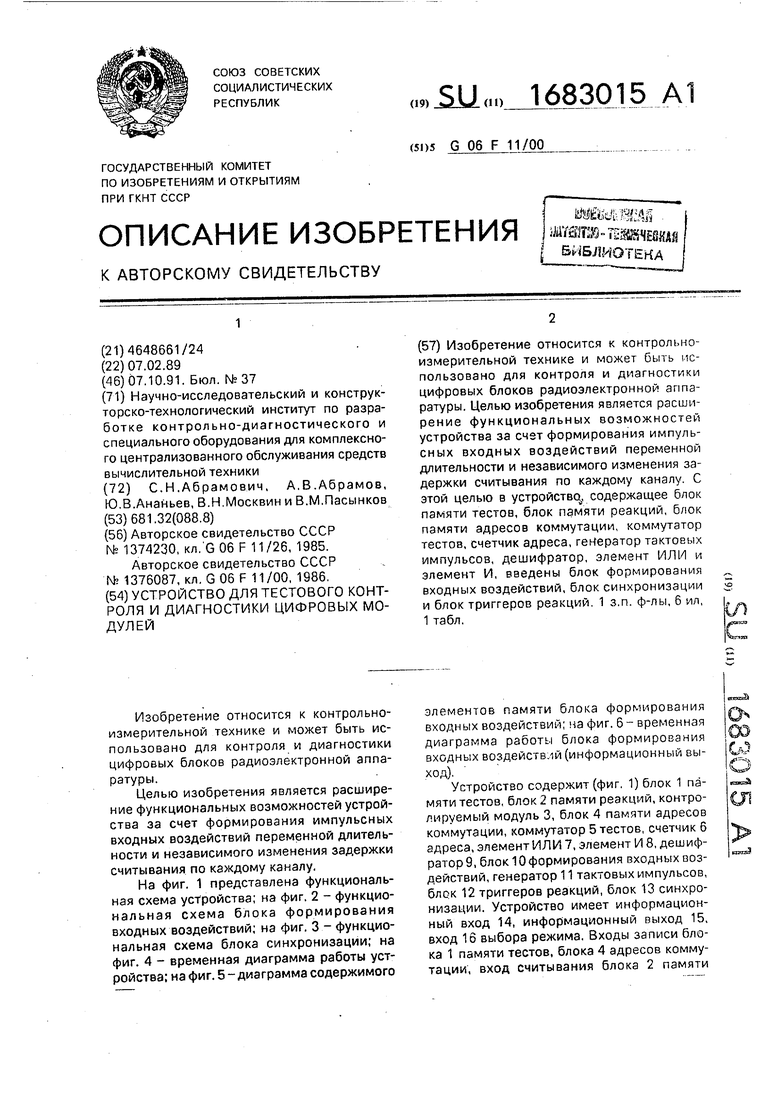

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема блока формирования входных воздействий; на фиг. 3 - функциональная схема блока синхронизации; на фиг. 4 - временная диаграмма работы устройства; на фиг. 5 - диаграмма содержимого

элементов памяти блока формирования входных воздействий; на фиг. 6 - временная диаграмма работы блока формирования входных воздействий (информационный выход).

Устройство содержит (фиг. 1) блок 1 памяти тестов, блок 2 памяти реакций, контролируемый модуль 3, блок 4 памяти адресов коммутации, коммутатор 5 тестов, счетчик 6 адреса, элементИЛИ 7, элемент И 8, дешифратор 9, блок 10 формирования входных воздействий, генератор 11 тактовых импульсов, блок 12 триггеров реакций, блок 13 синхронизации. Устройство имеет информационный вход 14, информационный выход 15, вход 16 выбора режима. Входы записи блока 1 памяти тестов, блока 4 адресов коммутации, вход считывания блока 2 памяти

U5 D

реакций, вход сброса счетчика 6 адреса и первый вход элемента ИЛИ 7 соединены с выходами дешифратора 9 соотбетственно с первого по пятый.

Входом 16 выбора режима устройства служит вход дешифратора 9. К выходу счетчика 6 адреса подключены адресные входы блока 1 памяти тестов, блока 2 памяти реакций и блока 4 памяти адресов коммутации. Счетный вход счетчика 6 адреса соединен с выходом элемента ИЛИ 7, Информационные входы блока 1 памяти тестов, блока 4 памяти адресов коммутации и второй информационный вход блока 10 формирования входных воздействий образуют информационный вход 14 устройства. Выход блока 4 памяти адресов коммутации подключен к управляющему входу коммутатора 5 тестов, выход которого является выходом устройства для подключения к входу контролируемого модуля 3. Информационным выходом 15 устройства служит информационный выход блока 2 памяти реакций.

Выход блока 1 памяти тестов подключен к первому информационному входу блока 10 формирования входных воздействий. Второй информационный вход блока 10 формирования входных воздействий соединен с информационным входом устройства. Первый и второй адресные входы блока 10 формирования входных воздействий подключены соответственно к выходу счетчика 6 адреса и первому выходу блока 13. Счетный вход блока 10 формирования входных воздействий соединен с выходом элемента И 8. Информационный выход блока 10 формирования входных воздействий подключен к информационному входу коммутатора 5 тестов. Вход записи блока 10 формирования входных воздействий соединен с шестым выходом дешифратора 9. Первый и второй входы элемента И 8 подключены соответственно к первому выходу генератора 11 тактовых импульсов и второму выходу блока 13.

Третий выход блока 13 подключен к входу записи блока 2 памяти реакций. Выход признака теста блока 10 формирования входных воздействий соединен со входом записи блока 12 триггеров реакций. Информационный вход блока 12 триггеров реакций подключен к выходу коммута тора 5 тестов. Выход блока 12 триггеров реакций соединен с информационным входом блока 2 памяти реакций. Входы разрешения обращения блока 1 памяти тестов, блока 2 памяти реакций, блока 4 памяти адресов коммутации и вход режима блока 10 формирования входных воздействий подключены к четвертому выходу блока 13. Синхровход

блока 13 соединен с первым выходом генератора 11 тактовых импульсов, второй выход которого соединен с входом запуска блока 13 и вторым входом элемента ИЛИ 7.

Блок 10 формирования входных воздействий (фиг. 2) содержит первый и второй мультиплексоры 17 и 18, группу элементов 19i - 19п памяти, группу IK-триггеров 20i - 20П.

0 Блок 13 синхронизации (фиг. 3) содержит мультиплексор 21, триггеры 22 и 23, элемент И-НЕ 24, счетчик 25.

Блок 1 памяти тестов служит для хранения и формирования тестовой последова5 тельности. Блок 2 памяти реакций служит для хранения и считывания результатов контроля. Блок 4 памяти адресов коммутации предназначен для хранения контрольного распределения входов и выходов контроли0 руемого модуля 3 по каждому каналу и в каждом такте тестовых воздействий. Коммутатор 5 тестов предназначен для переключения входных и выходных каналов контролируемого модуля 3. Счетчик 6 адре5 са служит для формирования адресов блоков 1, 2. 4 и 10. Элемент ИЛИ 7 дает возможность прибавлять 1 к содержимому счетчика 6 адреса как от дешифратора 9, так и от генератора 11 тактовых импульсов

0Элемент И 8 служит для подачи тактовых сигналов от генератора 11 тактовых импульсов под управлением сигналов с второго выхода блока 13 Дешифратор 9 служит для формирования импульсов, предназ5 наченных для первоначальной загрузки блока 1 памяти тестов, блока 4 памяти адресов коммутации, блока 10 формирования входных воздействий, считывания результатов контроля из блока 2 памяти реакций,

0 установки счетчика 6 адреса з ноль и изменения содержимого счетчика 6 адреса ча 1 при записи (см. таблицу соответствия входных кодов и выходов). Блок 10 формирования входных воздействий предназначен для

5 хранения информации о начале и конце импульсных входных воздействий и формирования сигналов входных воздействий, а также для хранения информации о величинах задержки считывания реакции контро0 лируемого модуля 3 и записи реакций в блок 12 триггеров реакций. Генератор 11 тактовых импульсов служит для формирования импульсов с частотой микротактов и сигналов тактовой частоты тестирования.

5Блок 12 триггеров реакции служит для

фиксации реакции контролируемого модуля 3 на входные воздействия. Блок 13 синхронизации предназначен для управления работой блоков 1, 2,4 и 10 во времени. На вход 14 поступает информация, записываемая в

блоки 1, 4 и 10. Выход 15 предназначен для съема реакций контролируемого модуля 3. На вход 16 подается код выбора режима соответствующего абонента.

Устройство для тестового контроля и диагностики работает следующим образом,

Перед началом тестирования на входе 16 устанавливается код, соответствующий сигналу установки в ноль счетчика 6 адреса. По сигналу сопровождения на выходе дешифратора 9 формируется импульс, который устанавливает в ноль по установочному входу счетчик 6 адреса, После обнуления счетчика 6 адреса на информационный вход 14 подается первое тестовое слово, после чего на входе 16 устанавливается код, соответствующий записи тестовой информации в блок 1 памяти тестов и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который записывает первое тестовое слово в блок 1 памяти тестов по нулевому адресу. Затем на информационном входе 14 устанавливается код, задающий распределение входных и выходных контактов контролируемого модуля 3 на первом тестовом слове, а на входе 16 устанавливается код, соответствующий записи информации в блок 4 памяти адресов коммутации, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который записывает информацию, задающую распределение входных и выходных контактов контролируемого модуля 3 на первом тестовом слове в блоке 4 памяти адресов коммутации по нулевому адресу.

После записи информации в блоки 1 и 4 по нулевому адресу на входе 16 устанавливается код, соответствующий сигналу прибавления к содержимому счетчика 6 адреса 1, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который через элемент ИЛИ 7 увеличивает содержимое счетчика 6 адреса на 1.

На информационный вход 14 подается второе тестовое слово, после чего на входе 16 устанавливается код, соответствующий записи тестовой информации в блок 1 памяти тестов, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который записывает второе тестовое слово в блок 1 памяти тестов. Затем на информационном входе 14 устройства устанавливается код, задающий распределение входных и выходных контактов контролируемого модуля 3 на втором тестовом слове, а на входе 16 устанавливается код, соответствующий записи информации в блок 4 памяти адресов коммутации, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который записывает информацию, задающую распределение входных и выходных контактов контролируемого модуля 3 на втором тестовом слове в блоке 4 памяти адресов коммутации по второму адресу.

Аналогичным образом записывается

0 информация по всем остальным адресам.

После заполнения блоков 1 и 4 и установки параметров входных воздействий и контроля в блоке 10 устройство переводится в режим выдачи тестовых воздействий.

5 Счетчик 6 адреса устанавливается в ноль по сигналу от дешифратора 9. Запускается генератор 11 тактовых импульсов. На первом выходе генератора 11 тактовых импульсов формируются импульсы частотой F. а на вто0 ром выходе формируются импульсы, определяющие частоту тестовых воздействий F/12. По сигналу с второго выхода генератора 11 тактовых импульсов запускается блок 13. Считывание информации из блоков 1 и 4

5 происходит под действием импульсов, снимаемых с четвертого выхода блока 13, при этом адресация происходит от счетчика 6 адреса под действием импульсов, снимаемых с второго выхода ieneparooa 11 тачто0 вых импульсов через элемент ИЛИ 7.

Для установки параметров импульсных входных воздействий и п раметров контроля по соответствующему канапу устанавливается в ноль счетчик б адреса затем на

5 входе 14 устанавливается информация, которая соответствует характеру входного воздействия и параметрам комгроля по данному каналу контролируетюго мэдуля 3, а ;-:з входе 16 выборки устан.авлигазтся код, со0 ответствующий сигналу записи в соответствующий элемент памяти группы элементе. 19ч - 19п памяти по нулевому адресу. Причем информация о параметрах импульсного входного воздействия устанавливается по

5 двум информационным входам DO, D1 соответствующего элемента 19i - 19п памяти, а информация о параметрах контроля устанавливается по третьему входу D2 соответствующего эпемента 191 - i9n памяти

0 (фиг, 2). После установки информации на входе 14 на входе 16 устанавливается код, соответствующий сигналу записи в соответствующий элемент 19i - 19П памяти йыбранного канала. Подается импульс со5 провождения и на выходе дешифратора 9 формируется импульс, которым записывает информацию, установленную на входе 14, в выбранный элемент, например элемент 19i памяти группы по нулевому адресу. Затем аналогичным образом записывается информация по остальным адресам элемента 19i памяти данного капала блока 10 формиро-. вания входных воздействий. Аналогичным образом записывается информация в другие выбранные элементы 19i - 19П памяти блока 10 формирования входных воздействий.

В зависимости от информации, поступившей: от блока 4 памяти адресов коммутации, сигнал на выходе коммутатора 5 тестов принимает значение информации, поступившей на его информационный вход с информационного выхода блока 10 формирования входных воздействий, если данным контакт коммутатора 5 тестов подключен к входному контакту контролируемого модуля 3. В то же вр емя он принимает высокоимпе- дансное состояние, если данный контакт коммутатора 5 тестов подключен к выходному контакту контролируемого модуля 3, благодаря чему этот разряд на информационном входе блока 12 триггеров реакций принимает значения, которые задает контролируемый модуль 3. Адресация в блоке 10 формирования входных воздействий осуществляется с первого выхода блока 13. В качестве коммутатора 5 тестов могут быть использованы элементы типа 133ЛПЗ, 155ЛП8, 555ЛП8, Блоки 1, 2 и 4 могут быть выполнены на элементах К132РУ6А, Блок 12 триггеров реакций может быть выполнен на микросхемах 531ТМ2. Блок 10 формирования входных воздействий может быть выполнен на микросхемах 531РУ8.

Формирование импульсных входных воздействий и задержки считывания с независимым изменением по каналам осуществляется следующим образом. После запуска генератора 11 тактовых импульсов блок 13 начинает формировать сигналы на первом, втором, третьем и четвертом выходах (фиг. 4). Формирование сигналов блока 13 происходит под действием сигналов, поступающих на вход синхронизации и вход запуска с первого и второго выходов генератора 11 тактовых импульсов. Сигналы с первого выхода блока 13 поступают на второй адресный вход блока 10 формирования входных воздействий и адресуют элементы 19i - 19П памяти при считывании. Импульсы частоты F в течение времени действия такта с второго выхода блока 13 проходят через элемент И 8 на счетный вход блока 10 формирования входных воздействий.

Информация, записанная в элементы 19i - 19n памяти блока 10, определяет начало и конец формируемого импульса входного воздействия и времени задержек считывания реакции по каналам. Запись реакции в блок 12 триггеров реакций происходит по сигналам с выхода признака теста блока 10 формирования входных воздействий. Моменты записи определяются информацией, записанной в третьи разряды

элементов 19i - 19П памяти блока 10 формирования входных воздействий. Запись реакций из блока 12 триггеров реакций в блок 2 памяти реакций осуществляется по сигналам, подаваемым в блок 2 памяти реакций с

0 третьего и четвертого выходов блока 13.

Формирование входных воздействий и запись реакции контролируемого модуля 3 с использованием блока 10 формирования входных воздействий (фиг, 2) происходит

5 следующим образом. Один такт тестирования контролируемого модуля 3 равен двенадцати периодам тактовой частоты F (микротактам). При этом за восемь микротактов происходит считывание информации

0 из элементов 19i - 19П памяти по восьми адресам (четыре оставшихся микротакта являются холостыми и требуются для анализа реакции контролируемого модуля).

Адресация элементов памяти происхо5 дит от счетчика 25 блока 13 (первый выход) через мультиплексор 17. В качестве старшего разряда адреса элементов памяти 19i - 19П используется тест-набор (ТН) из блока 1 памяти тестов, поступающих через мульти0 плексор 18. В зависимости от значения ТН в каждом такте по каждому каналу из соответствующего элемента 19| - 19г, памяти считывается информация либо из младшей половины области памяти (при ТН 0), либо

5 из старшей половины области памяти (при ТН 1).

Информация, считанная по первым двум разрядам элементов памяти 19i - 19П, поступает на входы i и К группы триггеров

0 20i - 20n, которые стробируются по входу С в каждом из восьми микротактов.

В зависимости от значения ТН и содержимого первых двух разрядов элементов 19i - 19п памяти возможны следующие ва5 рианты (фиг, 5) формирования входного зоз- действия (сигнал на сыходе IK-триггерэ): i - информация, записанная в элементе нсмя- та по первому разряду; К - информация, записанная в элементе памяти по второму

0 разряду; О - сигнал уровня логического нуля; 1 - сигнал уровня логической единицы,

Виды формируемых входных воздействий, соответствующие варианты указанным

5 вариантам, показаны на фиг. 6.

3 первом и атером вариантах формируется входное воздействие ь виде одиночного импульса положительной или отрицательной полярности с возможностью его запрета в тактах, где ТН 1.

В третьем варианте входное воздействие принимает значение, равное значению ТН в данном такте,

В четвертом варианте формируется импульс с началом в любом микротакте любого такта и с окончанием в любом микротакте любого такта.

Выходная реакция контролируемого модуля 2 фиксируется в триггерах блока 12 триггеров реакции по сигналам с выходов третьих разрядов элементов 19i - 19n. Номера микротактов стробирования реакции определяются содержанием третьих разрядов элементов 19i - 19П памяти.

Информация из блока 12 триггеров реакций переписывается в блок 2 памяти реакций в начале следующего такта по сигналам с третьего и четвертого выходов блока 13.

Формула изобретения

1. Устройство для тестового контроля и диагностики цифровых модулей, содержащее блок памяти тестов, блок памяти реакций, блок памяти адресов коммутации, коммутатор тестов, счетчик адреса, генератор тактовых импульсов, дешифратор, элемент ИЛИ и элемент И, причем выходы дешифратора с первого по пятый соединены соответственно с входами записи блока памяти тестов и блока памяти адресов коммутации, входом считывания блока памяти реакций, входом сброса счетчика адреса и первым входом элемента ИЛИ, вход дешифратора является входом выбора режима устройства, выход счетчика адреса подключен к адресным входам блока памяти тестов, блока памяти адресов коммутации и блока памяти реакций, счетный вход счетчика адреса соединен с выходом элемента ИЛИ, информационные входы блока памяти тестов и блока памяти адресов коммутации обь- единены и образуют информационный вход устройства, выход блока памяти адресов коммутации подключен к управляющему входу коммутатора тестов, выход которого является выходом устройства для подключения к входу контролируемого модуля, а информационный выход блока памяти реакций является информационным выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу, оно содержит блок формирования входных воздействий, блок синхронизации и блок триггеров реакций, при этом первый и второй информационные входы, первый и второй адресные входы,

счетный вход, вход записи и информационный выход блока формирования входных воздействий соединены соответственно с выходом блока памяти тестов, информационным входом устройства, выходом счетчика адреса, первым выходом блока синхронизации, выходом элемента И, шестым выходом дешифратора и информационным входом коммутатора тестов, первый и

0 второй входы элемента И подключены соответственно к первому выходу генератора тактовых импульсов и второму выходу блока синхронизации, третий выход которого соединен с входом записи блока памяти реак5 ций, выход признака теста блока формирования входных воздействий подключен к входу записи блока триггеров реакций, информационный вход которого является входом устройства для подключе0 ния к выходу контролируемого модуля, выход блока триггеров реакций соединен с информационным входом блока памяти реакций, входы разрешения обращения блока памяти тестов, блока памяти реакций, блока

5 памяти тестов, блока памяти реакций, блока памяти адресов коммутации и вход режима блока формирования входных воздействий подключены к четвертому выходу блока синхронизации,

0 соединены соответственно с первым и вторым выходами генератора тактовых импульсов, а, кроме того, второй выход генератора тактовых импульсов подключен к второму входу элемента ИЛИ, при этом блок форми5 рования входных воздействий содержит два мультиплексора, группу элементов памяти и группу триггеров, причем первые три адресных входа элементов памяти группы соединены между собой и подключены

0 соответственно к первым трем выходам первого мультиплексора, первая и вторая группы информационных входов которого являются соответственно первым и вторым адресными входами блока формирования

5 входных воздействий, четвертый выход первого мультиплексора соединен с первой группой информационных входов второго мультиплексора, вторая группа информационных входов которого является

0 первым информационным входом блока формирования входных воздействий,1 вхддом режима которого являются управляющие входы первого и второго мультиплексоров, выходы второго мультиплексора

5 подключены к четвертым адресным входам соответствующих элементов памяти группы, информационные входы элементов памяти группы являются вторым информационным входом блока формирования входных воздействий, входом записи которого

являются входы записи элементов памяти группы, первые выходы элементов памяти группы подключены к 1-входам соответствующих триггеров группы, К-входы которых соединены со вторыми выходами соответствующих элементов памяти группы, синхров- ходы триггеров группы соединены с входами выборки элементов памяти группы и являются счетным входом блока формирования входных воздействий, выходом признака теста и информационным выходом которого являются третьи выходы элементов памяти группы и выходы триггеров группы соответственно. 2. Устройство поп. 1,отличающее- с я тем, что блок синхронизации содержит мультиплексор, два триггера, элемент И - НЕ и счетчик, причем первый и второй выходы мультиплексора соединены соответственно с информационными входами первого и второго триггеров, прямой выход первого триггера соединен с вторым информационным входом первой группы входов мультиплексора и служит третьим выходом блока, инверсный выход первого триггера подключен к первому входу элемента И-НЕ,

второй вход которого соединен с входом разрешения счета счетчика и прямым выходом второго триггера, который является четвертым выходом блока, инверсный выход второго триггера соединен с управляющим

входом мультиплексора и является вторым выходом блока, выход элемента И-НЕ подключен к входу записи счетчика, выход последнего разряда счетчика соединен с первым и вторым входами второй группы

информационных входов мультиплексора, первый информационный вход первой группы информационных входов которого является входом запуска блока, синхровход которого образует синхровходы триггеров и

счетчика, а первый выход образован выходами счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и диагностики цифровых блоков радиоэлектронной аппаратуры. Целью изобретения является расширение функциональных возможностей устройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу. С этой целью в устройство., содержащее блок памяти тестов, блок памяти реакций, блок памяти адресов коммутации, коммутатор тестов, счетчик адреса, генератор тактовых импульсов, дешифратор, элемент ИЛИ и элемент И, введены блок формирования входных воздействий, блок синхронизации и блок триггеров реакций. 1 з.п. ф-лы, 6 ил, 1 табл, rfonwa Чн-ям

Входы дешифратора

К+2 Т JK-M Тк ... J4J3

Выходы дешифратора

О0...00 00000Запись элемента 191 (канал 1 )

О 0 1Запись элемента 19, (канал 2)

1 1 1Запись элемента 198 (канал 8)

,.. О 0 01 000Запись блока 1 (каналы 1-8)

IО О О ОЗапись блока 4 (каналы 1-8)

II000Чтение блока 2 (каналы 1-8) ... О 1Аналогично () (каналы 9-16) ... 1 0Аналогично () (каналы 17-24)

О 1

1 О

О ... О О

о ... о о

00 000Установка счетчика 6

00 000Счет счетчика 6 через элемент 7

Выходы дешифратора

Аналогично () (каналы 2 -7)k-1

)

k tT

К блоку ft

K$№f УЪ кая и 14 ft

1

(Тест-. юУюМ1

18

tf блокам .UM Ji

Первый Выход

фие.1

Ы9Чг

DO...D2

KiUOXt

М

От 8л 9

кбл. П

ШЮ.

Щ VI VL

А;

А2

19„

й

кбмт

Ql-irg ixngн

t

N

а

1

§

3

«J

4

3

I

4

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1989-02-07—Подача