Далее рассмотрим управление запре-.,- первого элемента И второй группы,

выходы элементов И второй группы динены соответственно с информаци ными входами второго регистра, вы ды которого соединены с входами э мента ИЛИ-НЕ и соответственно с рыми входами элементов И первой г пы, выходы которых являются выход группы тактовых выходов устройств выход первого элемента И соединен входом разрешения записи первого гистра, отличающееся что, с целью расширения функционал ных возможностей за счет обеспече переменного периода выходных импул сов, в устройство введены третий э мент И, блок сравнения, третий регистр, группа элементов ИЛИ и вто рой дешифратор, первый инверсный в ход второго дешифратора соединен с вторым входом первого элемента И в рой группы, выход элемента задержк соединен с синхровходом триггера, выходы первого дешифратора с второ по n-й соединены соответственно с выми входами элементов ИЛИ группы, выходы которых соединены с первыми входами элементов И соответственно второго по n-й второй группы, втор входы которых соединены соответств но с инверсными выходами второго дешифратора, группа входов которог соединена с группой выходов третье го регистра, с первой группой вход блока сравнения, вторая группа вхо дов которого соединена с группой ходов первого регистра, выход перв элемента И соединен с входом разре ния записи третьего регистра, вход сброса в О которого соединен с

20

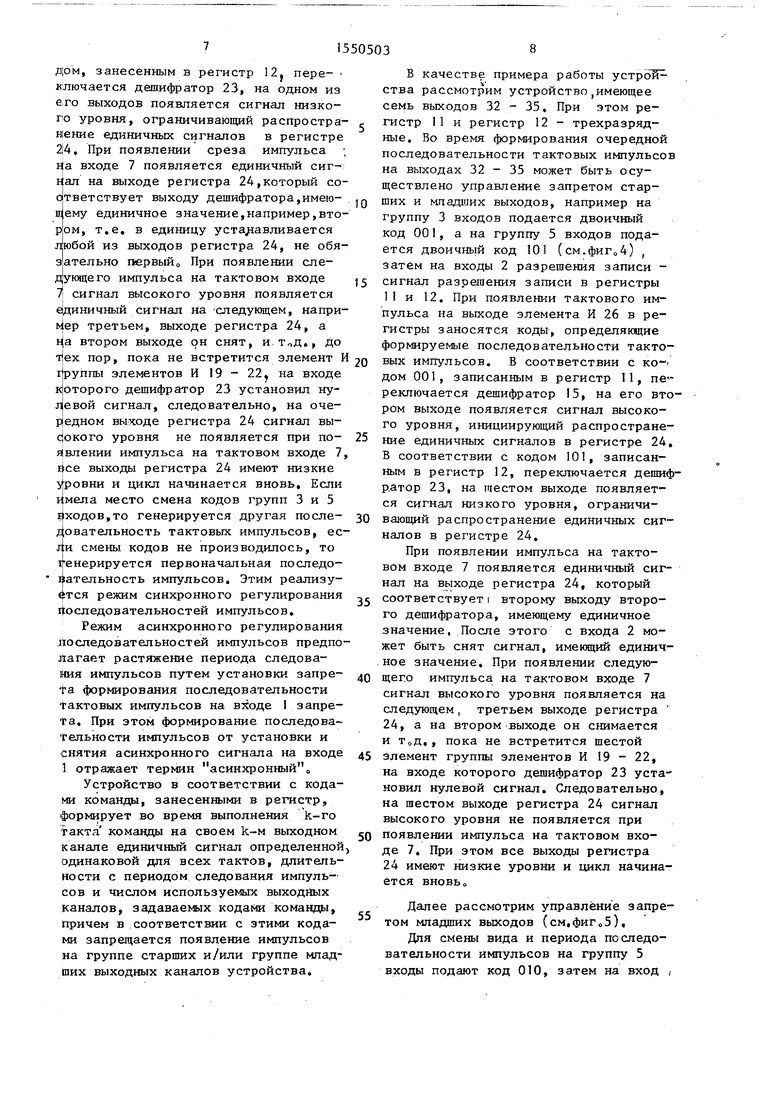

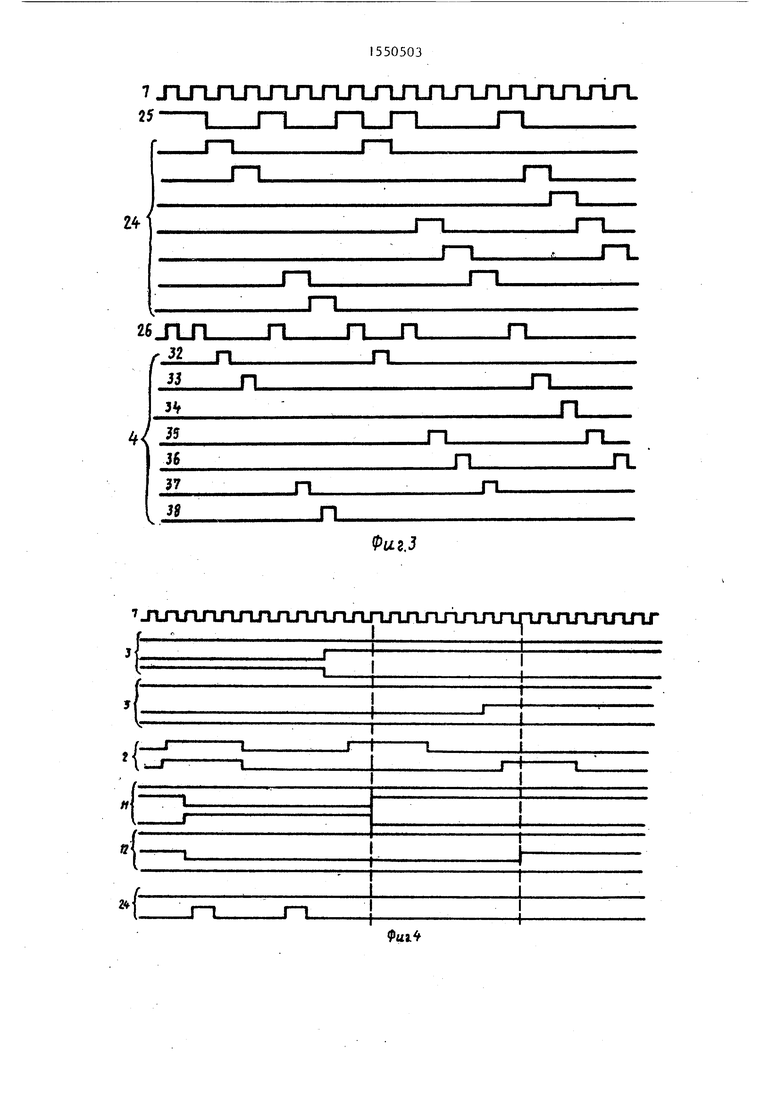

том старших выходных шин каналов (фиг.5)

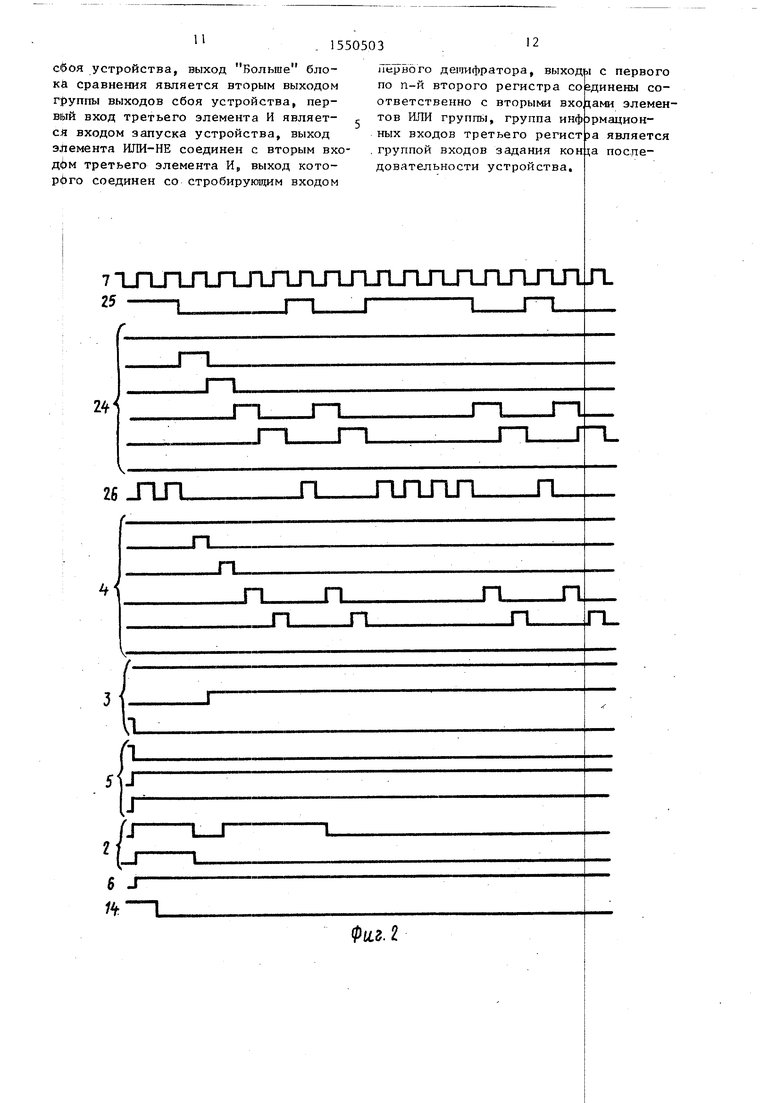

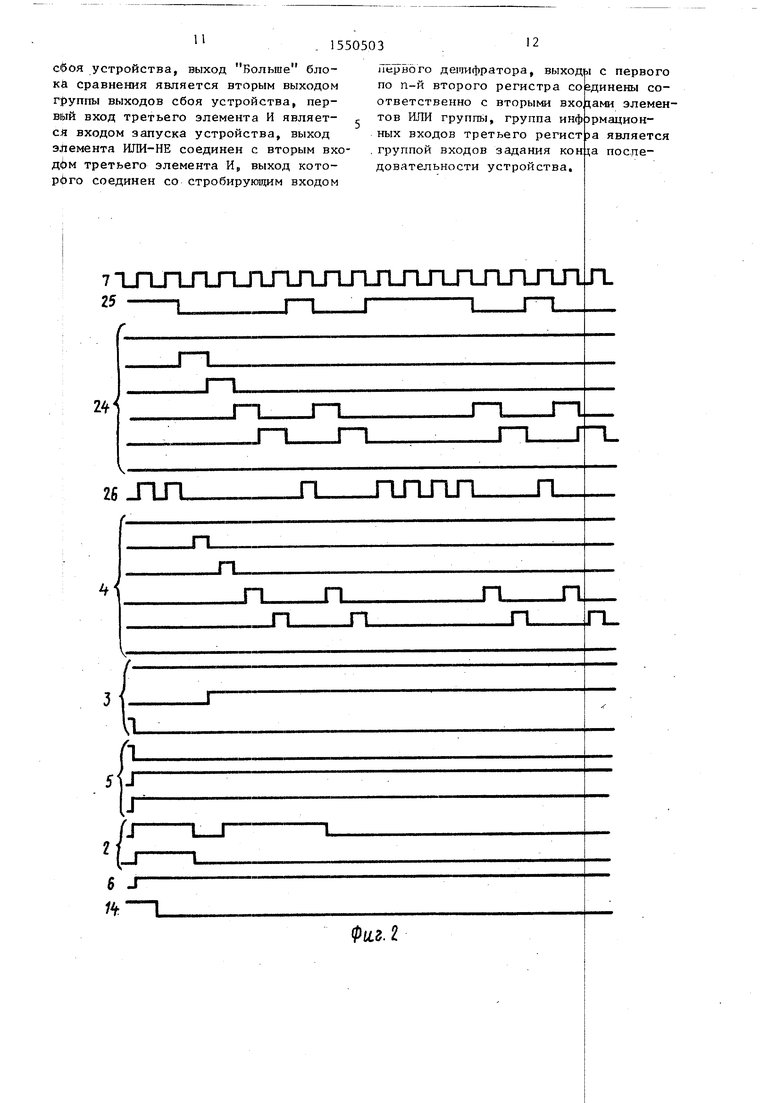

Для смены вида и периода последовательности импульсов на группу 3 входов подают код 111, затем на вход I - сигнал разрешения записи в регистр 12. При появлении тактового импульса на выходе элемента И 26 в регистр 12 заносится код 111, При этом переключается дешифратор 23, на его 25 шестом выходе снимается сигнал низкого уровня, ограничивающий распространение единичных сигналов в регистре 24, Так как младшие разряды регистра управление не затронуло, то при появ-зо лении импульса на шине тактовых импульсов 7 появляется единичный сигнал на третьем выходе регистра 24. При появлении соответствующих тактовых импульсов этот сигнал присутствует последовательно на четвертом, пятом, шестом и седьмом выходах регистра 24, затем на выходе элемента ИЛИ-НЕ, снова третьем выходе регистра 24 и т.д.

35

40

Формула изобретения

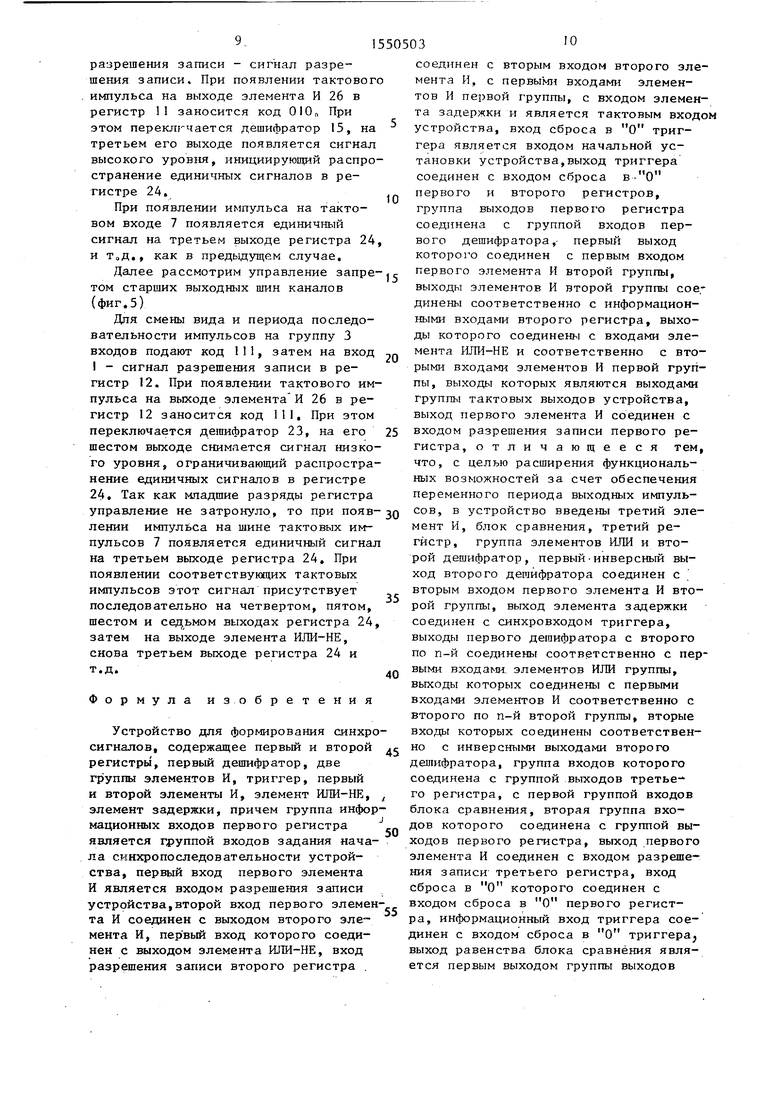

Устройство для формирования синхросигналов, содержащее первый и второй регистры, первый дешифратор, две группы элементов И, триггер, первый и второй элементы И, элемент ИЛИ-НЕ, t элемент задержки, причем группа информационных входов первого регистра является группой входов задания начала синхропоследовательности устройства, первый вход первого элемента И является входом разрешения записи

50

выходы элементов И второй группы со динены соответственно с информацион ными входами второго регистра, выхо ды которого соединены с входами эле мента ИЛИ-НЕ и соответственно с вт рыми входами элементов И первой гру пы, выходы которых являются выходам группы тактовых выходов устройства, выход первого элемента И соединен с входом разрешения записи первого ре гистра, отличающееся те что, с целью расширения функциональ ных возможностей за счет обеспечени переменного периода выходных импуль сов, в устройство введены третий эл мент И, блок сравнения, третий регистр, группа элементов ИЛИ и второй дешифратор, первый инверсный вы ход второго дешифратора соединен с вторым входом первого элемента И вт рой группы, выход элемента задержки соединен с синхровходом триггера, выходы первого дешифратора с второг по n-й соединены соответственно с п выми входами элементов ИЛИ группы, выходы которых соединены с первыми входами элементов И соответственно второго по n-й второй группы, вторы входы которых соединены соответстве но с инверсными выходами второго дешифратора, группа входов которого соединена с группой выходов третье- го регистра, с первой группой входо блока сравнения, вторая группа входов которого соединена с группой в ходов первого регистра, выход перво элемента И соединен с входом разреш ния записи третьего регистра, вход сброса в О которого соединен с

устройства,второй вход первого элемен- входом сброса в О первого регистта И соединен с выходом второго эле мента И, первый вход которого соединен с выходом элемента ИЛИ-НЕ, вход разрешения записи второго регистра

ра, информационный вход триггера со динен с входом сброса в О триггера выход равенства блока сравнения явля ется первым выходом группы выходов

0

5 о

5

0

0

выходы элементов И второй группы соединены соответственно с информационными входами второго регистра, выходы которого соединены с входами элемента ИЛИ-НЕ и соответственно с вторыми входами элементов И первой группы, выходы которых являются выходами группы тактовых выходов устройства, выход первого элемента И соединен с входом разрешения записи первого регистра, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения переменного периода выходных импульсов, в устройство введены третий элемент И, блок сравнения, третий регистр, группа элементов ИЛИ и второй дешифратор, первый инверсный выход второго дешифратора соединен с вторым входом первого элемента И второй группы, выход элемента задержки соединен с синхровходом триггера, выходы первого дешифратора с второго по n-й соединены соответственно с первыми входами элементов ИЛИ группы, выходы которых соединены с первыми входами элементов И соответственно с второго по n-й второй группы, вторые входы которых соединены соответственно с инверсными выходами второго дешифратора, группа входов которого соединена с группой выходов третье- го регистра, с первой группой входов блока сравнения, вторая группа входов которого соединена с группой выходов первого регистра, выход первого элемента И соединен с входом разрешения записи третьего регистра, вход сброса в О которого соединен с

ра, информационный вход триггера соединен с входом сброса в О триггера выход равенства блока сравнения является первым выходом группы выходов

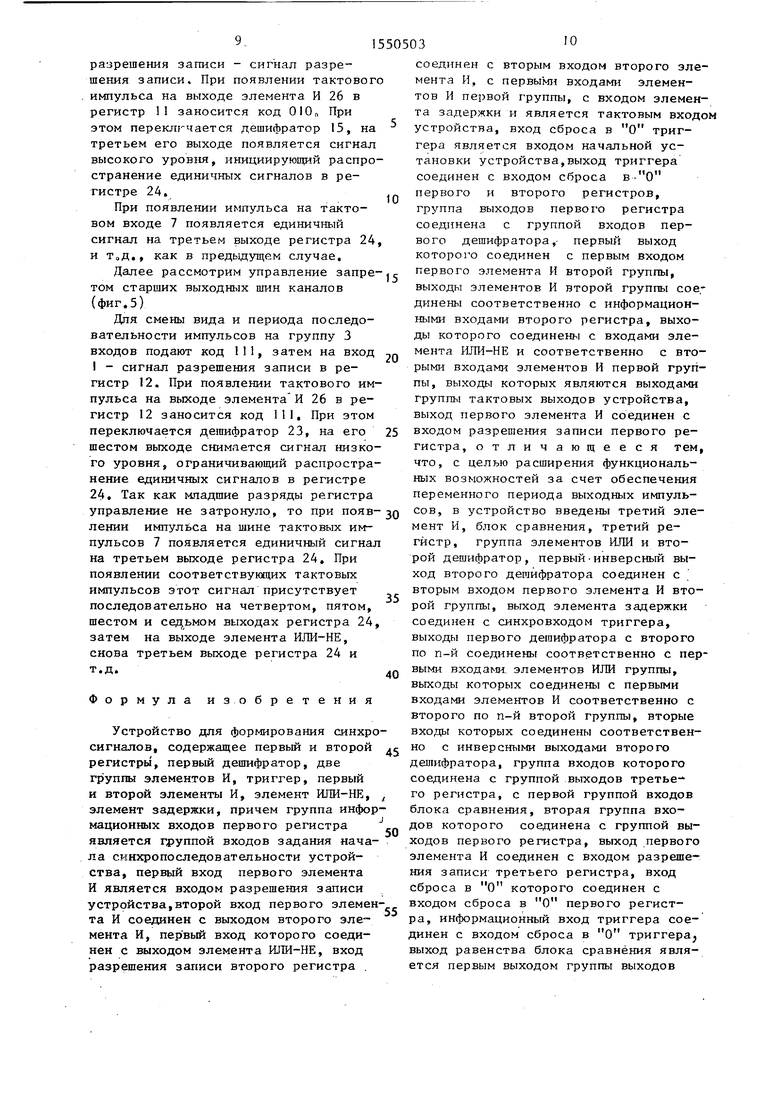

сбоя устройства, выход Больше блока сравнения является вторым выходом группы выходов сбоя устройства, первый вход третьего элемента И является входом запуска устройства, выход элемента ИЛИ-НЕ соединен с вторым вхо- дйм третьего элемента Ир выход которого соединен со стробирующим входом

первого дешифратора, выход по n-й второго регистра ее ответственно с вторыми тов ИЛИ группы, группа ных входов третьего регист группой входов задания довательности устройства.

входами инфэрмационконда

эа является

поспеi с первого единены со- элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для управления доступом к общей памяти | 1987 |

|

SU1418722A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

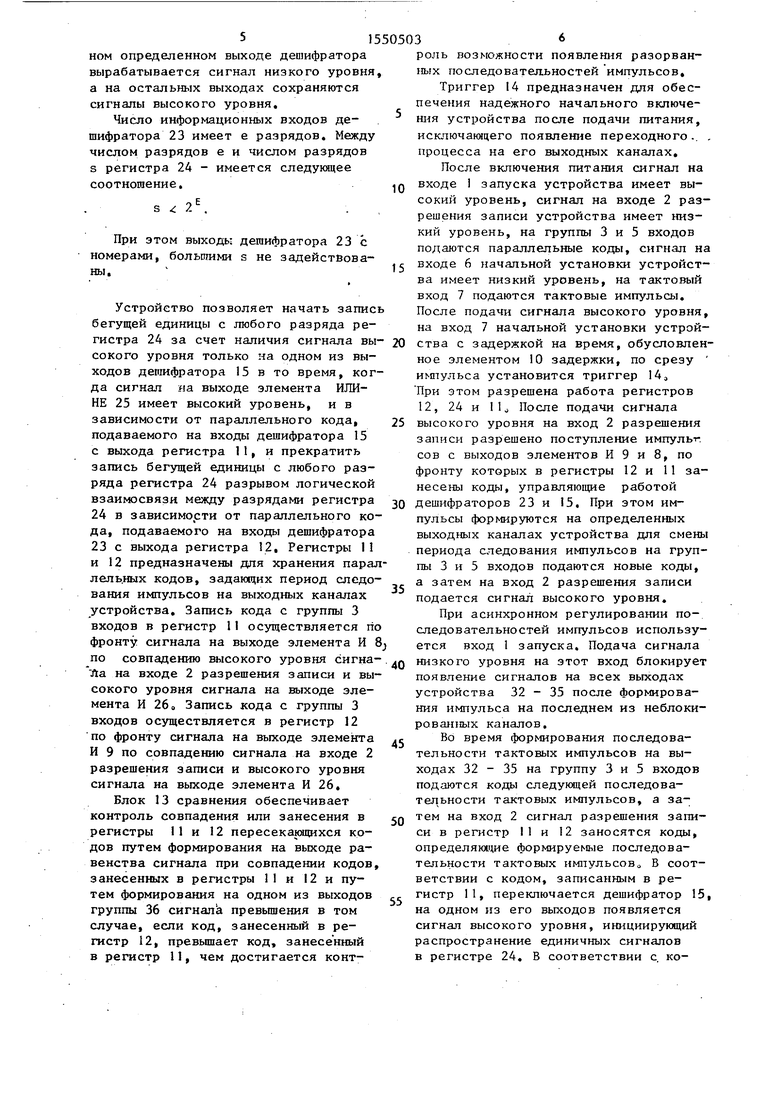

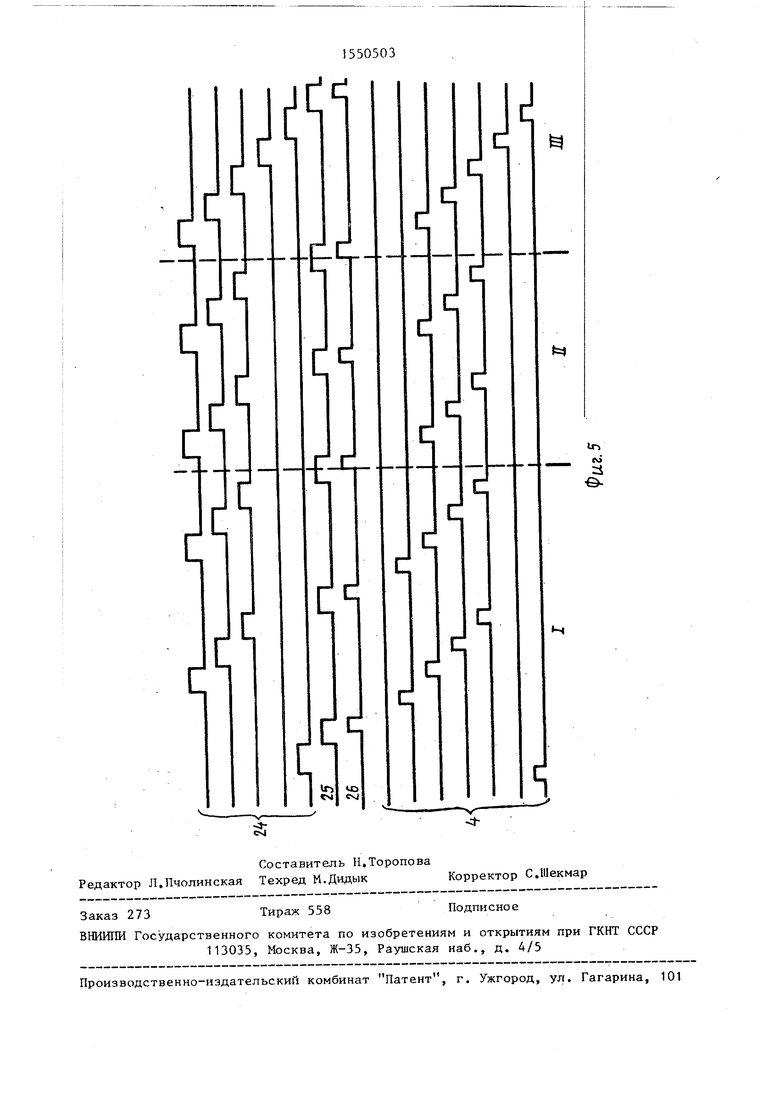

Изобретение относится к вычислительной технике и может быть использовано в качестве распрпеделителя импульсов. Отличительной особенностью устройства является то, что оно позволяет обеспечить как синхронное, так и асинхронное регулирование периода следования импульсов на выходных каналах устройства при одновременном запрете появления импульсов на группе старших и/или на группе младших выходных каналов устройства. Целью изобретения является расширение функциональных возможностей за счет обеспечения переменного периода выходных импульсов. Поставленная цель достигается введением группы элементов ИЛИ 16...18, элемента И 30, блока 13 сравнения, регистра 12, элемента И 9, дешифратора 23. 5 ил.

ФмЛ

7 JTTJTJTJTJTJTJTnLJarLT

п

ЛTL

п

33

W

35

36

37

TL

39

TL

7 JГLггfглJ J JlJтлLГlJ J

( t

гт

п.

п

TL

П

п.

аг.З

| Распределитель импульсов | 1980 |

|

SU919071A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-15—Публикация

1988-01-04—Подача