ся

ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1596333A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах приема дискретной информации. Цель изобретения - расширение области применения за счет формирования конца массива по адресному принципу. Устройство содержит накопитель 1, счетчик 2, регистр 3, блок сравнения 4, элементы И 5, 6, триггеры 7, 8, информационные входы 9, вход 10 обращения, вход записи-чтения 11, вход 12 синхронизации, выход 13 указывателя конца массива, информационные выходы 14. В устройстве сигнал "КМ" является однозначным сигналом, он формируется по адресному признаку, не связан с нулевым положением адресного счетчика, не требует дополнительного логического анализа. 2 ил.

0.

ел

00

ел

Изобретение относится к вычислительной технике и может быть использовано в системах приема и передачи дискретной информации.

Цель изобретения - расширение области применения за счет формирования конца массива по адресному принципу.

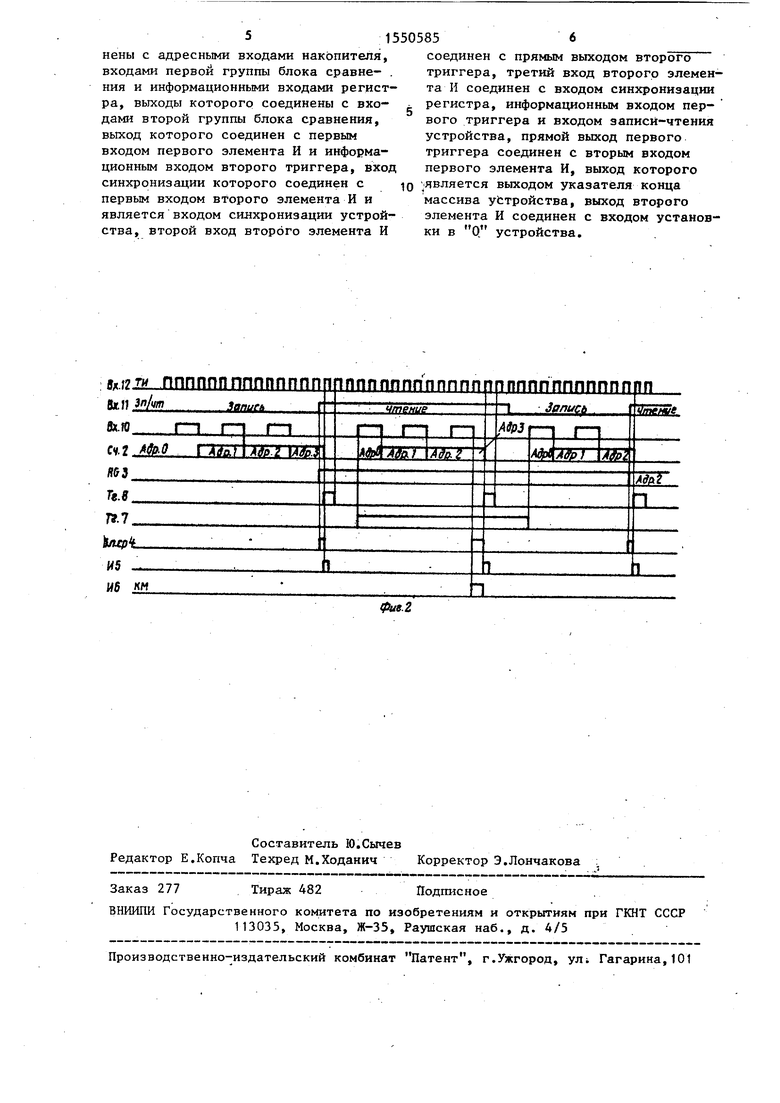

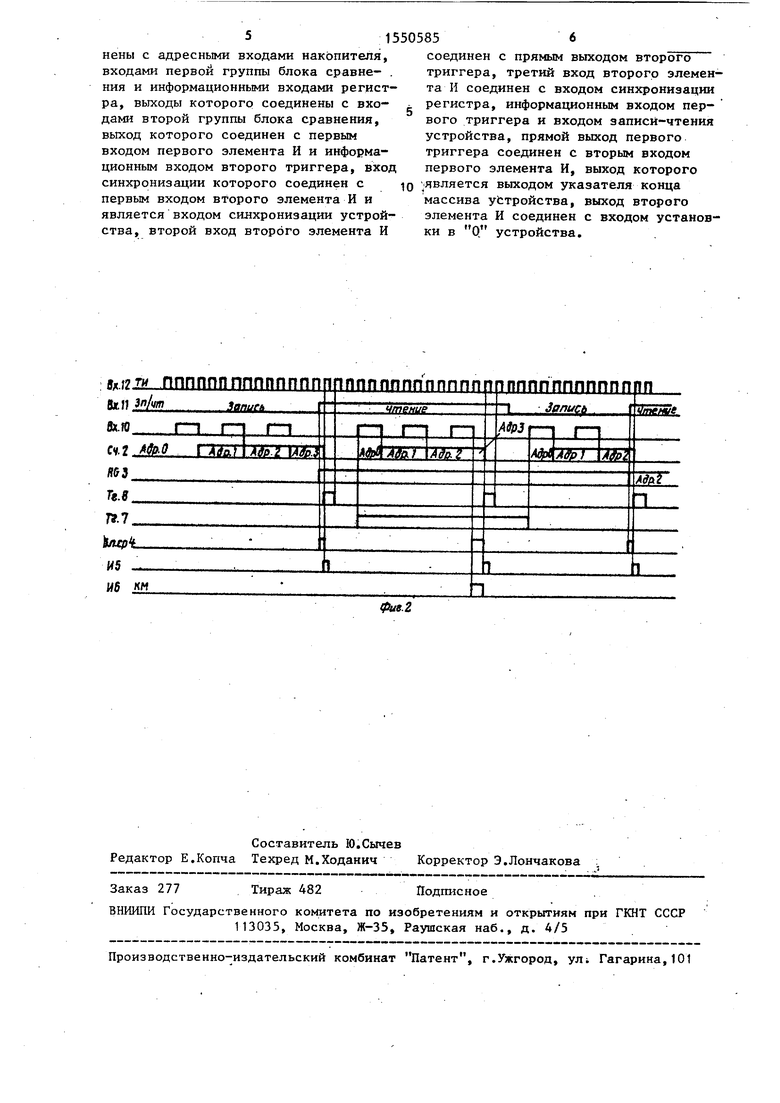

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - временные (диаграммы его работы.

Устройство содержит накопитель 1, счетчик 2, регистр 3, блок 4 сравнения, элементы И 5 и 6,, триггеры 7 ,и 8, информационные входы 9, вход 10 обращения, вход 11 записи-чтения, вход 12 синхронизации, выход 13 указателя конца массива, информационные выходы 14.

Устройство работает следующим об- ,разом.

В исходном состоянии счетчик 2, |регистр 3, триггеры 7 и 8 обнулены (цепи начальной установки не показаны) . Режим записи задается потенциальным сигналом низкого уровня по входу 11 устройства, при этом элемент И 5 закрыт. После этого по входу 9 подаются данные, а по входу 10 - импульсы сопровождения, обеспечивающие запись данных в накопитель по адресу, задаваемому счетчиком 2. 3апись информации произнюдится по ||фронту импульса на входе1 10, а счетчик 2 изменяет свое состояние по срезу этого импульса. По окончании записи устройство переводится в режим чтения путем подачи потенциального сигнала высокого уровня по входу 11 устройства. По фронту этого сигнала содержимое счетчика 2 - конечный адрес записанного массива - переписывается в регистр 3. Кроме того, этот сигнал подается на D-вход триггера 8 подготавливает к открыванию элемент И 5. После записи конечного адреса в регистр 3 коды на первых и вторых входах блока 4 сравнения совпадают и он формирует сигнал совпадения, который подается на D-вход триггера 7 и вход элемента И 6. Текущий тактовый импульс устанавливает в единичное состояние триггер 7, который открывает элемент И 5 и этот же тактовый импульс устанавливает счетчик 2 в нулевое состояние. После этого сигнал на выходе блока 4 сравнения снимается и триггер 7 устанавливается в нулевое положение очередным тактовым импульсом, тем самым закрывая элемент И 5. После установки

. режима чтения по входу 11 устройства внешнее устройство подает импульсы чтения по входу 10. Первый импульс по входу 10 устанавливает в единичное состояние триггер 8, который подгоQ тавливает к открыванию элемент И 6. Считываемые данные из накопителя 1 подаются на информационные выходы 14 устройства, а адреса ячеек накопителя задаются также счетчиком 2, ко5 торый аналогично изменяет свое состояние по срезу импульса чтения. При этом текущее состояние счетчика 2 непрерывно сравнивается с содержимым регистра 3 с помощью блока 4 сравQ нения. После считывания последнего слова массива коды счетчика 2 и регистра 3 совпадают и блок 4 формирует сигнал совпадения. Этот сигнал через элемент И 6 выдается на выход 13 уст5 ройства в виде импульса сигнала конец массива (КМ) и подается на D-вход триггера 7. Текущий тактовый импульс устанавливает триггер 7 в единичное состояние, и аналогично описанному тактовым импульсом с выхода элемента И 5 счетчик 2 устанавливается в исходное состояние. При этом снимается сигнал с выхода блока 4 сравнения и с выхода элемента И 6, а триггер 7 устанавливается в исход5 ное состояние. Устройство готово к выполнению повторного цикла чтения либо к циклу записи.

0

40

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, информационные входы которого являются одноименными входами устройства, входы обращения и записи-чтения накопителя являются соответствующими входами устройства, выходы накопителя - информационными выходами устройства,

счетчик, первый и второй триггеры, первый и второй элементы И, отличающееся тем, что, с целью расширения области применения устройства за счет формирования конца мас- сива по адресному принципу, в него введены регистр и блок сравнения, вход обращения устройства соединен с входами синхронизации первого триггера и счетчика, выходы которого соедийены с адресными входами накопителя, входами первой группы блока сравне- . ния и информационными входами регистра, выходы которого соединены с входами второй группы блока сравнения, выход которого соединен с первым входом первого элемента И и информационным входом второго триггера, вход синхронизации которого соединен с первым входом второго элемента И и является входом синхронизации устройства, второй вход второго элемента И

Составитель Ю.Сычев Редактор Е.Копча Техред М.Ходанич Корректор Э.Лончакова

Заказ 277

Тираж 482

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

соединен с прямым выходом второго триггера, третий вход второго элемента И соединен с входом синхронизации регистра, информационным входом первого триггера и входом записи-чтения устройства, прямой выход первого триггера соединен с вторым входом первого элемента И, выход которого является выходом указателя конца массива устройства, выход второго элемента И соединен с входом установки в Q устройства.

Подписное

| Буферное запоминающее устройство | 1984 |

|

SU1163359A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1988-02-01—Подача