ел ел

N5

т.

О5 OD

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения аналого-цифрового преобразователя с цифровой вычислительной машиной | 1983 |

|

SU1094038A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для сопряжения аналого-цифрового преобразователя с цифровой вычислительной машиной | 1983 |

|

SU1179308A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

Изобретение относится к вычислительной технике, в частности к средствам ввода измерительной информации в цифровые вычислительные машины. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения обслуживания многопараметрических событий, поступающих от АЦП. Устройство содержит промежуточные регистры 1, регистр данных 2, сумматор 3, вспомогательную память 4, адресные регистры 5, 9, память микрокоманд 8, регистр слова состояний 7, тактовый генератор 10, шинные формирователи 11, 12 и формирователь синхросигналов 13. Устройство позволяет сопрягать несколько аналого-цифровых преобразователей с цифровой вычислительной машиной. 6 ил., 1 табл.

фиг.

Изобретение относится к вычислительной технике, в частности к средствам ввода измерительной информации в цифровые вычислительные машины (ЦВМ).

Целью изобретения является расширение функциональных возможностей за счет обеспечения обслуживания многопараметрических событий, поступающих от группы АЦП.

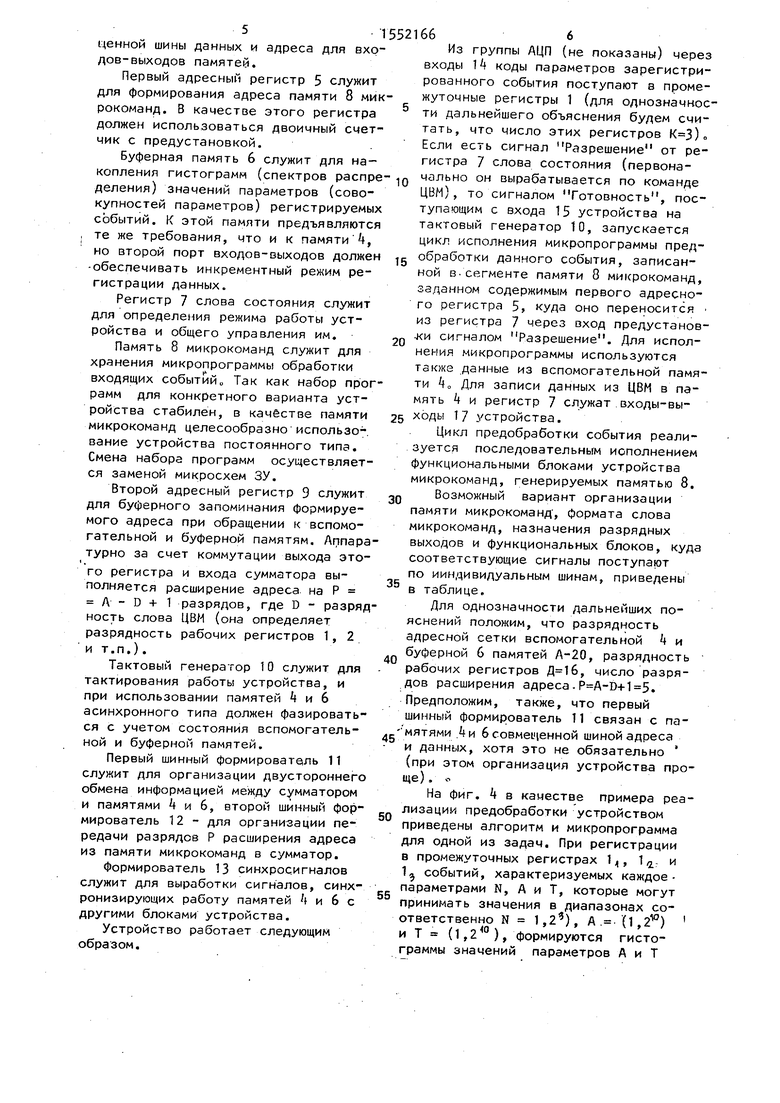

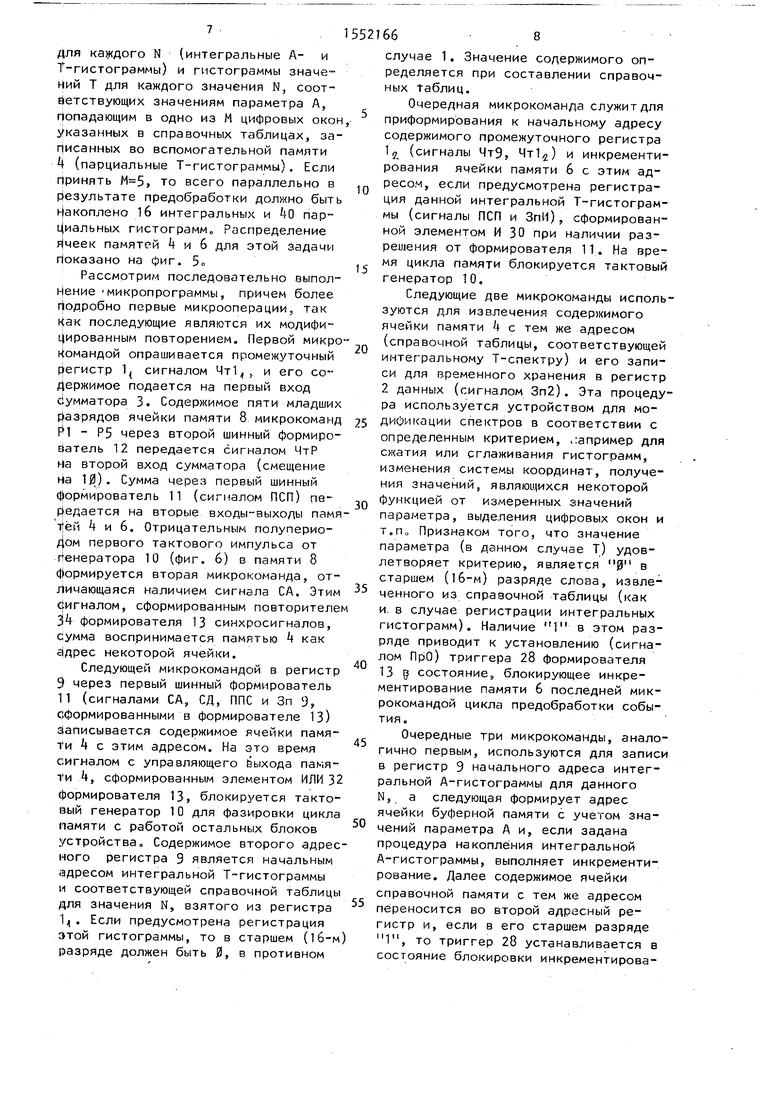

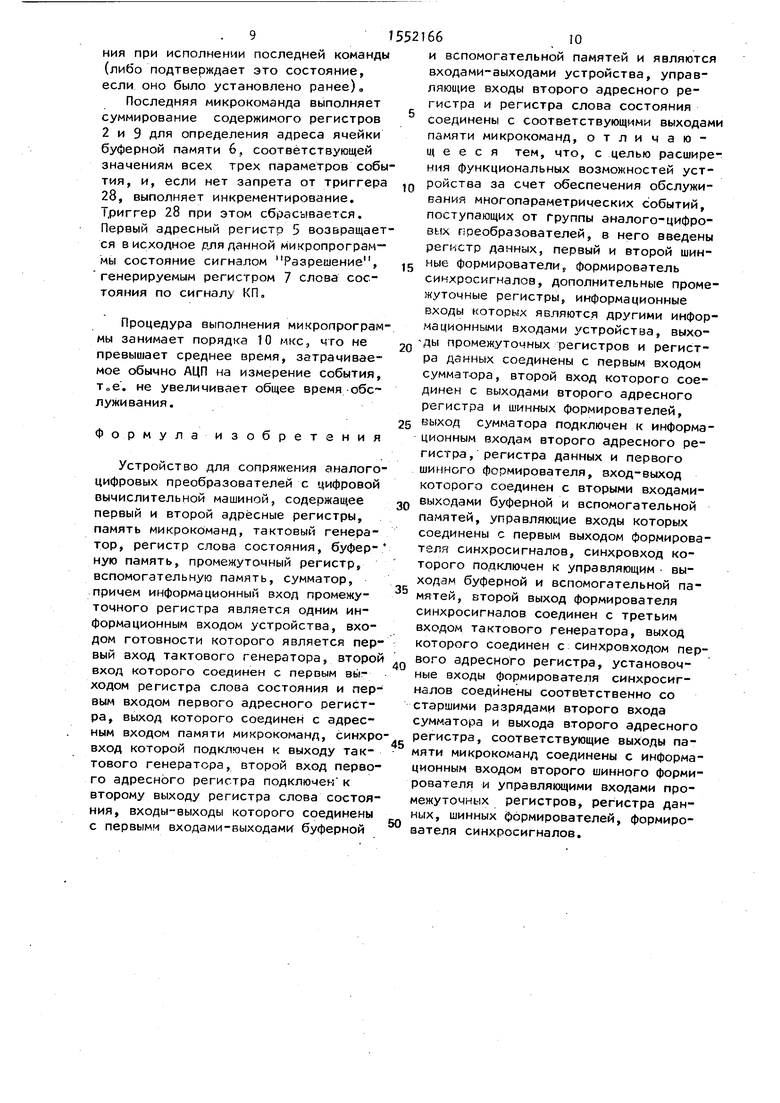

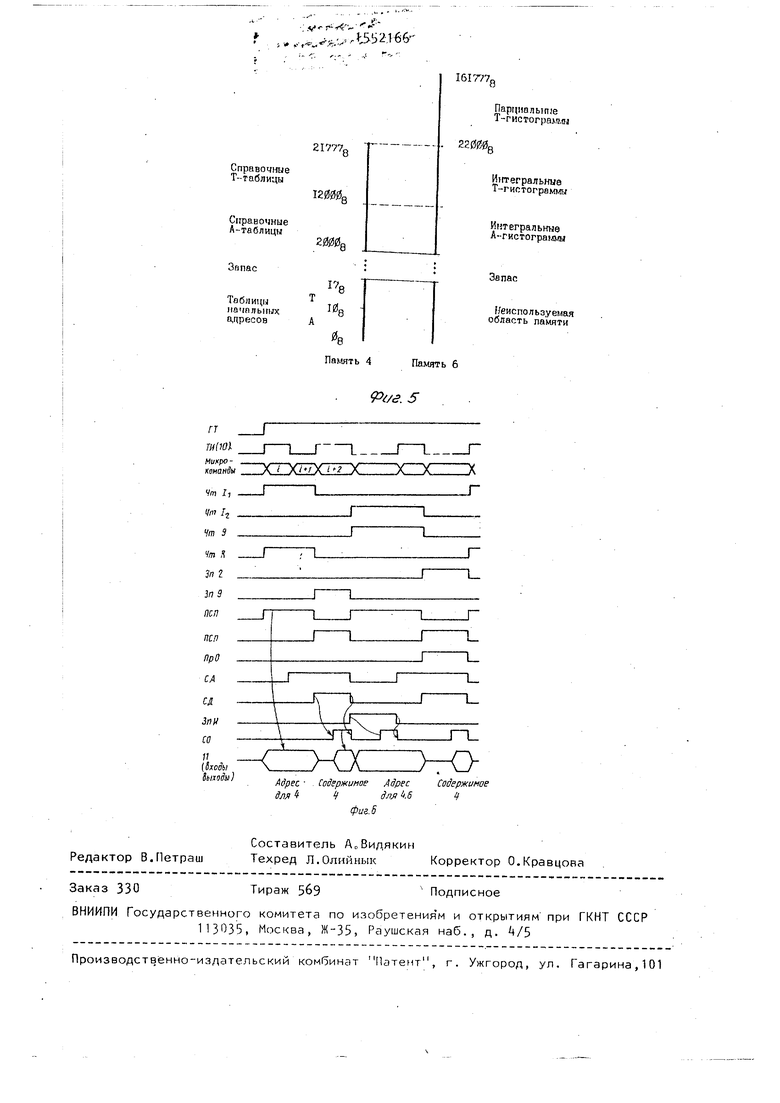

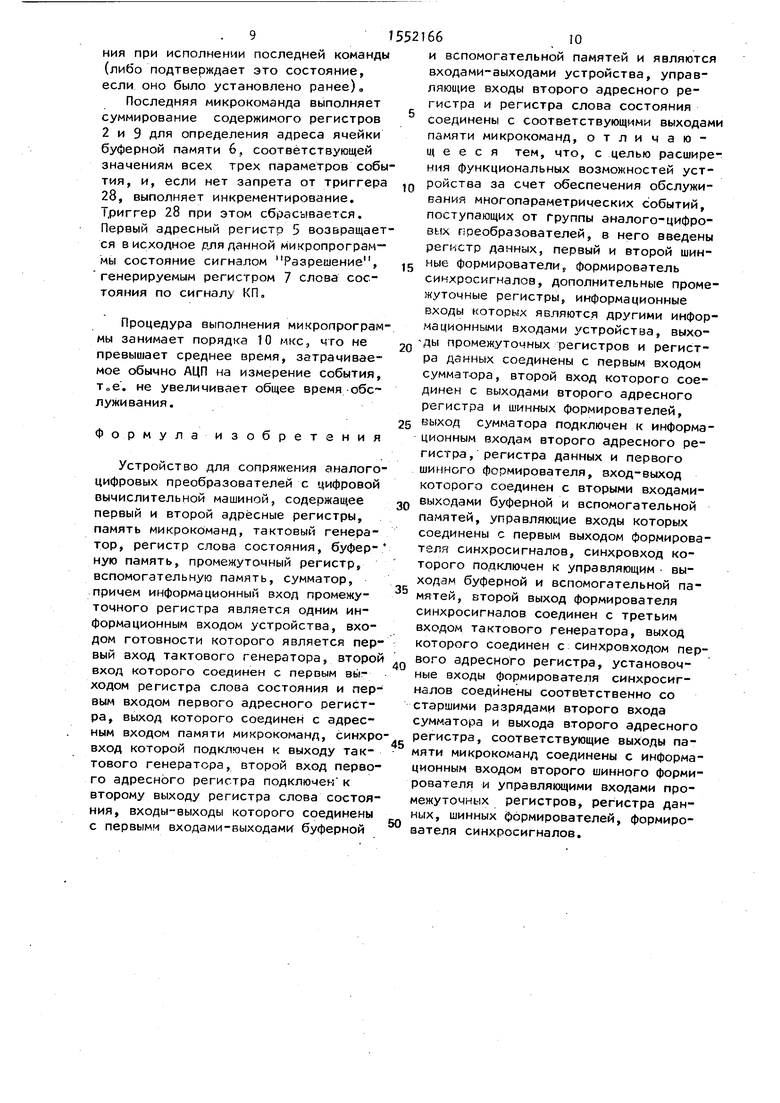

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема тактового генератора; на фиг. 3 - схема формирователя синхросигналов; на фиг. 4 - блок-схема алгоритма (а) и микропрограмма (б), реализуемые устройством,- на фиг„ 5 схема распределения вспомогательной и буферной памятей; на фиго 6 - временная диаграмма процедуры обращения к памятям.

Устройство (фиг. 1) содержит К про Нежуточных регистров Ц-1К регистр 2, данных, сумматор 3, вспомогательную память k, первый адресный регистр 5, буферную память 6, регистр 7 сло- Е)а состояния, память 8 микрокоманд, второй адресный регистр 9, тактовый Генератор 10, первый шинный формиро- фатель 11, второй шинный формирователь 12, формирователь 13 синхросигналов, К информационных входов 1, Е1ход 15 сигнала Готовность, выход 6 сигнала Разрешение, входы-выход 1 устройства.

Тактовый генератор 10 содержит (фиг. 2), триггер 18, вход установки И 1м которого служит первым входом генератора и соединен с входом 15 сигнала Готовность устройства, а йход установки в О служит входом разрешения генератора и соединен с первым выходом регистра 7 слова сос- Гояния, элемент И 19, первый вход которого соединен с выходом триггера 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, тран Зистор 21 типа КТ 315 конденсатор 22 и резисторы 23 и . Причем выход Элемента И 19 соединен со счетным входом регистра 5, а также с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 и через конденсатор 22 и транзистор 21 коллектор которого соединен с шиной 25 источника питания положительной полярности, с вторым входом элемента Ijl 19 и через регистор 2k с нулевой Шиной 26 источника питания, а через 0езистор 23 - с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, второй вход эле

5

0

5

0

5

0

5

0

5

мента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 служит управляющим входом тактового генератора 10 и соединен с вторым выходом формирователя 13 синхросигналов.

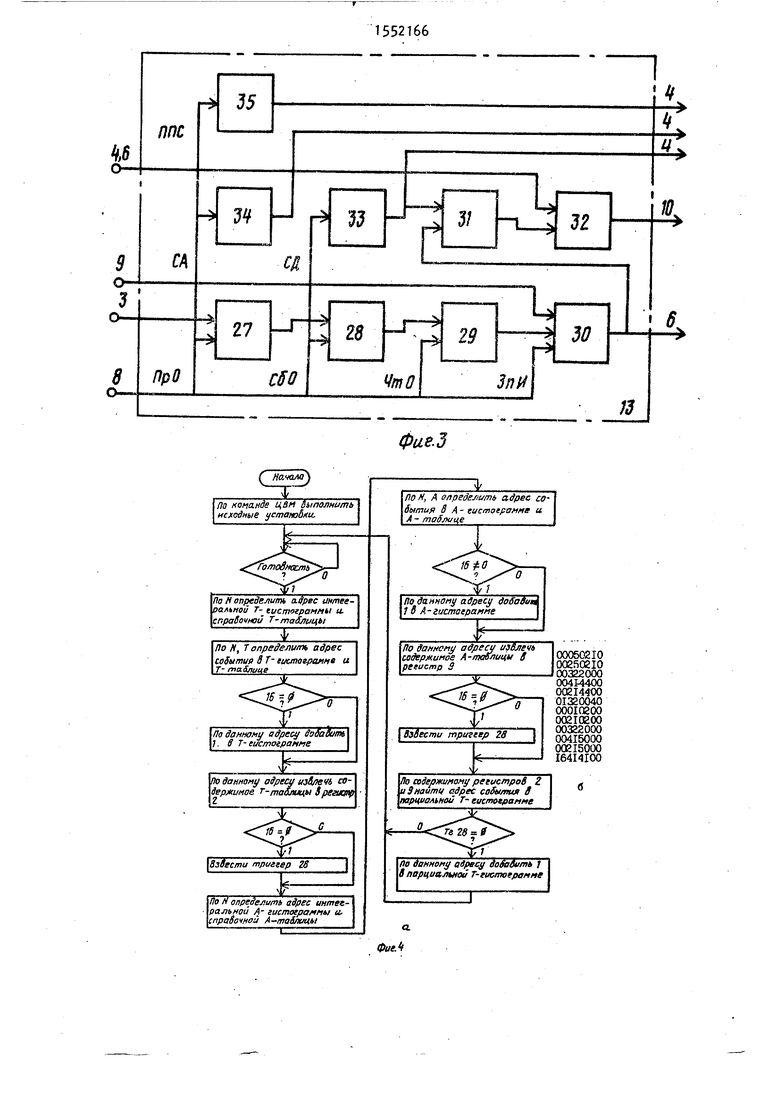

Формирователь 13 синхросигналов содержит (фиг. 3) последовательно соединенные элемент И 27, первый вход которого является первым установочным входом формирователя 13, триггер 28, элемент И-НЕ 29, элемент И 30, первый вход которого является вторым установочным входом формирователя, а выход - выходом сигнала ИНК первого выхода формирователя 13, элемент ИЛИ-НЕ 31, элемент ИЛИ 32, первый вход которого является синхровходом формирователя 13, а выход - его вторым выходом, повторитель 33, выход которого соединен с вторым входом элемента ИЛИ-НЕ 31 и является выходом сигнала Д первого выхода формирователя, повторитель 3, выход которого является выходом сигнала СА первого выхода формирователя 13, повторитель 35, выход которого является выходом сигнала Чт первого выхода формирователя. Вторые входы элемента 27, триг геоа 28, элементов 29 и 30 и входы повторителей 33 - 35 являются соответственно входами для сигналов ПрО, СбО, ЧтО, ЗпИ, СД, СА, ППС управляющего входа формирователя 13.

Промежуточный регистр 1 служит для приема и буферного хранения данных, поступающих от АЦП, и должен иметь три выходных состояния. Регистр 2 данных служит для буферного запоминания данных, поступающих с выхода сумматора 3 на его второй вход и также доляен иметь три выходных состояния.

Сумматор 3 служит для формирования и модификации адресов и данных. Разрядность сумматора определяется разрядностью адресной сетки (А) вспомогательной памяти Ц и буферной памяти 6„

Вспомогательная память k служит для хранения справочных таблиц, по которым ведется предобработка входящих событий. В качестве вспомогательной памяти должно использоваться запоминающее устройство с двумя портами ьходов-выходов и возможностью произвольной выборки данных для чтения и записи. Емкость справочной памяти опреде- ляет возможности предобработки устрой- :тва.Целесообразно использование совме5

ценной шины данных и адреса для вхо дов-выходов памятей.

Первый адресный регистр 5 служит для формирования адреса памяти 8 микрокоманд. В качестве этого регистра должен использоваться двоичный счетчик с предустановкой.

Буферная память 6 служит для накопления гистограмм (спектров распределения) значений параметров (совокупностей параметров) регистрируемых событий. К этой памяти предъявляются те же требования, что и к памяти k, но второй порт входов-выходов должен обеспечивать инкрементный режим регистрации данных.

Регистр 7 слова состояния служит для определения режима работы устройства и общего управления им.

Память 8 микрокоманд служит для хранения микропрограммы обработки входящих событий„ Так как набор программ для конкретного варианта устройства стабилен, в качестве памяти микрокоманд целесообразно использование устройства постоянного типа. Смена набора программ осуществляется заменой микросхем ЗУ.

Второй адресный регистр 9 служит для буферного запоминания формируемого адреса при обращении к вспомогательной и буферной памятям. Лппара турно за счет коммутации выхода это- го регистра и входа сумматора выполняется расширение адреса на Р Л - D + 1 разрядов, где D - разрядность слова ЦВМ (она определяет разрядность рабочих регистров 1, 2 и т.п.).

Тактовый генератор 10 служит для тактирования работы устройства, и при использовании памятей k и 6 асинхронного типа должен фазироваться с учетом состояния вспомогательной и буферной памятей.

Первый шинный формирователь 11 служит для организации двустороннего обмена информацией между сумматором и памятями 4 и 6, второй шинный формирователь 12 - для организации передачи разрядов Р расширения адреса из памяти микрокоманд в сумматор.

Формирователь 13 синхросигналов служит для выработки сигналов, синхронизирующих работу памятей и 6 с другими блоками устройства.

Устройство работает следующим образом.

521666

Из группы АЦП (не показаны) через входы Ik коды параметров зарегистрированного события поступают в промежуточные регистры 1 (для однозначнос- ° ти дальнейшего объяснения будем считать, что число этих регистров )° Если есть сигнал Разрешение от регистра 7 слова состояния (первона- IQ чально он вырабатывается по команде ЦВМ), то сигналом Готовность, поступающим с входа 15 устройства на тактовый генератор 10, запускается цикл исполнения микропрограммы пред- 15 обработки данного события, записанной в сегменте памяти 8 микрокоманд, саманном содержимым первого адресного регистра 5, куда оно переносится из регистра 7 через вход предустанов- 2Q -ки сигналом Разрешение. Для исполнения микропрограммы используются также данные из вспомогательной памяти 4„ Для записи данных из ЦВМ в память k и регистр 7 служат входы-вы- 25 ходы 17 устройства.

Цикл предобработки события реализуется последовательным исполнением функциональными блоками устройства микрокоманд, генерируемых памятью 8. -Q Возможный вариант организации памяти микрокоманд, формата слова микрокоманд, назначения разрядных выходов и функциональных блоков, куда соответствующие сигналы поступают по ииндивидуальным шинам, приведены 35 в таблице.

Для однозначности дальнейших пояснений положим, что разрядность адресной сетки вспомогательной 4 и буферной 6 памятей A-2Q, разрядность рабочих регистров , число разрядов расширения адреса-P A-D+1 5. Предположим, также, что первый шинный формирователь 11 связан с па- мятями 4 и 6 совмещенной шиной адреса и данных, хотя это не обязательно (при этом организация устройства проще) . «.

На фиг. k в качестве примера реализации предобработки устройством приведены алгоритм и микропрограмма для одной из задач. При регистрации в промежуточных регистрах 1, 1й и 1 событий, характеризуемых каждое- параметрами N, А и Т, которые могут

40

0

55

принимать значения в диапазонах соответственно N 1,2), А (1,2V) и Т (1,2W), формируются гистограммы значений параметров А и Т

71

для каждого N (интегральные А- и Т-гистограммы) и гистограммы значений Т для каждого значения N, соответствующих значениям параметра А, Попадающим в одно из М цифровых окон, указанных е справочных таблицах, за- Писанных во вспомогательной памяти 4 (парциальные Т-гистограммы). Если принять , то всего параллельно в результате предобработки должно быть Накоплено 16 интегральных и 0 парциальных гистограмм,, Распределение я:чеек памятей k и 6 для этой задачи Показано на фиг. 5 о

Рассмотрим последовательно выполнение микропрограммы, причем более подробно первые микрооперации, так Как последующие являются их модифицированным повторением. Первой микро Командой опрашивается промежуточный регистр 1( сигналом Чт,,, и его содержимое подается на первый вход Сумматора 3. Содержимое пяти младших разрядов ячейки памяти 8 микрокоманд Р1 - Р5 через второй шинный формирователь 12 передается сигналом ЧтР На второй вход сумматора (смещение На 10). Сумма через первый шинный формирователь 11 (сигналом ПСП) пе- ведается на вторые входы-выходы памятей 4 и 6. Отрицательным полуперио- Дом первого тактового импульса от Генератора 10 (фиг. 6) в памяти 8 формируется вторая микрокоманда, отличающаяся наличием сигнала СА. Этим Сигналом, сформированным повторителе 3 формирователя 13 синхросигналов, сумма воспринимается памятью k как некоторой ячейки.

Следующей микрокомандой в регистр 9 через первый шинный формирователь 11 (сигналами СА, СД, ППС и Зп 9, Сформированными в формирователе 13) Записывается содержимое ячейки памяти k с этим адресом. На это время сигналом с управляющего выхода памяти k, сформированным элементом ИЛИ 32 формирователя 13, блокируется тактовый генератор 10 для фазировки цикла памяти с работой остальных блоков устройства. Содержимое второго адресного регистра 9 является начальным Адресом интегральной Т-гистограммы и соответствующей справочной таблицы для значения N, взятого из регистра 1j|. Если предусмотрена регистрация Этой гистограммы, то в старшем (1б-м разряде должен быть 0, в противном

0

21

„ 5

5 ,„

40

45

668

случае 1. Значение содержимого определяется при составлении справочных таблиц.

Очередная микрокоманда служит для приформирования к начальному адресу содержимого промежуточного регистра 1 (сигналы Чт9, Чт12) и инкременти- рования ячейки памяти 6 с этим адресом, если предусмотрена регистрация данной интегральной Т-гистограммы (сигналы ПСП и ЗпИ), сформированной элементом И 30 при наличии разрешения от формирователя 11. На время цикла памяти блокируется тактовый генератор 10.

Следующие две микрокоманды используются для извлечения содержимого ячейки памяти l с тем же адресом (справочной таблицы, соответствующей интегральному Т-спектру) и его записи для временного хранения в регистр 2 данных (сигналом Зп2). Эта процедура используется устройством для модификации спектров в соответствии с определенным критерием, например для сжатия или сглаживания гистограмм, изменения системы координат, получения значений, являющихся некоторой функцией от измеренных значений параметра, выделения цифровых окон и т.п„ Признаком того, что значение параметра (в данном случае Т) удовлетворяет критерию, является 0 в старшем (1б-м) разряде слова, извлеченного из справочной таблицы (как и в случае регистрации интегральных гистограмм). Наличие 1 в этом разряде приводит к установлению (сигналом ПрО) триггера 28 формирователя 13 в. состояние, блокирующее инкре- ментирование памяти 6 последней микрокомандой цикла предобработки события.

Очередные три микрокоманды, аналогично первым, используются для записи в регистр 9 начального адреса ральной А-гистограммы для данного N, а следующая формирует адрес ячейки буферной памяти с учетом значений параметра А и, если задана процедура накопления интегральной А-гистограммы, выполняет инкременти- рование. Далее содержимое ячейки справочной памяти с тем же адресом переносится во второй адресный регистр и, если в его старшем разряде 1, то триггер 28 устанавливается в состояние блокировки инкрементирова. 91

ния при исполнении последней команды (либо подтверждает это состояние, если оно было установлено ранее).

Последняя микрокоманда выполняет суммирование содержимого регистров 2 и 9 для определения адреса ячейки буферной памяти 6, соответствующей значениям всех трех параметров события, и, если нет запрета от триггера 28, выполняет инкрементирование. Триггер 28 при этом сбрасывается. Первый адресный регисто 5 возвращается в исходное для данной микропрограммы состояние сигналом Разрешение, генерируемым регистром 7 слова состояния по сигнал «П.

Процедура выполнения микропрограммы занимает порядка 10 икс, ч го не превышает среднее время, затрачиваемое обычно АЦП на измерение события, т„е. не увеличивает общее время обслуживания.

Формула изобретения

Устройство для сопряжения аналого- цифровых преобразователей с цифровой вычислительной машиной, содержащее первый и второй адресные регистры, память микрокоманд, тактовый генератор, регистр слова состояния, буфер- ную память, промежуточный регистр, вспомогательную память, сумматор, причем информационный вход промежуточного регистра является одним информационным входом устройства, входом готовности которого является первый вход тактового генератора, второй вход которого соединен с первым выходом регистра слова состояния и первым входом первого адресного регистра, выход которого соединен с адресным входом памяти микрокоманд, синхро1 вход которой подключен к выходу тактового генератора, второй вход первого адресного регистра подключен к второму выходу регистра слова состояния, входы-выходы которого соединены с первыми входами-выходами буферной

5216610

и вспомогательной памятей и являются входами-выходами устройства, управляющие входы второго адресного регистра и регистра слова состояния соединены с соответствующими выходами памяти микрокоманд, отличающееся тем, что, с целью расширения функциональных возможностей уст10 ройства за счет обеспечения обслуживания многопараметрических событий, поступающих от группы аналого-цифровых преобразователей, в него введены регистр данных, первый и второй шин15 ные формирователиг формирователь

синхросигналов, дополнительные промежуточные регистры, информационные входы которых являются другими информационными входами устройства, выхо20 -ды промежуточных регистров и регистра данных соединены с первым входом сумматора, второй вход которого соединен с выходами второго адресного регистра и шинных формирователей,

25 выход сумматора подключен к информационным входам второго адресного регистра, регистра данных и первого шинного формирователя, вход-выход которого соединен с вторыми входами30 выходами буферной и вспомогательной памятей, управляющие входы которых соединены с первым выходом формирователя синхросигналов, синхровход которого подключен к управляющим выходам буферной и вспомогательной памятей, второй выход формирователя синхросигналов соединен с третьим входом тактового генератора, выход которого соединен с синхровходом пер0 вого адресного регистра, установочные входы формирователя синхросигналов соединены соответственно со старшими разрядами второго входа сумматора и выхода второго адресного регистра, соответствующие выходы памяти микрокоманд соединены с информационным входом второго шинного формирователя и управляющими входами промежуточных регистров, регистра данных, шинных формирователей, формиро35

5

0

вателя синхросигналов.

Фиг. 2.

По копанье ЦВМ Выполнить исходные устанобхи.

Па Н определит иврвс м/пее- ральной Т еистяграммы а. справочной Т-та&пицы

По И, Т определить адрес

8 Т- еислюграннв и Т- таблице

Па ванному адресу Набаоить J. в Т- еистагранне

По ванному aipecy изЙ/№ /1 содержимое т-та§мзцы S регистр

8з0ести триггер Z8

По К определить aipec интее- ральной А- гисгтярарты а, справочной А та6лицы

фие.З

По N, А определить адрес события вА- гистограмме а А - таблице

По дан нону адресу добавин 1 д А-гиаяоеранне

адресу извлечь -таблицы о

иггер 28

000502JO 00250210 00322000 004И400 00214400 01320040 00010200 00210200 00322000 00415000 00215000 I64I4IOO

По иЗержиному регистров Z и 3 найти адрес события 8 парциальной Т- еистогранне

По ванному аврвсу добавить 1 S парциальной Т-гислюерапне

21777,

8

Справочные Т- таблицы

I2000Q

Справочные А-таблицм

2000Д

Запас

178

10е

% Память 4

Адрес Содержимое Адрес для ЬЧдляЬ5

фиг. 5

Редактор В.Петраш

Составитель АоВидякин

Техред Л.Олийнык Корректор О.Кравцова

Заказ 330

Тираж 5б9

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР , Москва, Ж-35, Раушская наб., д. А/5

161777,

8

Парцналыше J-гистогралшы

220008

Интегральные Т-гимограммы

Интегральные А- гистогра лмы

Запас

Неиспользуемая область памяти

Память 6

. 5

ЬО

Содержите

Ч

Подписное

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения аналого-цифрового преобразователя с цифровой вычислительной машиной | 1983 |

|

SU1179308A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-12—Подача