Изобретение относится к цифровой вычислительной технике, может быть использовано при отладке программ специализированных ЦВМ, содержащих в составе штатные блоки постоянной памяти с рабочими программами, и является усовершенствованием устройства по авт.св. № 1198525.

Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативной подмены нескольких зон информации постоянной памяти соответствующими зонами информации оперативной памяти.

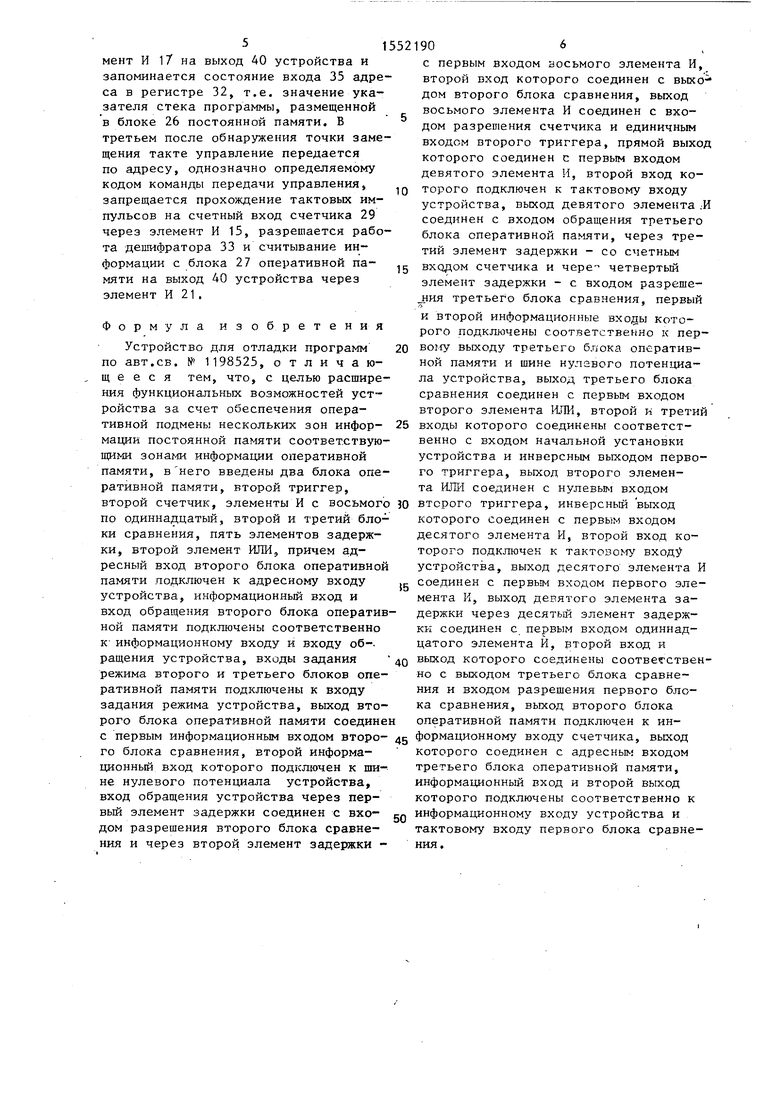

На чертеже представлена схема устройства.

Устройство содержит блоки 1 и 2 оперативной памяти, блоки 3-5 сравнения, элементы 6-10 задержки, элементы И 11-21, триггерь 22 и 23, элементы ИЛИ 24 и 25, блок 26 постоянной памяти, блок 27 оперативной памяти, счетчики 28 и 29, дешифратор 30, регистры 31 и 32, дешифратор 33, вход 34 обращения устройства, адресный вход 35 устройства, информационный вход 36 устройства, тактовый вход 37 устройства, вход 38 начальной установки устройства, вход 39 установки режима устройства, выход 40 устройства.

Устройство работает следующим образом.

В исходном состоянии, в которое устройство устанавливается при подаче на вход Сброс 38 сигнала начальной установки, разрешается считывание информации только с блока 26 постоянной памяти через элемент И 20 в момент появления тактовых импульСП

1

со

14)

сов, поступающих на вход 37 тактовых импульсов о Поэтому на выход 40 устро ,ства выдается информация, размещен ная в блоке 26 постоянной памяти. В момент появления сигнала Обращение на входе 34 обращения устройства осуществляется выборка из блока 1 оперативной памяти числа, соответствующего k младшим разрядам адреса, подаваемого на адресный вход 35 устройства. Сигнал Обращение через вре- мя, равное времени выборки инфор ма- ции из блока 1 оперативной памяти,, 1 что обеспечивается элементом 6 задержки, поступает на тактовый вход блока 3 сравнения.

В случае считывания нулевого числ из блока 1 оперативной памяти, которое интерпретируется как отсутствие необходимости подмены зон информации блока 26 постоянной памяти для всех адресов с указанным значением k младших разрядов, срабатывает блок 3 сравнения и запрещает установку в °1 триггера 22. Таким образом, считывание информации ведется по-прежнему с блока 26 постоянной памяти на выход 40 устройства.

В случае считывания числа,, отличного от нуля, из блока 1 оперативной

адрес подсписка адресов точек замещения и соответствующих им команд перехода, расположенного в блоке 2 оперативной памяти, блок 3 сравнения разрешает прохождение через элемент И 11 сигнала Обращение, задержанного на время срабатывания блока 3 сранения. С Йыхода элемента И 11 сигнал Обращение разрешает запись числа, считанного с блока 1 оперативной памяти, на счетчик 28 и устанавливает в состояние 1 триггер 22. Последний переключает Прохождение тактовых импульсов устройства таким образом, что по приходе каждого тактового импульса осуществляется выборка информации из блока 2 оперативной памяти, через время считывания информации из блока 2 оперативной памяти, что обеспечивается элементами 8 и 9 задержки соответственно, инкремент содержимого счетчика 28 и тактирова- ние блока 4 сравнения.

В случае считывания с первого вы-

хода блока 2 оперативной памяти нулевой команды перехода, что интерпре- THPVPTCH как конец подсписка адресов

0

5

0

5

0

5

0

0

5

точек замещения и соответствующих им команд перехода, срабатывает блок 4 сравнения и запрещает тактирование блока 5 сравнения, а также через элемент ИЛИ 24 устанавливает триггер 22 в состояние О. Таким образом, считывание информации ведется по-прежнему с блока 26 постоянной памяти на выход 40 устройства. В случае ы- вания команды перехода, отличной от нуля, с первого выхода блока 2 оперативной памяти число, считываемое с второго выхода блока 2 оперативной памяти, интерпретируется как полный адрес точки замещения зсны информации из блока 26 постоянной памяти. В этом случае блок 4 сравнения разрешает тактирование блока 5 сравнения.

При совпадении полного адреса, подаваемого на вход 35 адреса устройства с числом, считанным с второго выхода блока 2 оперативной памяти, блок 5 сравнения формирует на выходе сигнал, который через элемент И 16 устанавливает в 1 триггер 23. Поэтому запрещается считывание информации с блока 2э постоянной памяти, прохождение сиг зала с выхода блока 5 сравнения черэз элемент И 16, разрешается работа счгтчика 29 и устанавливается в О триггер 22, который запрещает прохождение тактовых импульсов с входа 37 тактовых импульсов устройства на выход элемента И 12 и разрешает прохождение тактовых импульсов на выход элемента И 13, При поступлении на вход 37 тактовых импульсов первого, после срабатывания блока 5 сравнения, тактового импульса разрешается прохождение кода команды передачи управления чергз элемент И 17 с первого выхода блэка 2 оперативной памяти на выход 40 устройства и запоминается состояние адресного входа 35 устройства в регистре 31. Следовательно, вместо очередной команды программы, размещенной в блоке 26 постоянной памяти, на выход 40 устройства выдается команда передачи управления и в регистре 31 запоминается адрес точки замещения.

По команде передачи управления в следующем такте содержимое счетчика команд загружается в стек. В этом такте, втором после обнаружения точки замещения, запрещается прохождение кода передачи управления через эле51552

мент И 1/ на выход 40 устройства и запоминается состояние входа 35 адреса в регистре 32, т.е. значение указателя стека программы, размещенной в блоке 26 постоянной памяти. В третьем после обнаружения точки замещения такте управление передается по адресу, однозначно определяемому

кодом команды передачи управления,

запрещается прохождение тактовых импульсов на счетный вход счетчика 29 через элемент И 15, разрешается работа дешифратора 33 и считывание информации с блока 27 оперативной па- мяти на выход 40 устройства через элемент И 21.

Формула изобретения

Устройство для отладки программ по авт.св. № 1198525, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения оперативной подмены нескольких зон инфор- мации постоянной памяти соответствующими зонами информации оперативной памяти, в него введены два блока оперативной памяти, второй триггер, второй счетчик, элементы И с восьмого по одиннадцатый, второй и третий блоки сравнения, пять элементов задержки, второй элемент ИЛИ, причем адресный вход второго блока оперативной

памяти подключен к адресному входу

15

устройства, информационный вход и вход обращения второго блока оперативной памяти подключены соответственно к информационному входу и входу об-. ращения устройства, входы задания 40 режима второго и третьего блоков оперативной памяти подключены к входу задания режима устройства, выход второго блока оперативной памяти соединен с первым информационным входом второ- 45 го блока сравнения, второй информационный вход которого подключен к шине нулевого потенциала устройства, вход обращения устройства через первый элемент задержки соединен с вхо- gn дом разрешения второго блока сравнения и через второй элемент задержки

0

0 5 ю

15

0 5 n

1906

с первым входом восьмого элемента И, второй вход которого соединен с выходом второго блока сравнения, выход восьмого элемента И соединен с входом разрешения счетчика и единичным входом второго триггера, прямой выход которого соединен с первым входом девятого элемента И, второй вход которого подключен к тактовому входу устройства, выход девятого элемента .И соединен с входом обращения третьего блока оперативной памяти, через третий элемент задержки - со счетным входом счетчика и чере четвертый элемент задержки - с входом разреше ния третьего блока сравнения, первый

/

и второй информационные входы которого подключены соответственно к пер- воггу выходу третьего б.пока оперативной памяти и шине нулевого потенциала устройства, выход третьего блока сравнения соединен с первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с входом начальной установки устройства и инверсным выходом первого триггера, выход второго элемента ИЛИ соединен с нулевым входом второго триггера, инверсный выход которого соединен с первым входом десятого элемента И, второй вход которого подключен к тактовому входу устройства, выход десятого элемента И соединен с первым входом первого элемента К, выход девятого элемента задержки через десятый элемент задержки соединен с первым входом одиннадцатого элемента И, второй вход и выход которого соединены соответственно с выходом третьего блока сравнения и входом разрешения первого блока сравнения, выход второго блока оперативной памяти подключен к информационному входу счетчика, выход которого соединен с адресным входом третьего блока оперативной памяти, информационный вход и второй выход которого подключены соответственно к информационному входу устройства и тактовому входу первого блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1989 |

|

SU1683019A2 |

| Устройство для отладки программ | 1983 |

|

SU1198525A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Запоминающее устройство | 1977 |

|

SU691925A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

Изобретение относится к цифровой вычислительной технике, может быть использовано при отладке программ специализированных ЦВМ, содержащих в своем составе штатные блоки постоянной памяти с рабочими программами, и является усовершенствованием изобретения по а.с. N 1198525. Устройство решает задачу оперативной подмены зон информации, расположенных в блоке постоянной памяти, информацией, расположенной в блоке оперативной памяти. Цель - расширение функциональных возможностей. Устройство содержит первый-третий блоки оперативной памяти, блок постоянной памяти, первый-третий блоки сравнения, первый-пятый элементы задержки, первый-одиннадцатый элементы И, триггер, P-триггер, первый и второй элементы ИЛИ, два счетчика, первый и второй дешифраторы, первый и второй регистры. 1 ил.

| Устройство для отладки программ | 1983 |

|

SU1198525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-23—Публикация

1988-08-01—Подача