О 00 Ы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1552190A2 |

| Устройство для отладки программ | 1983 |

|

SU1198525A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для управления памятью | 1979 |

|

SU943726A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1411755A2 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программ | 1983 |

|

SU1137472A1 |

| Устройство для отладки программ | 1986 |

|

SU1383372A1 |

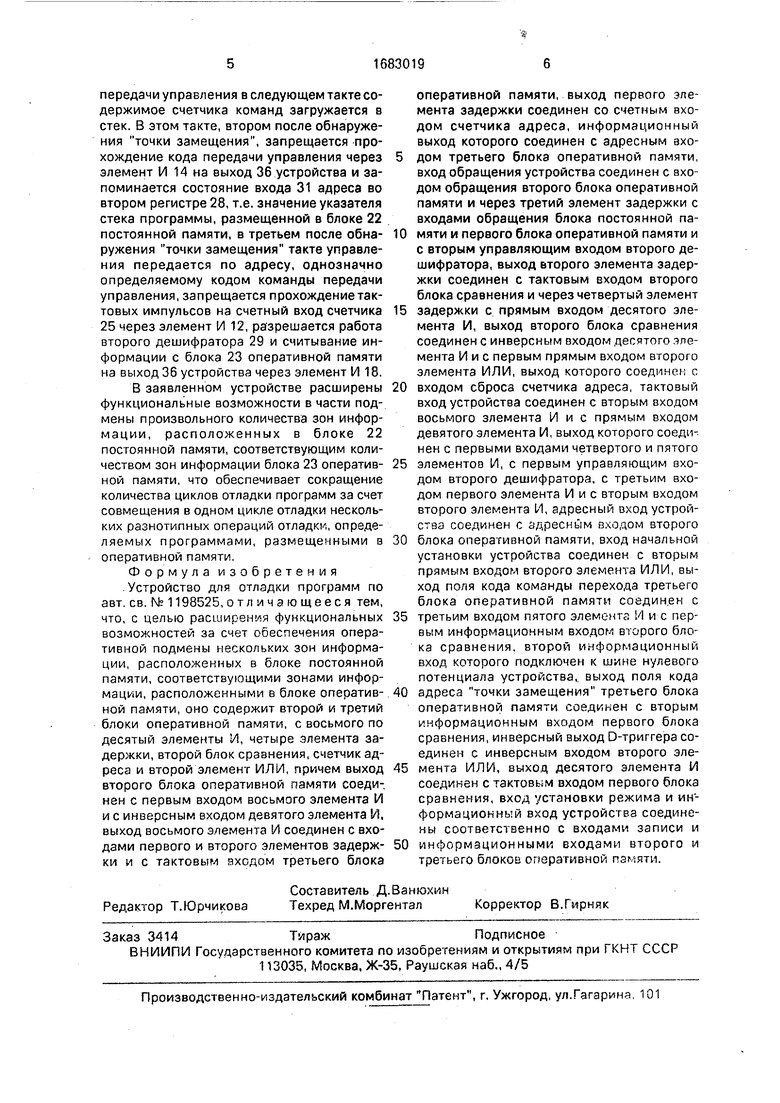

Изобретение относится к цифровой вычислительной технике и может быть использовано при отладке программ специализированных ЦВМ, содержащих в своем J/ составе штатные блоки постоянной памяти с рабочими программами. Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативной подмены нескольких зон информации, расположенных в блоке постоянной памяти, информацией, расположенной в блоке оперативной памяти. Устройство для отладки программ содержит три блока оперативной памяти 1, 2, 23, блок 22 постоянной памяти, блоки 3, 4 сравнения, элементы 5 - 8 задержки, элементы И 9-18, D-триггер 19, элементы ИЛИ 20, 21, счетчик 24 адреса, двухразрядный двоичный счетчик 25, первый 26 и второй 29 дешифраторы, первый27 и второй 28 регистры. 1 ил.

ю

ю

Изобретение относится к цифровой вычислительной технике, может быть использовано при отладке программ специаизированных ЦВМ, содержащих в своем оставе штатные блоки постоянной памяти рабочими программами, и является усовершенствованием устройства по авт. св. № 1198525.

Целью изобретения является расширеие функциональных возможностей устройтва за счет обеспечения оперативной подмены нескольких зон информации, расположенных в блоке постоянной памяти, сответствующими зонами информации, расположенными в блоке оперативной памяти.

На чертеже представлен пример реалиации устройства, где изображены второй блок 1 оперативной памяти, третий блок 2 оперативной памяти, второй и первый блоки 3 и 4 сравнения, элементы 5-8 задержки, элементы И 9 - 18, D-триггер 19, элементы ИЛИ 20 и 21, блок 22 постоянной памяти, первый блок 23 оперативной памяти, счетчик 24 адреса, двухразрядный двоичный счетчик 25, первый дешифратор 26, первый регистр 27, второй регистр 28, второй дешифратор 29, вход 30 обращения устройства, адресный вход 31 устройства, информационный вход 32 устройства, тактовый вход 33 устройства, вход 34 начальной установки устройства, вход 35 установки режима устройства, выход 36 устройства.

Устройство работает следующим образом.

В исходном состоянии, в которое устройство устанавливается при подаче на вход 34 сигнала начальной установки, разрешается считывание информации только с блока 22 постоянной памяти через элемент И 17 в момент появления тактовых импульсов, поступающих на вход 33 тактовых импульсов, поэтому на выход 36 устройства выдается информация, размещенная в блоке 22 постоянной памяти. В момент появления сигнала на входе 30 обращения устройства осуществляется выборка из блока 1 оперативной памяти бита, соответствующего к младшим разрядам адреса, подаваемого на адресный вход 31 устройства. В случае считывания нулевого бита из блока 1 оперативной памяти, который интерпретируется как отсутствие необходимости подмены зон информации блока 22 постоянной памяти для всех адресов с указанным значением k младших разрядов, прохождение тактовых импульсов запрещается через элемент И 9 и разрешается через элемент И 10. Таким образом, считывание информации ведется по-прежнему с блока

22 постоянной памяти на выход 36 устройства. В случае считывания бита, отличного от нуля, из блока 1 оперативной памяти, который интерпретируется как наличие адресов с указанными k младшими разрядами в списке адресов точек замещения и соответствующих им команд перехода, расположенном в блоке 2 оперативной памяти, запрещается прохождение тактовых им0 пульсов через элемент И 10 и разрешается через элемент И 9, Таким образом, по приходе каждого тактового импульса осуществляются выборка информации из блока 2 оперативной памяти через время считыва5 ния информации из блока 2 оперативной памяти, что обеспечивается элементами 5, 7 задержки, инкремент содержимого счетчика 24 адреса и тактирование блока 3 сравнения. В случае считывания с первого выхода

0 блока 2 оперативной памяти нулевой команды перехода, что интерпретируется как конец списка адресов точек замещения и соответствующих им команд перехода, срабатывает блок 3 сравнения и запрещает так5 тирование блока 4 сравнения, таким образом, считывание информации по-прежнему ведется с блока 22 постоянной памяти на выход 36 устройства, В случае считывания команды перехода, отличной от нуля, с

0 первого выхода блока 2 оперативной памяти число, считываемое с второго выхода блока 2 оперативной памяти, интерпретируется как полный адрес точки замещения зоны информации из блока 22 постоянной памя5 ти, в этом случае блок 3 сравнения разрешает тактирование блока 4 сравнения. При совпадении полного адреса, подаваемого на вход 31 устройства, с числом с второго выхода блока 2 оперативной памяти блок 4

0 сравнения формирует на выходе сигнал, который через элемент И 13 устанавливает в 1 D-триггер 19, поэтому запрещается считывание информации с блока 22 постоянной памяти, прохождение сигнала с выхода

5 блока 4 сравнения через элемент И 13, разрешается работа счетчика 25. При поступлении на вход 33 тактовых импульсов первого после срабатывания блока 4 сравнения тактового импульса разрешается

0 прохождение кода команды передачи управления через элемент И 14 с первого выхода блока 2 оперативной памяти на выход 36 устройства и запоминается состояние адресного входа 31 устройства на первом

5 регистре 27. Следовательно, вместо очередной команды программы, размещенной в блоке 22 постоянной памяти, на выход 36 устройства выдается команда передачи управления и в первом регистре 27 запоминается адрес точки замещения. По команде

передачи управления в следующем такте содержимое счетчика команд загружается в стек. В этом такте, втором после обнаружения точки замещения, запрещается прохождение кода передачи управления через элемент И 14 на выход 36 устройства и запоминается состояние входа 31 адреса во втором регистре 28, т.е. значение указателя стека программы, размещенной в блоке 22 постоянной памяти, в третьем после обнаружения точки замещения такте управления передается по адресу, однозначно определяемому кодом команды передачи управления, запрещается прохождение тактовых импульсов на счетный вход счетчика 25 через элемент И 12, разрешается работа второго дешифратора 29 и считывание информации с блока 23 оперативной памяти на выход 36 устройства через элемент И 18, В заявленном устройстве расширены функциональные возможности в части подмены произвольного количества зон информации, расположенных в блоке 22 постоянной памяти, соответствующим количеством зон информации блока 23 оперативной памяти, что обеспечивает сокращение количества циклов отладки программ за счет совмещения в одном цикле отладки нескольких разнотипных операций отладки, определяемых программами, размещенными в оперативной памяти.

Формула изобретения Устройство для отладки программ по авт. св. М 1198525, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения оперативной подмены нескольких зон информации, расположенных в блоке постоянной памяти, соответствующими зонами информации, расположенными в блоке оперативной памяти, оно содержит второй и третий блоки оперативной памяти, с восьмого по десятый элементы И, четыре элемента задержки, второй блок сравнения, счетчик адреса и второй элемент ИЛИ, причем выход второго блока оперативной памяти соединен с первым входом восьмого элемента И и с инверсным входом девятого элемента И, выход восьмого элемента И соединен с входами первого и второго элементов задержки и с тактовым яходом третьего блока

оперативной памяти, выход первого элемента задержки соединен со счетным входом счетчика адреса, информационный выход которого соединен с адресным зхо- 5 дом третьего блока оперативной памяти, вход обращения устройства соединен с входом обращения второго блока оперативной памяти и через третий элемент задержки с входами обращения блока постоянной па0 мяти и первого блока оперативной памяти и с вторым управляющим входом второго дешифратора, выход второго элемента задержки соединен с тактовым входом второго блока сравнения и через четверт ый элемент

5 задержки с прямым входом десятого элемента И, выход второго блока сравнения соединен с инверсным входом десятого элемента И и с первым прямым входом второго элемента ИЛИ, выход которого соединен с

0 входом сброса счетчика адреса, тактовый вход устройства соединен с вторым входом восьмого элемента И и с прямым входом девятого элемента И, выход которого соединен с первыми входами четвертого и пятого

5 элементов И, с первым управляющим входом второго дешифратора, с третьим входом первого элемента И и с вторым входом второго элемента И, адресный вход устройства соединен с адресным входом второго

0 блока оперативной памяти, вход начальной установки устройства соединен с вторым прямым входом второго элемента ИЛИ, выход поля кода команды перехода третьего блока оперативной памяти соединен с

5 третьим входом пятого элемента И и с первым информационным входом второго блока сравнения, второй информационный вход которого подключен к шине нулевого потенциала устройства, выход поля кода

0 адреса точки замещения третьего блока оперативной памяти соединен с вторым информационным входом первого блока сравнения, инверсный выход D-триггера соединен с инверсным входом второго эле5 мента ИЛИ, выход десятого элемента И соединен с тактовь;м входом первого блока сравнения, вход установки режима и информационный вход устройства соединены соответственно с входами записи и

0 информационными входами второго и третьего блоков оперативной памяти.

| Устройство для отладки программ | 1983 |

|

SU1198525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1989-10-16—Подача